摩尔定律,虽命名为“定律”,但究其本质更像是一条预言,一条在过去的 50 年间始终引导半导体行业发展的伟大预言。但是,现阶段摩尔定律下工艺的无限制成长终会遭遇一道名为“物理极限”的壁垒,如何绕过壁垒以延续乃至超越摩尔定律成为了现如今业界的发展重心。

如果说系统级芯片(System on Chip,英文简称 SoC)技术是摩尔定律不断发展所产生的重要产物,那么系统级封装(System in Package,英文简称 SiP)技术便是实现超越摩尔定律的关键路径。在“后摩尔定律”所提供的关键助力之下,SiP 生态系统正持续成长以缓解因晶体管尺寸日趋物理极限产生的压力。

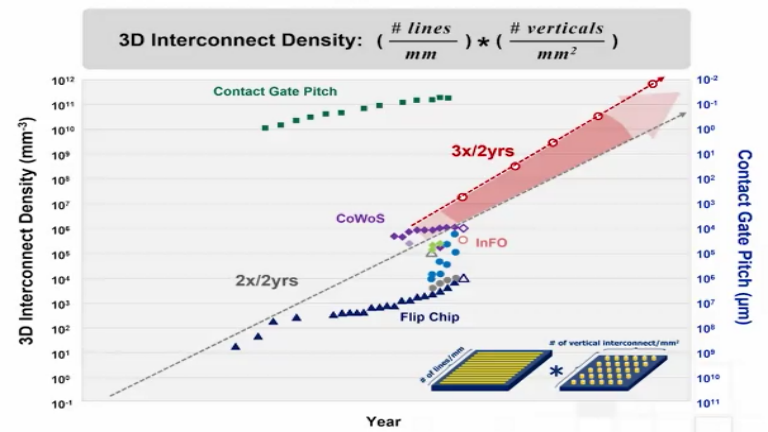

(图片来源:TSMC) 随着 5G 通信及机器学习技术应用的快速普及,系统级封装 SiP 技术在短短的时间内便已经成为实现微系统功能多样化、集成异构化、体积及成本最小化的最优方案。

对于 SiP 技术的生态系统,除了业内人士非常熟悉的半导体材料和计算机辅助设计(CAD)软件之外,IC 基板技术及与之关联的供应链同样是 SiP 生态系统的重要一环。上图所示为当前半导体封测行业中常见的基板技术及其趋势。 目前从技术发展的趋势来看,双面塑模成型技术、电磁干扰屏蔽技术、激光辅助键合技术可以并称为拉动系统级封装技术发展的“三驾创新马车”。NO.1双面塑模成型技术双面塑模成型技术(Double-Sided Molding Technology)之所以成为系统级封装工程专家的新宠,主要有两个原因: (一)有效减少封装体积以节省空间。 (二)有效缩短多个裸芯(Bare Dies)及被动元件之间的连接线路以降低系统阻抗、提升整体电气性能。 更小的封装体积、更强的电气性能,为双面塑模成型技术在 SiP 领域的广泛应用前景提供了良好的基础。下图所示为一例由长电科技成功导入规模量产的双面塑模成型 SiP 射频前端模块产品。

长电科技的双面封装 SiP 产品采用了多项先进工艺以确保双面塑模成型技术的成功应用。该产品采用了 C-mold 工艺,实现了芯片底部空间的完整填充,并有效减少了封装后的残留应力, 保证了封装的可靠性。

同时 Grinding 工艺的应用,使封装厚度有了较大范围的选择,同步实现精准控制产品的厚度公差。为了去除流程中残留的多余塑封料,长电科技还采用了 Laser ablation 工艺,以确保产品拥有更好的可焊性。

这项技术看似稀松平常,实则机关暗藏,每一项创新技术的成功落地都要经历许多挑战。双面塑模成型(Double-Sided Molding Technology)技术的落地主要面临着以下三大挑战: (一)塑模成型过程中的翘曲问题。 (二)背面精磨(Back Grinding)过程中的管控风险。 (三)激光灼刻(Laser Ablating)及锡球成型(Solder Ball Making)中的管控风险。 面对全新工艺所带来的诸多挑战,长电科技选择直面困难,攻克一系列技术难题,并成功于 2020 年 4 月通过全球行业领先客户的认证,实现了双面封装 SiP 产品的量产。 在这项全新突破的工艺中,长电科技严格把控生产流程,采用高度自动化的先进制程,将在双面塑模成型过程可能发生的各类风险隐患进行了有效降低。

原文标题:详解 SiP 技术体系中的三驾创新马车(一)

文章出处:【微信公众号:长电科技】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

半导体

+关注

关注

334文章

26931浏览量

215426 -

SiP

+关注

关注

5文章

496浏览量

105235 -

长电科技

+关注

关注

5文章

348浏览量

32472

原文标题:详解 SiP 技术体系中的三驾创新马车(一)

文章出处:【微信号:gh_0837f8870e15,微信公众号:长电科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

达林顿晶体管概述和作用

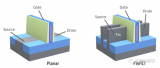

CMOS晶体管的尺寸规则

NMOS晶体管和PMOS晶体管的区别

CMOS晶体管和MOSFET晶体管的区别

PNP晶体管符号和结构 晶体管测试仪电路图

降压开关稳压器如何使用串联晶体管

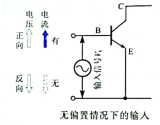

晶体管放大时,各级电位状态是什么

什么是达林顿晶体管?达林顿晶体管的基本电路

晶体管计算机的主要物理元件为

有什么方法可以提高晶体管的开关速度呢?

晶体管是怎么做得越来越小的?

SiP正持续成长以缓解因晶体管尺寸日趋物理极限的压力

SiP正持续成长以缓解因晶体管尺寸日趋物理极限的压力

评论