作者:zgezi

一、SoC设计的特点

一个完整的SoC设计包括系统结构设计(也称为架构设计),软件结构设计和ASIC设计(硬件设计)。

SoC设计与传统的ASIC设计最大的不同在于以下两方面:

SoC设计更需要了解整个系统的应用,定义出合理的芯片架构,使得软硬件配合达到系统最佳工作状态。因而,软硬件协同设计被越来越多地采用。

SoC设计是以IP复用或更大的平台复用为基础的。因而,基于IP 复用的设计是硬件实现的特点。

二、软硬件协同设计流程

SoC(System on Chip)通常被称作系统及芯片或者片上系统,作为一个完整的系统,其包含了硬件和软件两部分内容。这里硬件指SoC芯片部分,软件指运行在SoC芯片上的系统及应用程序。所在在进行设计时需要同时从软件和硬件的角度去考虑。

传统的设计中,设计工程师很难对结构在系统层次上进行详细评估,随着设计的细节化,要改变系统架构变得更加困难。此外,由于仿真速度的限制,软件开发难以在这种详细的硬件平台上进行,所以采用传统的设计流程进行SoC设计可能会存在产品设计周期长,芯片设计完成后发现系统架构存在问题等。

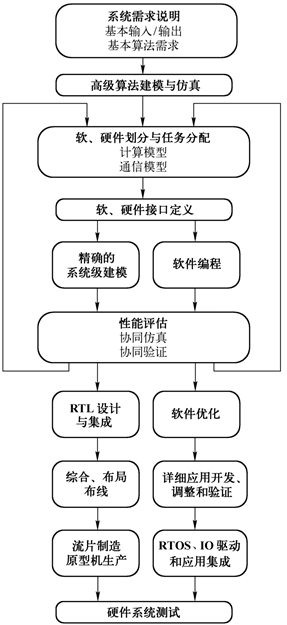

软硬件协同设计指的是软硬件的设计同步进行,如下图所示,在系统定义的初始阶段两者就紧密相连,近年来,由于电子系统级设计(ESL Electronic System Leverl Design)工具的发展,软硬件协同设计逐渐被采用。这种方法使得软件设计者在硬件设计完成之前就可以获得软件开发的虚拟硬件平台,在虚拟平台上开发应用软件,评估系统架构设计。

2.1 系统需求说明

系统设计首先从确定所需的功能开始,包含系统基本输入和输出及基本算法需求,以及系统要求的功能、性能、功耗、成本和开发时间等。在这一阶段,通常会将用户的需求转换为用于设计的技术文档,并初步确定系统的设计流程。

2.2 高级算法建模与仿真

设计者将使用如C和C++等高级语言创建整个系统的高级算法模型和仿真模型。目前,一些EDA工具可以帮助我们完成这一步骤。有了高级算法模型,便可以得到软硬件协同仿真所需的可执行的说明文档。此类文档会随着设计进程的深入而不断地完善和细化。

2.3 软硬件划分过程

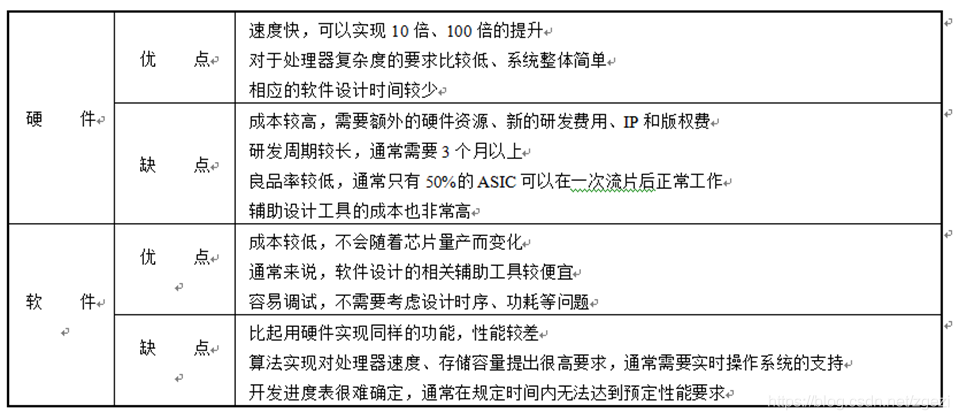

设计者通过软硬件划分来决定哪些功能应该由硬件完成,哪些功能应该由软件来实现。这是一个需要反复评估-修改直至满足系统需求的过程。

2.4 软硬件同步设计

由于软硬件的分工已明确,芯片的架构及同软件的接口也已定义,接下来便可以进行软硬件的同步设计了。其中硬件设计包括RTL设计和集成、综合、布局布线及最后的流片。软件设计则包括算法优化、应用开发,以及操作系统、接口驱动和应用软件的开发。

三、基于标准单元的SoC芯片设计流程

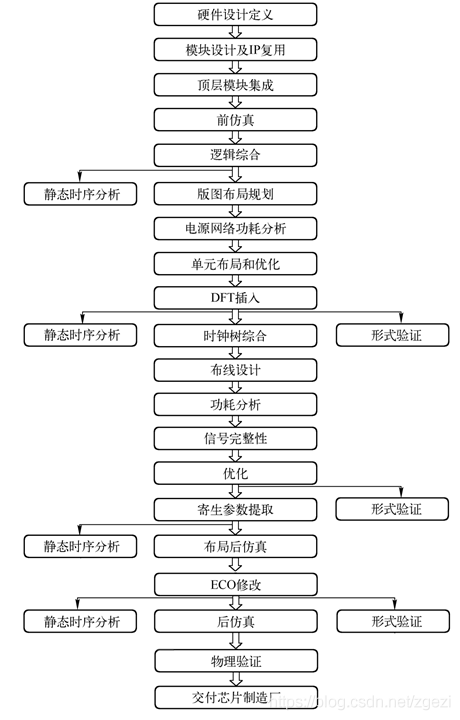

硬件设计定义说明(Hardware Design Specification)

硬件设计定义说明描述芯片总体结构、规格参数、模块划分、使用的总线,以及各个模块的详细定义等。

模块设计及IP复用(Module Design & IP Reuse)

对于需要重新设计的模块进行设计;对于可复用的IP核,通常由于总线接口标准不一致需要做一定的修改。

顶层模块集成(Top Level Integration)

顶层模块集成是将各个不同的功能模块,包括新设计的与复用的整合在一起,形成一个完整的设计。通常采用硬件描述语言对电路进行描述,其中需要考虑系统时钟/复位、I/O环等问题。

前仿真(Pre-layout Simulation)

前仿真也叫RTL级仿真。通过HDL仿真器验证电路逻辑功能是否有效。在前仿真时,通常与具体的电路物理实现无关,没有时序信息。

逻辑综合(Logic Synthesis)

逻辑综合是指使用EDA工具把由硬件描述语言设计的电路自动转换成特定工艺下的网表,即从RTL级的HDL描述通过编译与优化产生符合约束条件的门级网表。

版图布局规划(Floorplan)

版图布局规划完成的任务是确定设计中各个模块在版图上的位置,主要包括:

I/O规划,确定I/O的位置,定义电源和接地口的位置;

模块放置,定义各种物理的组、区域或模块,对这些大的宏单元进行放置;

供电设计,设计整个版图的供电网络,基于电压降(IR Drop)和电迁移进行拓扑优化。

功耗分析(Power Analysis)

在设计中的许多步骤都需要对芯片功耗进行分析,从而决定是否需要对设计进行改进。

在版图布局规划后,需要对电源网络进行功耗分析(PNA,Power Network Analysis),确定电源引脚的位置和电源线宽度。

在完成布局布线后,需要对整个版图的布局进行动态功耗分析和静态功耗分析。

除了对版图进行功耗分析以外,还应通过仿真工具快速计算动态功耗,找出主要的功耗模块或单元。

单元布局和优化(Placement & Optimization)

单元布局和优化主要定义每个标准单元的摆放位置并根据摆放的位置进行优化。

静态时序分析(STA,Static Timing Analysis)

STA是一种静态验证方法

通过对提取电路中所有路径上的延迟等信息的分析,计算出信号在时序路径上的延迟,找出违背时序约束的错误,如检查建立时间(Setup Time)和保持时间(Hold Time)是否满足要求。

形式验证(Formal Verification)

形式验证也是一种静态验证方法。

在整个设计流程中会多次引入形式验证用于比较RTL代码之间、门级网表与RTL代码之间,以及门级网表之间在修改之前与修改之后功能的一致性。

可测性电路插入(DFT,Design for Test)

可测性设计是SoC设计中的重要一步。通常,对于逻辑电路采用扫描链的可测试结构,对于芯片的输入/输出端口采用边界扫描的可测试结构。基本思想是通过插入扫描链,增加电路内部节点的可控性和可观测性,以达到提高测试效率的目的。一般在逻辑综合或物理综合后进行扫描电路的插入和优化。

时钟树综合(Clock Tree Synthesis)

SoC设计方法强调同步电路的设计,即所有的寄存器或一组寄存器是由同一个时钟的同一个边沿驱动的。构造芯片内部全局或局部平衡的时钟链的过程称为时钟树综合。分布在芯片内部寄存器与时钟的驱动电路构成了一种树状结构,这种结构称为时钟树。时钟树综合是在布线设计之前进行的。

布线设计(Routing)

这一阶段完成所有节点的连接。

寄生参数提取(Parasitic Extraction)

通过提取版图上内部互连所产生的寄生电阻和电容值,进而得到版图实现后的真实时序信息。

这些寄宿生电路信息将用于做静态时序分析和后仿真。

后仿真(Post-layout Simulation)

后仿真也叫门级仿真、时序仿真、带反标的仿真,需要利用在布局布线后获得的精确延迟参数和网表进行仿真,验证网表的功能和时序是否正确。后仿真一般使用标准延时(SDF,Standard Delay Format)文件来输入延时信息。

ECO修改(ECO,Engineering Change Order)

ECO修改是工程修改命令的意思。

这一步实际上是正常设计流程的一个例外。当在设计的最后阶段发现个别路径有时序问题或逻辑错误时,有必要通过ECO对设计的局部进行小范围的修改和重新布线,并不影响芯片其余部分的布局布线。在大规模的IC设计中,ECO修改是一种有效、省时的方法,通常会被采用。

物理验证(Physical Verification)

物理验证是对版图的设计规则检查(DRC,Design Rule Check)及逻辑图网表和版图网表比较(LVS,Layout Vs. Schematic)。

DRC用以保证制造良率。

LVS用以确认电路版图网表结构是否与其原始电路原理图(网表)一致。

来源:电子创新网

审核编辑黄昊宇

-

soc

+关注

关注

38文章

4218浏览量

219260 -

设计

+关注

关注

4文章

818浏览量

69964

发布评论请先 登录

相关推荐

Vivado之实现布局布线流程介绍

芯片设计进阶之SOC电源管理系统介绍

soc开发流程常见问题及解决方案

SOC芯片在汽车电子中的应用

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

简单介绍SoC设计流程

简单介绍SoC设计流程

评论