1. 面积与速度的平衡与互换

这里的面积指一个设计消耗FPGA/CPLD的逻辑资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更一般的衡量方式可以用设计所占的等价逻辑门数。

速度指设计在芯片上稳定运行所能达到的最高频率,这个频率由设计的时序状况来决定,以及设计满足的时钟要求:PAD to PAD time 、Clock Setup Time、Clock Hold Time、Clock-to-Output Delay等众多时序特征量密切相关。

面积和速度这两个指标贯穿FPGA/CPLD设计的时钟,是设计质量的评价的终极标准 —— 面积和速度是一对对立统一的矛盾体。

要求一个同时具备设计面积最小、运行频率最高是不现实的。更科学的设计目标应该是在满足设计时序要求(包括对设计频率的要求)的前提下,占用最小的芯片面积。或者在所规定的面积下,是设计的时序余量更大、频率跑的更高。这两种目标充分体现了面积和速度的平衡的思想。

作为矛盾的两个组成部分,面积和速度的地位是不一样的。相比之下,满足时序、工作频率的要求更重要一些,当两者冲突时,采用速度优先的准则。

从理论上讲,如果一个设计时序余量较大,所能跑的速度远远高于设计要求,那么就通过功能模块的复用来减少整个设计消耗的芯片面积,这就是用速度的优势换取面积的节约。反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么一般可以通过将数据流串并转换,并行复制多个操作模块,对整个设计采取乒乓操作和串并转换的思想运行。

2. 硬件原则

硬件原则主要针对HDL代码编写而言:Verilog是采用了C语言形式的硬件的抽象,它的本质作用在于描述硬件,它的最终实现结果是芯片内部的实际电路。所以评判一段HDL代码的优劣的最终标准是:其描述并实现的硬件电路的性能,包括面积和速度两个方面。

评价一个设计的代码水平较高,仅仅是说这个设计是由硬件想HDL代码这种表现形式的转换更加流畅、合理。而一个设计最终性能,在更大程度上取决于设计工程师所构想的硬件实现方案的效率以及合理性。(HDL代码仅仅是硬件设计的表达形式之一)

初学者片面追求代码的整洁、简短,是错误的,是与HDL的标准背道而驰的。正确的编码方法,首先要做到对所需实现的硬件电路胸有成竹,对该部分的硬件的结构和连接十分清晰,然后再用适当的HDL语句表达出来即可。

另外,Verilog作为一种HDL语言,是分层次的。系统级--算法级--寄存器传输级--逻辑级--门级--开关级。构建优先级树会消耗大量的组合逻辑,所以如果能够使用case的地方,尽量使用case代替if.....else......

3. 系统原则

系统原则包含两个层次的含义:更高层面上看,是一个硬件系统,一块单板如何进行模块花费和任务分配,什么样的算法和功能适合放在FPGA里面实现,什么样的算法和功能适合放在DSP/CPU里面实现,以及FPGA的规模估算数据接口设计等。具体到FPGA设计就要对设计的全局有个宏观上的合理安排,比如时钟域、模块复用、约束、面积、速度等问题,在系统上模块的优化最为重要。

一般来说实时性要求高,频率快的功能模块适合FPGA实现。而FPGA和CPLD相比,更适合实现规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。

比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富。FPGA/CPLD一般是由底层可编程硬件单元、BRAM、布线资源、可配置IO单元、时钟资源等构成。

底层可编程硬件单元一般由触发器和查找表组成。Xilinx的底层可编程硬件资源较SLICE,由两个FF和2个LUT构成。Altera的底层硬件资源叫LE,由1个FF和1个LUT构成。使用片内RAN可以实现单口RAM、双口RAM、同步/异步FIFO、ROM、CAM等常用单元模块。

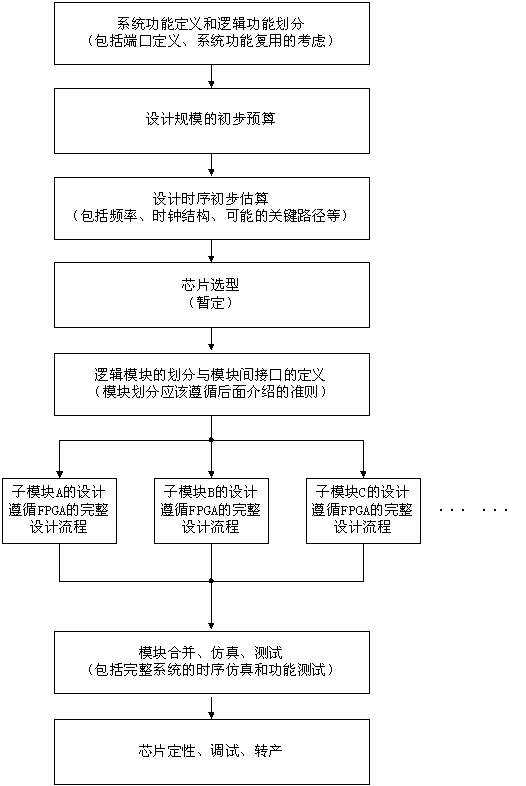

一般的FPGA系统规划的简化流程

4. 同步设计原则

异步电路的逻辑核心是用组合逻辑电路实现,比如异步的FIFO/RAM读写信号,地址译码等电路。电路的主要信号、输出信号等并不依赖于任何一个时钟性信号,不是由时钟信号驱动FF产生的。异步时序电路的最大缺点是容易产生毛刺,在布局布线后仿真和用逻辑分析仪观测实际信号时,这种毛刺尤其明显。

同步时序电路的核心逻辑用各种各样的触发器实现,电路的主要信号、输出信号都是由某个时钟沿驱动触发器产生出来的。同步时序电路可以很好的避免毛刺,布局布线后仿真,和用逻辑分析仪采样实际工作信号都没有毛刺。

是否时序电路一定比异步电路使用更多的资源呢?从单纯的ASCI设计来看,大约需要7个门来实现一个D触发器,而一个门即可实现一个2输入与非门,所以一般来说,同步时序电路比异步电路占用更大的面积。(FPGA/CPLD中不同,主要是因为单元块的计算方式)

如何实现同步时序电路的延时?异步电路产生延时的一般方法是插入一个Buffer、两级与非门等,这种延时调整手段是不适用同步时序设计思想的。首先要明确一点HDL语法中的延时控制语法,是行为级的代码描述,常用于仿真测试激励,但是在电路综合是会被忽略,并不能启动延时作用。

同步时序电路的延时一般是通过时序控制完成的,换句话说,同步时序电路的延时被当做一个电路逻辑来设计。对于比较大的和特殊定时要求的延时,一般用高速时钟产生一个计数器,通过计数器的计数控制延迟;对于比较小的延时,可以用D触发器打一下,这种做法不仅仅使信号延时了一个时钟周期,而且完成了信号与时钟的初次同步,在输入信号采样和增加时序约束余量中使用。

同步时序电路的时钟如何产生?时钟的质量和稳定性直接决定着同步时序电路的性能。输入信号的同步时序电路要求对输入信号进行同步化,如果输入数据的节拍和本级芯片的处理时钟同频,并且建立保持时间匹配,可以直接用本级芯片的主时钟对输入数据寄存器采样,完成输入数据的同步化。如果输入数据和本级芯片的处理时钟是异步的,特别是频率不匹配的时候,则要用处理时钟对输入数据做两次寄存器采样,才能完成输入数据的同步化。

是不是定义为Reg型,就一定综合成寄存器,并且是同步时序电路呢?答案的否定的。Verilog中最常用的两种数据类型Wire和Reg,一般来说,Wire型指定书数据和网线通过组合逻辑实现,而reg型指定的数据不一定就是用寄存器实现。

5. 乒乓操作

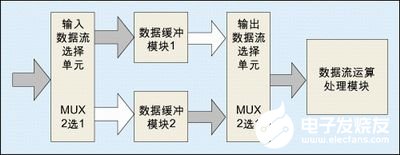

“ 乒乓操作 ” 是一个常常应用于数据流控制的处理技巧,乒乓操作的处理流程为:输入数据流通过 “ 输入数据选择单元 ” 将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口 RAM(DPRAM) 、单口 RAM(SPRAM) 、 FIFO 等。

● 在第一个缓冲周期,将输入的数据流缓存到 “ 数据缓冲模块 1” ;在第 2 个缓冲周期,通过 “ 输入数据选择单元 ” 的切换,将输入的数据流缓存到 “ 数据缓冲模块 2” ,同时将 “ 数据缓冲模块 1” 缓存的第 1 个周期数据通过 “ 输入数据选择单元 ” 的选择,送到 “ 数据流运算处理模块 ” 进行运算处理;在第 3 个缓冲周期通过 “ 输入数据选择单元 ” 的再次切换,将输入的数据流缓存到 “ 数据缓冲模块 1” ,同时将 “ 数据缓冲模块 2” 缓存的第 2 个周期的数据通过 “ 输入数据选择单元 ” 切换,送到 “ 数据流运算处理模块 ” 进行运算处理。如此循环。

典型的乒乓操作方法

乒乓操作的最大特点是,通过输入数据选择单元和输出数据选择单元、进行运算和处理。把乒乓操作模块当成一个整体,站在两端看数据,输入数据和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。所以乒乓操作常常应用于流水线式算法,完成数据的无缝缓冲和处理。

乒乓操作的第二个优点是可以节约缓冲区空间。比如在WCDMA基带应用中,1帧是由15个时隙组成的,有时需要将1整帧的数据延时一个时隙后处理,比较直接的方法就是将这帧数据缓存起来,然后延时一个时隙,进行处理。这时缓冲区的长度为1帧的数据长,假设数据速率是3.84Mb/s,1帧10ms,此时需要缓冲区的长度是38400bit,如果采用乒乓操作,只需定义两个缓冲1时隙的数据RAM,当向一个RAM写数据时,从另一块RAM读数据,然后送到处理单元处理,此时每块RAM的容量仅需2560bit,2块加起来5120bit的容量。

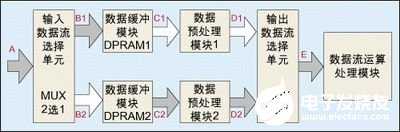

乒乓操作用低速模块处理高速数据流

另外,巧妙运用乒乓操作还可以达到用低速模块处理高速数据流的效果。如图 2 所示,数据缓冲模块采用了双口 RAM ,并在 DPRAM 后引入了一级数据预处理模块,这个数据预处理可以根据需要的各种数据运算,比如在 WCDMA 设计中,对输入数据流的解扩、解扰、去旋转等。假设端口 A 的输入数据流的速率为 100Mbps ,乒乓操作的缓冲周期是 10ms 。

6. 串并转换设计技巧

串并转换是 FPGA 设计的一个重要技巧,它是数据流处理的常用手段,也是面积与速度互换思想的直接体现。串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用寄存器、 RAM 等实现。

前面在乒乓操作的图例中,就是通过 DPRAM 实现了数据流的串并转换,而且由于使用了 DPRAM ,数据的缓冲区可以开得很大,对于数量比较小的设计可以采用寄存器完成串并转换。如无特殊需求,应该用同步时序设计完成串并之间的转换。比如数据从串行到并行,数据排列顺序是高位在前,可以用下面的编码实现:prl_temp<={prl_temp,srl_in}。

其中, prl_temp 是并行输出缓存寄存器, srl_in 是串行数据输入。对于排列顺序有规定的串并转换,可以用 case 语句判断实现。对于复杂的串并转换,还可以用状态机实现。串并转换的方法比较简单,在此不必赘述。

7. 流水线操作设计思想

首先需要声明的是,这里所讲述的流水线是指一种处理流程和顺序操作的设计思想,并非 FPGA 、 ASIC 设计中优化时序所用的 “Pipelining” 。

流水线处理是高速设计中的一个常用设计手段。如果某个设计的处理流程分为若干步骤,而且整个数据处理是 “ 单流向 ” 的,即没有反馈或者迭代运算,前一个步骤的输出是下一个步骤的输入,则可以考虑采用流水线设计方法来提高系统的工作频率。

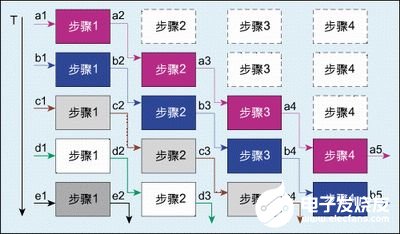

流水线设计的结构

流水线设计的结构示意图如图所示。其基本结构为:将适当划分的 n 个操作步骤单流向串联起来。流水线操作的最大特点和要求是,数据流在各个步骤的处理从时间上看是连续的,如果将每个操作步骤简化假设为通过一个 D 触发器 ( 就是用寄存器打一个节拍 ) ,那么流水线操作就类似一个移位寄存器组,数据流依次流经 D 触发器,完成每个步骤的操作。

流水线设计时序

流水线设计的一个关键在于整个设计时序的合理安排,要求每个操作步骤的划分合理。如果前级操作时间恰好等于后级的操作时间,设计最为简单,前级的输出直接汇入后级的输入即可;如果前级操作时间大于后级的操作时间,则需要对前级的输出数据适当缓存才能汇入到后级输入端;如果前级操作时间恰好小于后级的操作时间,则必须通过复制逻辑,将数据流分流,或者在前级对数据采用存储、后处理方式,否则会造成后级数据溢出。

在 WCDMA 设计中经常使用到流水线处理的方法,如 RAKE 接收机、搜索器、前导捕获等。流水线处理方式之所以频率较高,是因为复制了处理模块,它是面积换取速度思想的又一种具体体现。

8. 数据接口的同步方法

数据接口的同步是 FPGA/CPLD 设计的一个常见问题,也是一个重点和难点,很多设计不稳定都是源于数据接口的同步有问题。在电路图设计阶段,一些工程师手工加入 BUFT 或者非门调整数据延迟,从而保证本级模块的时钟对上级模块数据的建立、保持时间要求。

还有一些工程师为了有稳定的采样,生成了很多相差 90 度的时钟信号,时而用正沿打一下数据,时而用负沿打一下数据,用以调整数据的采样位置。这两种做法都十分不可取,因为一旦芯片更新换代或者移植到其它芯片 组的芯片上,采样实现必须重新设计。而且,这两种做法造成电路实现的余量不够,一旦外界条件变换 ( 比如温度升高 ) ,采样时序就有可能完全紊乱,造成电路瘫痪。

● 输入、输出的延时 ( 芯片间、 PCB 布线、一些驱动接口元件的延时等 ) 不可测,或者有可能变动的条件下,如何完成数据同步?对于数据的延迟不可测或变动,就需要建立同步机制,可以用一个同步使能或同步指示信号。另外,使数据通过 RAM 或者 FIFO 的存取,也可以达到数据同步目的。

设计数据接口同步是否需要添加约束?建议最好添加适当的约束,特别是对于高速设计,一定要对周期、建立、保持时间等添加相应的约束。这里附加约束的作用有两点:提高设计的工作频率,满足接口数据同步要求;获得正确的时序分析报告。

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/weixin_38423214/article/details/107630734

审核编辑:何安

-

FPGA设计

+关注

关注

9文章

428浏览量

26671

发布评论请先 登录

相关推荐

华邦电子安全闪存关键知识点

Docker-镜像的分层-busybox镜像制作

Aigtek功率放大器应用:电感线圈的知识点分享

后悔没有早点看到:天线设计中的知识点!

玩转FPGA必备的基础知识

FIFO Generator的Xilinx官方手册

关于反应热报告我们应该了解的知识

一个更适合工程师和研究僧的FPGA提升课程

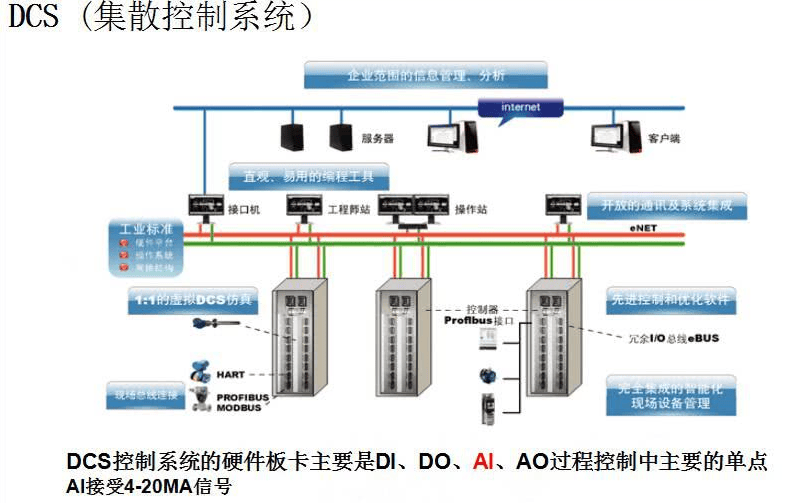

一篇搞定DCS系统相关知识点

关于FPGA设计的8大重要知识点

关于FPGA设计的8大重要知识点

评论