本文主要介绍信号完整性是什么,信号完整性包括哪些内容,什么时候需要注意信号完整性问题?

信号完整性是指高速产品设计中由互连线引起的所有问题。包括以下几部分:

时序

噪声

电磁干扰(EMI)

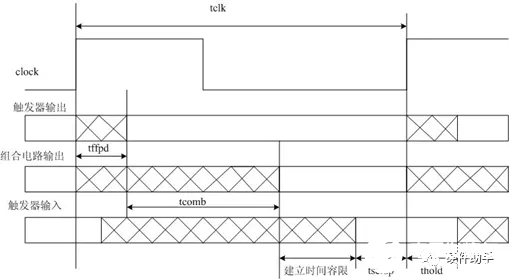

数据采样过程通常是由时钟信号的上升或者下降沿来触发的。数据必须及时的到达接收端并且在接收器件开始锁存之前稳定为一个非模糊的逻辑状态。任何数据的延迟或者波形的畸变将导致数据传输的失败。时序是高速系统的一切,信号时序取决于信号传播的物理长度引起的延迟,同时取决于抵达阀值时波形的形状。信号波形畸变的原因可能有很多的原因。主要的包括建立时间Tsu、保持时间Th、输出延时Tco、电路的线延迟Tdelay、时钟延时Tpd等。

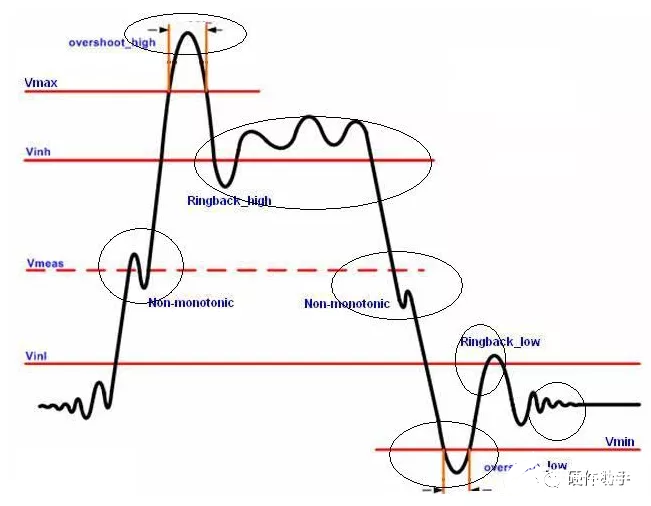

噪声问题具体来说有很多种形式,例如:振铃、反射、近端串扰、开关噪声、非单调性、地弹,电源反弹、衰减、容性负载、灵敏度、有损线等等。

与噪声有关的问题都可以从以下四个方面考虑:

单一网络信号的完整性:在一个信号的信号路径和返回路径上由于阻抗突变引起的反射与失真。

两个或多个网络的串扰:多个信号通路之间耦合的互电容、互电感。

电源和地分配中的轨道塌陷:电源和地网络中的阻抗压降。

来自整个系统的电磁干扰辐射:来自元件、系统、外界的电磁干扰。

针对第一种情况,由于互联线的阻抗发生变化,导致反射和失真(包括阻抗突变、反射、振铃、ISI、时序等),解决的方法是:

使用均匀传输线;

进行阻抗匹配。

针对第二种情况,由于两个互连网络之间的互容和互感引起容性耦合和感性耦合,而其中感性耦合占主导作用,对于感性耦合主导的噪声,我们常常把这种串扰归为开关噪声、△I噪声、dI-dt噪声、地弹、同步开关噪声(SSN)、同步开关输出噪声(SSO减小信号之间的串扰的方法如下:

采用介电质常数比较小的材料;

减小互连线的长度,互连线越长,串扰越严重;

增加线之间的距离。

只要存在两个电路,就会由于互容,一个电路的电压产生电场,影响另一个电路;只要存在两个电流回路,就会有互感,一个回路的电流产生磁场,影响另一个回路。

针对第三种情况,由于电压越来越低,功耗越来越大,电源噪声容限越来越小。因此在设计时要求电源阻抗低,地阻抗低,电源和地之间的阻抗低!所谓的低阻抗,在低频时取决于电源线的电感,中频时取决于板级的旁路电容,高频时取决于片内的分布电容阵列。具体的方法是:

相邻电源和地分配层平面的的介质应该尽可能的薄,以使它们紧紧地靠近;

低电感的去耦电容;

封装时安排多个很短的电源和地引脚;

片内加去耦电容。

针对第四种情况,电磁干扰问题有三个方面:噪声源、传播路径和天线。电磁干扰的强度和频率正相关,对于共模信号,电磁干扰强度和频率成正比。对于差模信号,电磁干扰强度和频率的平方成正比。

产生辐射的电压源大多数来自电源分配网络(由于PDN是电路板上最大的导体,因此也是最容易发射及接收噪声),因此减少轨道塌陷也能降低辐射。解决的方法从如下三个方面入手:

首先从电路设计的角度解决;

其次从接口滤波的角度阻隔;

最后才从屏蔽的角度规避。

以上就是针对信号完整性的一个简单的介绍,详细的内容以及分类方法各不相同,但具体问题的解决方法大都是相通的。

-

信号完整性

+关注

关注

68文章

1418浏览量

95779

发布评论请先 登录

相关推荐

iic协议的信号完整性测试

GND与信号完整性的关系

PCIe信号完整性问题解决方案

高速电路设计与信号完整性分析

什么是信号完整性

保障信号完整性的设计策略剖析

什么时候需要注意信号完整性问题

什么时候需要注意信号完整性问题

评论