描述

Xilinx 用两个 96 位独特器件标识符(称为器件 DNA)为每个 Zynq UltraScale+ 器件编程。

一个 DNA 值位于可编程逻辑 (PL) 中,另一个 DNA 值位于处理系统 (PS) 中。

这两个 DNA 值是不同的,但每个 DNA 都有以下属性及读取访问方法。

| DNA 位置 | 大小 | 不可修改(写保护) | 只读访问方法 |

|---|---|---|---|

| PL DNA | 96 位 | 有 |

PL DNA_PORTE2 原语(参见 UG974), or 通过 FUSE_DNA 指令 (opcode[11:0]=100100110010) JTAG PL TAP。 Vivado 硬件管理器显示 PL DNA 值。 |

| PS DNA | 96 位 | 不 |

PS APB(32 位)寄存器,地址: 0xFFCC100C (DNA_0) 0xFFCC1010 (DNA_1) 0xFFCC1014 (DNA_2) SDK XilSKey_ZynqMp_EfusePs_ReadDna API 返回 PS DNA 值。 |

PL DNA[93:57] 位值可能与 Xilinx 编程的 PS DNA[93:57] 位值不同。

解决方案

PL DNA 建议用于通过 Xilinx 二维码器件查找工具/请求识别器件的应用,或用于依靠不可修改独特器件标识符的安全应用。

实例:

如何使用附带的 AXI_DNA 内核从处理器访问 PL DNA。(在 Vivado/XSDK 2018.2 中完成测试)。

1) 在 ip_repo 文件夹中提取压缩文件附件。

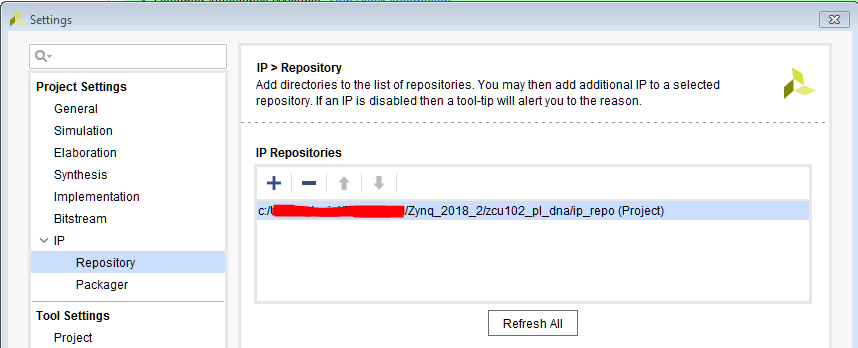

2) 将 ip_repo 目录添加到资源库中。

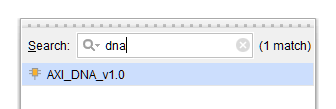

3) 将 AXI_DNA IP 添加到模块设计中,“运行自动”会其连接至处理器子系统并验证分配给 AXI DNA 的地址。

4) 将硬件导出至 XSDK,创建一个空项目并导入这三个文件(在 71342.zip 中附加到此答复记录):

dna_test.c

AXI_DNA_selftest.c

AXI_DNA.h

5) 编译,创建一个可引导的映像,观察 UART 终端上的以下输出:

***************************************

The PL DNA is: 400000000113746804416305

***************************************

附件

| 文件名 | 文件大小 | File Type |

|---|---|---|

| xilinx.com_user_AXI_DNA_1.0.zip | 13 KB | ZIP |

| 71342.zip | 2 KB | ZIP |

审核编辑:何安

发布评论请先 登录

相关推荐

针对ZYNQ+ULTRASCALE的FPGA供电的一些疑问求解答

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

为Xilinx® Zynq®UltraScale™系列多处理器中的VCCINT_VCU轨供电

使用TPS65086x PMIC为Xilinx Zynq UltraScale MPSoC供电

AMD助力PlanetSpark公司开发AI边缘盒子EdgeAI Box X7

一个更适合工程师和研究僧的FPGA提升课程

中高端FPGA如何选择

AMD推出全新Spartan UltraScale+ FPGA系列

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

AMD推出Spartan UltraScale+ FPGA系列产品

为嵌入式应用选择AMD Spartan UltraScale+FPGA

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上为FPGA设计PCB的步骤详解

Zynq UltraScale+ 器件与PL DNA不同的值

Zynq UltraScale+ 器件与PL DNA不同的值

评论