作者:watchmanZYNQ微信公众号

出现问题以及分析

vivado2017.4生成比特流失败,报错信息:

[Drc 23-20]规则违反(NSTD-1)未指定的I/O标准,-142个逻辑端口中有4个使用I/O标准(IOSTANDARD)值“ DEFAULT”,而不是用户分配的特定值。

这可能会导致I/O争用或与电路板电源或连接性不兼容,从而影响性能,信号完整性,或者在极端情况下会损坏设备或所连接的组件。

若要更正此冲突,请指定所有I/O标准。除非所有逻辑端口都定义了用户指定的I/O标准值,否则此设计将无法生成位流。

要允许使用未指定的I/O标准值创建位流(不建议),请使用以下命令:set_property SEVERITY {Warning} [get_drc_checks NSTD-1].NOTE

使用Vivado Runs基础结构时(例如,launch_runs Tcl命令),请将此命令添加到.tcl文件,并将该文件作为执行运行的write_bitstream步骤的预钩添加。

问题端口:USBIND_0_port_indctl [1:0],USBIND_0_vbus_pwrfault,USBIND_0_vbus_pwrselect。

解决办法:

新建记事本,添加以下三句:

1set_property SEVERITY {Warning} [get_drc_checks NSTD-1] 2 3set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1] 4 5set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

重命名为 name.tcl文件(确定后缀格式有效)

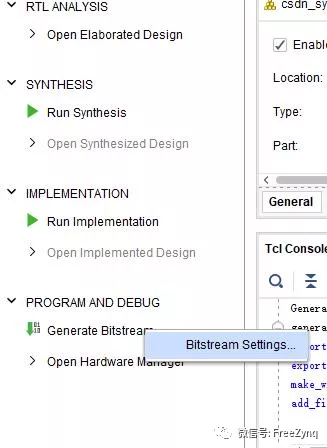

在进入vivado软件,在generate bitstream 界面如下,右键进入setting

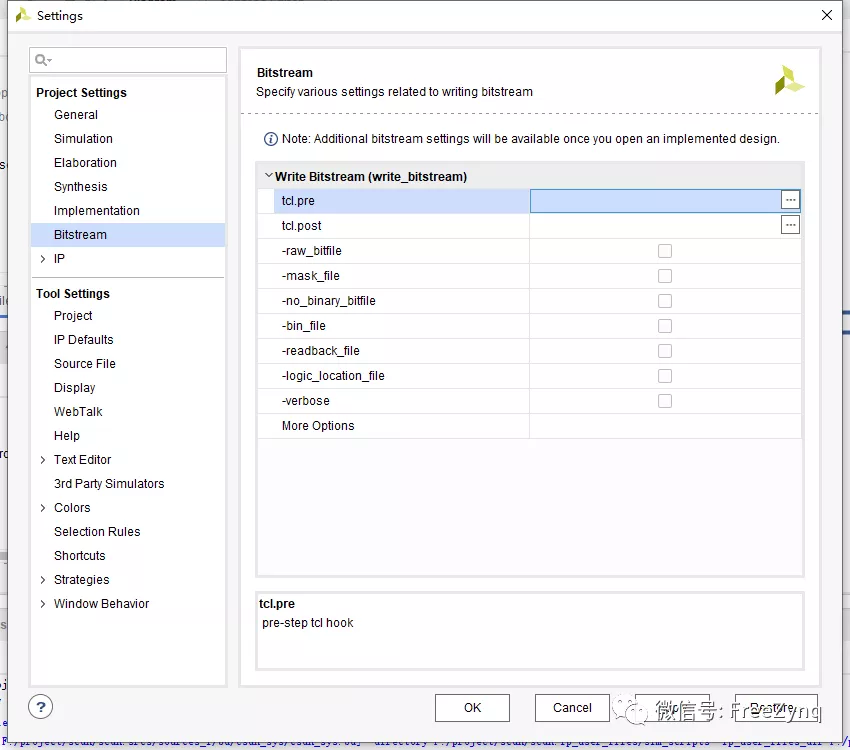

点击tcl.pre

选中刚才配置的name.tcl

点击OK,就行了,之后就可以成功生成bit流了。

审核编辑:何安

-

Vivado

+关注

关注

19文章

815浏览量

66962

发布评论请先 登录

相关推荐

cmdgc5016生成的配置寄存器值居然没有变化,有人能解释下吗?

DAC1280 TDATA引脚输入的比特流,怎么产生这个比特流,算法是什么?

SRIO介绍及xilinx的vivado 2017.4中生成srio例程代码解释

请问怎么理解DAC1280的比特流?

一文了解FPGA比特流的内部结构

vivado2017.4生成比特流失败报错信息

vivado2017.4生成比特流失败报错信息

评论