0、绪论

在 AMBA 系列之 AXI 总线协议初探 中,了解到 AXI 总线交互分为 Master / Slave 两端,而且标准的 AXI 总线支持不同的位宽,既然是总线,那么必须要支持总线互联,多 Master,多 Slave的场景,在 AMBA AXI Specification 的 “AXI Architecture-》Interface and Interconnect ”章节 描述了 Interconnect 的含义;用于AXI总线互联,而且给出了一些基本的互联拓扑结构:

1、共享地址和数据总线

2、共享地址总线,多个数据总线

3、多个地址总线、多个数据总线

根据实际系统的需求,不同的交互速度和互联复杂程度来折中选择方案;

换句话来说,实际的工程中,一个(或者多个)实际的主设备有 AXI Master 控制器,一个(或者多个)从设备有 AXI Slave 控制器,他(们)之间通过 Interconnect 作为桥梁,制定一套互联的规矩(数据/地址总线等);我们可以把这个 AXI Interconnect 理解为一个独立的 IP Core 负责一些互联的事务;

Xilinx 定义了一套它的 AXI Interconnect IP,在 Xilinx 官方网站有对这个 IP 的介绍:

https://china.xilinx.com/products/intellectual-property/axi_interconnect.。.

Xilinx 的 AXI Interconnect IP Core 核心,由 Product Guide 095 (PG095)来描述:

https://www.xilinx.com/support/documentation/ip_documentation/axi_interc.。.

Xilinx 的 AXI Interconnect IP 和 Vivado Design Suite捆绑,产品描述:

包含在Vivado 和 ISE 设计套件中,不收取额外费用

AXI Interconnect IP 将一个或多个 AXI 存储器映射的主器件连接到一个或多个存储器映射的从器件。AXI 接口符合 ARM® 的 AMBA® AXI 第 4 版规范,包括 AXI4-Lite 控制寄存器接口子集。Interconnect IP 仅用于存储器映射传输;AXI4-Stream 传输不适用。AXI Interconnect IP 可作为嵌入式开发套件 (EDK) 中 Vivado® IP 目录中的处理器内核使用,或者作为 CORE Generator™ IP 目录中的独立内核使用。

AXI4-Stream 互联参考:《AXI4-Stream Infrastructure IP Suite LogiCORE IP Product Guide (PG085)》

Product Guide 095 (PG095)中具体描述了 AXI Interconnect 支持的功能:

AXI互联IP核允许任意AXI主设备和AXI从设备的连接,可以根据数据位宽、时钟域和 AXI Sub-protocol 进行转换。当外部主设备或从设备的接口特性不同于互联模块内部的crossbar switch的接口特色时,相应的基本模块(Infrastructure cores)就会被自动的引入来执行正确的转换;

支持的 Feature 如下:

AXI Crossbar:将一个或者多个相似的 AXI memory-mapped Master 设备连接到一个或者多个相似的AXI memory-mapped Slave 设备,也就是 Masters 和 Slaves 的互联;

AXI Data Width Converter:将一个AXI memory-mapped Master 连接到一个数据位宽不同的AXI memory-mapped Slave 设备;

AXI Clock Converter:将一个 AXI memory-mapped Master 连接到一个不同时钟域(Clock domain)的 AXI memory-mapped Slave设备;

AXI Protocol Converter:将 AXI4、AXI3 或者 AXI4-Lite 协议的 Master 连接到不同 AXI 协议的内存映射 Slave 设备;

AXI Data FIFO:在 AXI memory-mapped Master 和 Slave 之间增加一组 FIFO 的缓冲;

AXI Register Slice:在 AXI memory-mapped Master 和 Slave 之间增加一组流水线寄存器;

AXI MMU:为 AXI 提供地址段的 decoding and remapping 服务

下面简单介绍一下一些部分

1、AXI Crossbar

每一个被实例化的 AXI Interconnect (互联模块)都包含一个 AXI Crossbar,用于多个 MI(Master Interface) 和 SI(Slave Interface) 的连接;

Crossbar 的 SI 可以被配置为 1 ~ 16 个 SI Slots,最多接受来自 16 个 Master 的传输,同样,MI 可以被配置为 1 ~ 16 个 MI Slots,最多与 16 个 Slaves 进行通信;

1.1、几种可以选择的 Crossbar 互联结构

1.1.1、Crossbar mode (Performance Optimized)

性能最优:

共享地址通道,独立的多数据通道架构 (SAMD:Shared-Address, Multiple-Data);

并行 crossbar 读和写通道,当发生多读写的时候,可以完全并行,互不干扰;

可以根据配置连接的映射来减少 crossbar 数据路径进而减少资源的使用;

共享的写地址仲裁器,加上一个共享的读地址仲裁器,通常仲裁器并不会影响吞吐;

只有 AXI Crossbar 被配置为 AXI-4 或者 AXI-3 的时候,Crossbar mode 才有效;

1.1.2、Shared Access mode (Area optimized)

面积最优:

共享的写入数据、共享读取数据和单独的共享地址路径;

一次传输仅支持一个事务;

使用资源最小;

更多的描述详见文章开头的 PG095

2、AXI Data Width Converter

Master 和 Slave 端 Interface 不同数据位宽的转换:

支持的 Slave Interface(SI) 数据位宽为:32, 64, 128, 256, 512 or 1,024 bits

支持的 Master Interface(MI) 数据位宽为:32, 64, 128, 256, 512 or 1,024 bits (must be different than SI data width)。

When upsizing, data is packed (merged) when permitted by address channel control signals (CACHE modifiable bit is asserted)。

When downsizing, burst transactions are split into multiple transactions if the maximum burst length would otherwise be exceeded

When upsizing, the IP core can optionally perform FIFO buffering and clock frequency conversion (synchronous or asynchronous) in a resource-efficient manner

3、AXI Clock Converter

Master 和 Slave 端 Interface 不同时钟域

支持同步时钟的比例转换,(N:1 and 1:N),转换的 N 是 2

支持异步时钟转换(比同步时钟消耗更多的资源,和 latency)

4、AXI Protocol Converter

4.1、AXI4 or AXI3 to AXI4-Lite protocol

AXI-4 或者 AXI-3 转到 AXI4-Lite 协议,burst 事务转为 AXI4-Lite 的 Single-Beat 传输

4.2、AXI4 to AXI3 protocol

当针对 AXI3 从器件时,可通过分解事务处理内容来转换大于 16 拍的 AXI4 突发量

5、AXI Data FIFO

读写通道独立可配置

基于 32-深度的 LUT-RAM

基于 512-深度的 BRAM

6、小结

简单的描述了 Xilinx AXI Interconnect IP 的部分内容,它的实现内部需要集成 Arbiter 或者 Router 来进行逻辑互联,官方的简要描述如下:

可选的互联架构

纵横机模式(性能最优化):共享地址多数据 (SAMD) 纵横机架构,具有面向写入和读取数据通道的并行路径

共享访问模式(面积最优化):共享的写入数据、共享读取数据和单独的共享地址路径。

AXI 兼容协议(AXI3、AXI4 和 AXI4-Lite)包括:

针对增量 (INCR) 突发量的长达 256 的突发长度

当针对 AXI3 从器件时,可通过分解事务处理内容来转换大于 16 拍的 AXI4 突发量

生成 REGION 输出,供有多个地址解码范围的从器件使用

在每条通道上传播 USER 信号(如果有); 独立的每通道 USER 信号宽度(可选)

传播服务质量 (QoS) 信号(如果有);不被 AXI Interconnect 内核使用(可选)

接口数据宽度:

AXI4: 32、 64、 128、 256、 512、 或 1024 位

AXI4-Lite: 32 位

32 位地址宽度

连接 1-16 个主器件和 1-16 个从器件

内置数据宽度转换、同步/异步时钟速率转换和 AXI4-Lite/AXI3 协议转换功能

可选的寄存器 slice 流水线和数据路径 FIFO 缓冲

可选的数据包 FIFO 功能

时延发出 AWVALID 信号,直到完整的突发量存储在写数据 FIFO 中为止

时延发出 ARVALID 信号,直到读数据 FIFO 有足够的空间存储整个突发量长度为止

在纵横机模式下支持多种出色的事务处理功能

循环依赖(死锁)的 “每 ID 单从器件” 避免法

固定优先权和轮询仲裁

支持整体针对每个已连接从器件的 “信任区” 安全功能

支持只读和只写主器件和从器件,减少资源使用。

审核编辑:何安

-

AXI

+关注

关注

1文章

127浏览量

16617

发布评论请先 登录

相关推荐

LM4871功放IN+/-两端、OUT+/-两端,在上电静态时电压不平衡怎么解决?

光收发器两端分别接到哪里

瞬时极性法电容两端极性判断

电源两端的电压为什么是路端电压

THS4541输出的两端信号不是差分的,两端信号相位是一致的,怎么解决?

滑动变阻器能直接接在电源两端吗

电容两端的电压由什么决定

电容两端的电压会发生骤然的变化

为什么把电压探头并在PFC电感两端会烧掉保险?

SoC设计中总线协议AXI4与AXI3的主要区别详解

需要用两个电流源并联连接在负载两端

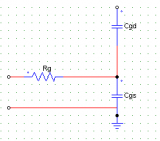

MOS管驱动电路gs两端并接一个电阻有何作用?

为什么有的RS485总线两端必须安装有源终端电阻?

直接量差分信号两端为什么测不准?解析原因及解决方案!

AXI 总线交互分为 Master / Slave 两端

AXI 总线交互分为 Master / Slave 两端

评论