•具有D寄存器的25位预加器,以增强A路径的能力

•INMODE控件支持在乘法(A*B)和加法操作(A:B)之间动态切换的平衡流水

•25*18乘法

•30位的输入,其下25位为乘法器的A输入,整个30位的输入形成48位A:B的上30位串联内部总线。

•级联A和B输入

•直接路径和级联路径之间的半独立可选pipelining

•独立的时钟支持两层的A和B输入寄存器

•独立的C输入和C寄存器,具有独立的复位和时钟启用。

•CARRYCASCIN和CARRYCASCOUT内部级联信号支持两个DSP48E1片中的96位累加器/加法器/减法器

•MULTSIGNIN和MULTSIGNOUT内部级联信号与特殊的OPMODE设置,以支持一个96位的MACC扩展

•单指令多数据(SIMD)模式的三输入加法器/减法器,在第一阶段排除了乘数的使用

•双24位SIMD加法器/减法器/累加器,具有两个独立的结转信号

•四路12位SIMD加法器/减法器/累加器,有四个独立的输出信号

•48位逻辑单元

•位逻辑操作-双输入AND,OR,NOT,NAND,NOR,XOR,XNOR

•逻辑单元模式可通过ALUMODE动态选择

•模式检测器

•溢出/下溢的支持

•收敛舍入支持

•终端计数检测支持和自动复位

•级联48位P总线支持内部低功耗加法器级联

•48位P总线允许12位/4位或24位/双SIMD加法器级联支持

•可选17位右移,使更广泛的乘数实现

•动态用户控制的操作模式

•7位OPMODE控制总线提供X、Y和Z多路选择信号

•Carryin第二阶段加法器

•支持舍入

•支持更广泛的增加/减少

•3位CARRYINSEL多路复用器

•Carryout第二阶段加法器

•支持更广泛的增加/减少

•每个SIMD加法器可用(最多4个)

•级联CARRYCASCOUT和MULTSIGNOUT允许MACC扩展到96位

•可选的输入、流水线和输出/累加寄存器

可选控制信号寄存器(OPMODE、ALUMODE和CARRYINSEL)

•独立的时钟启用和重置更大的灵活性,重置具有优先级。

•为了在第一阶段的乘法器不使用时节省电力,USE_MULT属性允许客户关闭内部乘法器逻辑。

每个DSP48E1片都有一个双输入乘法器和一个三输入加法器/减法器/累加器。DSP48E1乘法器具有非对称的输入,接受18位2的补数操作数和25位2的补数操作数。乘法器阶段以两个部分乘积的形式产生一个43位2的补码结果。这些部分积在X多路复用器和Y多路复用器中被符号扩展到48位,并被输入到三输入加法器中进行最终求和。这将产生一个43位的乘法输出,它已经被签名扩展到48位。因此,当乘法器被使用时,加法器有效地变成一个双输入加法器。

第二阶段加法器/减法器接受三个48位的补数操作数,并产生一个48位的补数操作数,当乘法器通过设置USE_MULT属性为NONE并使用适当的OPMODE设置来绕过该乘法器时,得到2的补数结果。在SIMD模式下,48位加法器/减法器也支持双24位或双12位SIMD算术运算。在这种配置中,动态ALUMODE控制信号也支持对两个48位二进制数的按位逻辑操作。

在DSP48E1列中,级联各个DSP48E1片可以支持更高级的DSP功能。两个数据路径(ACOUT和BCOUT)和DSP48E1片输出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供级联功能。级联数据路径的能力在过滤器设计中很有用。例如,有限脉冲响应(FIR)滤波器的设计可以使用级联输入来安排一系列的输入数据样本,使用级联输出来安排一系列的部分输出结果。级联的能力提供了高性能和低功耗的DSP滤波器功能的实现,因为一般的路由在fabric中没有使用。

C输入端口允许形成许多3-输入数学函数,如3-输入加法或2-输入加法乘法。这个函数的一个子集是对乘法趋近于零或无穷大的对称舍入的宝贵支持。C输入和模式检测器也支持收敛舍入。

对于多精度算法,DSP48E1片提供了17的右移。因此,一个DSP48E1切片的部分积可以右对齐并添加到相邻DSP48E1切片中计算的下一个部分积。使用这种技术,DSP48E1片可以用来构建更大的乘数。

可编程的输入操作数、中间结果和累加器输出流水线提高了吞吐量。48位的内部总线(PCOUT/PCIN)允许将DSP片聚合到单个列中。当跨越多个列时,需要使用Fabric逻辑。

DSP48E1片输出处的Thepatterndetector模式检测器支持收敛舍入、溢出/下溢、块浮点和累加器终端计数(计数器自动复位)。模式检测器可以检测DSP48E1片的输出是否符合模式(由掩码限定)。

DSP48E1Tile和互连

两个DSP48E1片和专用互连形成一个DSP48E1Tile(参见图2-3)。DSP48E1Tile垂直地堆叠在DSP48E1列中。DSP48E1Tile的高度与五个可配置逻辑块(CLBs)相同,并且与一个块RAM的高度匹配。7系列设备中的块RAM可分为两个18K块RAM。每个DSP48E1片与一个18K块RAM水平对齐。7系列设备最多有20个DSP48E1列。

-

FPGA

+关注

关注

1629文章

21729浏览量

603013 -

DSP48E1

+关注

关注

0文章

5浏览量

604

发布评论请先 登录

相关推荐

当DSP与FPGA通讯的时候,XZCS0、XZCS6、XZCS7会影响ADS8556的工作吗?

ED6H系列FPGA口袋实验室

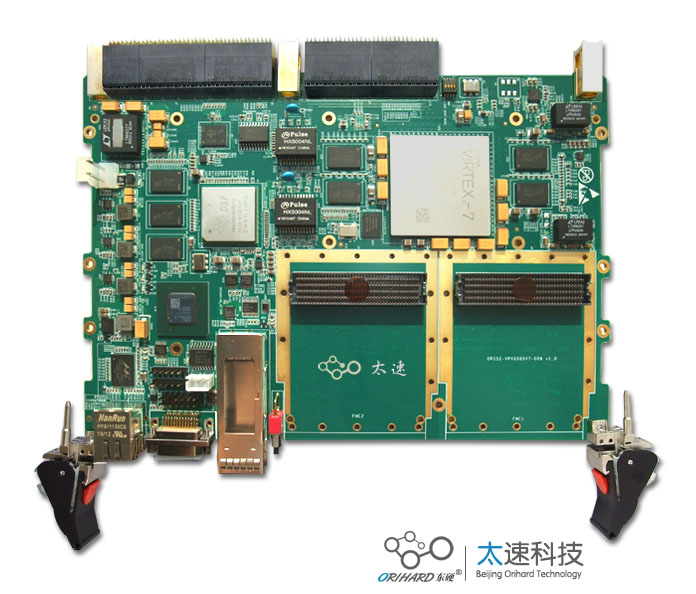

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信号处理卡

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

【RA-Eco-RA2E1-48PIN-V1.0开发板试用】RA-Eco-RA2E1-48PIN-V1.0开发板基于Keil MDK环境搭建

【RA-Eco-RA2E1-48PIN-V1.0开发板试用】带你认识RA-Eco-RA2E1-48PIN-V1.0开发板

【RA-Eco-RA2E1-48PIN-V1.0开发板试用】1、开箱+环境搭建

DSP电机控制程序的概述

FPGA核心板 Xilinx Artix-7系列XC7A100T开发平台,米尔FPGA工业开发板

宽电压输入稳压电源模块 E48_UHFCS-3W系列

Xilinx fpga芯片系列有哪些

华普微强芯加持!低功耗SPI模块E48系列,可替代多款芯片方案

AMD Xilinx 7系列FPGA的Multiboot多bit配置

7系列FPGA DSP48E1的参数特点概述

7系列FPGA DSP48E1的参数特点概述

评论