原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

本文主要讲解使用PWM控制LED,实现呼吸灯的效果。

1.实验原理

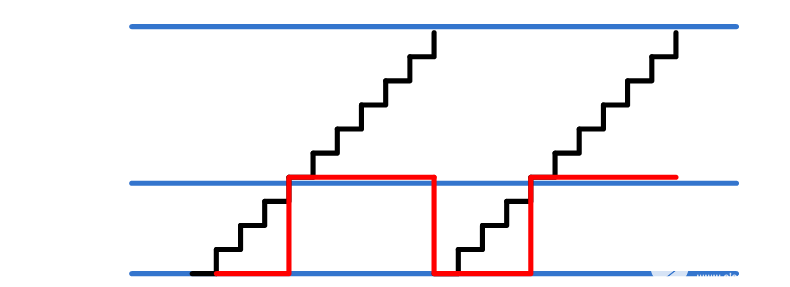

如下图所示,用一个N比特的计数器,最大值可以表示为2的N次方,最小值0,计数器以“period”为步进值累加,加到最大值后会溢出,进入下一个累加周期。当计数器值大于“duty”时,脉冲输出高,否则输出低,这样就可以完成图中红色线所示的脉冲占空比可调的脉冲输出,同时“period”可以调节脉冲频率,可以理解为计数器的步进值。

PWM脉宽调制示意图

PWM脉宽调制示意图

不同的脉冲占空比的方波输出后加在LED上,LED灯就会显示不同的亮度,通过不断地调节方波的占空比,从而实现LED灯亮度的调节。

2. 实验设计

PWM模块设计非常简单,在上面的原理中已经讲到,这里不再说原理。

| 信号名称 | 方向 | 说明 |

| clk | in | 时钟输入 |

| rst | in | 异步复位输入,高复位 |

| period | in | PWM脉宽周期(频率)控制。period = PWM输出频率 * (2 的N次方) / 系统时钟频率。显然N越大,频率精度越高。 |

| duty | in | 占空比控制,占空比 = duty / (2的N次方)* 100% |

PWM模块(ax_pwm)端口

`timescale1ns/1psmoduleax_pwm#( parameterN=16//pwmbitwidth )(inputclk,inputrst,input[N-1:0]period, //pwmstepvalueinput[N-1:0]duty, //dutyvalueoutputpwm_out //pwmoutput);reg[N-1:0]period_r; //periodregisterreg[N-1:0]duty_r; //dutyregisterreg[N-1:0]period_cnt; //periodcounterregpwm_r;assignpwm_out=pwm_r;always@(posedgeclkorposedgerst)beginif(rst==1)begin period_r<={ N {1'b0}}; duty_r <={ N {1'b0}};endelsebegin period_r <= period; duty_r <= duty;endend//period counter, step is period valuealways@(posedge clk orposedge rst)beginif(rst==1) period_cnt <={ N {1'b0}};else period_cnt <= period_cnt + period_r;endalways@(posedge clk orposedge rst)beginif(rst==1)begin pwm_r <=1'b0;endelsebeginif(period_cnt >=duty_r) //ifperiodcounterisbiggerorequalstodutyvalue,thensetpwmvaluetohighpwm_r<=1'b1;else pwm_r <=1'b0;endend

那么如何实现呼吸灯的效果呢?我们知道呼吸灯效果是由暗不断的变亮,再由亮不断的变暗的过程,而亮暗效果是由占空比来调节的,因此我们主要来控制占空比,也就是控制duty的值。

在下面的测试代码中,通过设置period的值,设定PWM的频率为200Hz,PWM_PLUS状态即是增加duty值,如果增加到最大值,将pwm_flag置1,并开始将duty值减少,待减少到最小的值,则开始增加duty值,不断循环。其中PWM_GAP状态为调整间隔,时间为100us。

`timescale1ns/1psmodulepwm_test(input clk, //25MHzinput rst_n, //lowactive output led //high-off,low-on); localparamCLK_FREQ=25; //25MHzlocalparamUS_COUNT=CLK_FREQ; //1uscounterlocalparamMS_COUNT=CLK_FREQ*1000; //1mscounterlocalparamDUTY_STEP =32'd100000; //dutysteplocalparamDUTY_MIN_VALUE=32'h6fffffff; //dutyminimumvaluelocalparamDUTY_MAX_VALUE=32'hffffffff; //dutymaximumvalue localparamIDLE =0; //IDLEstatelocalparamPWM_PLUS =1;//PWMdutyplusstatelocalparamPWM_MINUS =2;//PWMdutyminusstatelocalparamPWM_GAP =3;//PWMdutyadjustmentgapwire pwm_out; //pwmoutputreg[31:0] period; //pwmstepvaluereg[31:0] duty; //dutyvaluereg pwm_flag; //dutyvalueplusandminusflag,0:plus;1:minusreg[3:0] state;reg[31:0] timer; //dutyadjustmentcounterassignled=~pwm_out;//ledlowactivealways@(posedgeclkornegedgerst_n)begin if(rst_n==1'b0) begin period <=32'd0; timer <=32'd0; duty <=32'd0; pwm_flag <=1'b0; state <= IDLE; end else case(state) IDLE: begin period <=32'd17179;//The pwm step value, pwm 200Hz(period = 200*2^32/50000000) state <= PWM_PLUS; duty <= DUTY_MIN_VALUE; end PWM_PLUS : begin if(duty >DUTY_MAX_VALUE-DUTY_STEP) //ifdutyisbiggerthanDUTYMAXVALUEminusDUTY_STEP,begintominusdutyvalue begin pwm_flag <=1'b1; duty <= duty - DUTY_STEP ; end else begin pwm_flag <=1'b0; duty <= duty + DUTY_STEP ; end state <= PWM_GAP ; end PWM_MINUS : begin if(duty < DUTY_MIN_VALUE + DUTY_STEP) //if duty is little than DUTY MIN VALUE plus duty step, begin to add duty value begin pwm_flag <=1'b0; duty <= duty + DUTY_STEP ; end else begin pwm_flag <=1'b1; duty <= duty - DUTY_STEP ; end state <= PWM_GAP ; end PWM_GAP: begin if(timer >=US_COUNT*100)//adjustmentgapis100us begin if(pwm_flag) state<= PWM_MINUS ; else state <= PWM_PLUS ; timer <=32'd0; end else begin timer <= timer +32'd1; end end default: begin state <= IDLE; end endcaseend//Instantiate pwm moduleax_pwm#(.N(32))ax_pwm_m0(.clk (clk),.rst (~rst_n),.period (period),.duty (duty),.pwm_out (pwm_out)); endmodule

3. 下载验证

生成bitstream,并下载bit文件,可以看到PL LED1灯产生呼吸灯效果。PWM是比较常用的模块,比如风扇转速控制,电机转速控制等等。

-

FPGA

+关注

关注

1629文章

21736浏览量

603387 -

PWM

+关注

关注

114文章

5186浏览量

213939 -

Zynq

+关注

关注

10文章

609浏览量

47181 -

MPSoC

+关注

关注

0文章

198浏览量

24282 -

呼吸灯

+关注

关注

10文章

110浏览量

42731

发布评论请先 登录

相关推荐

《DNESP32S3使用指南-IDF版_V1.6》第十章 LED实验

AMD/Xilinx Zynq® UltraScale+ ™ MPSoC ZCU102 评估套件

在米尔电子MPSOC实现12G SDI视频采集H.265压缩SGMII万兆以太网推流

迅为iTOP-RK3568开发板驱动开发指南-第十八篇 PWM

在米尔电子MPSOC实现12G SDI视频采集H.265压缩SGMII万兆以太网推流

《DNK210使用指南 -CanMV版 V1.0》第十章 板卡信息实验

使用TPS65086x PMIC为Xilinx Zynq UltraScale MPSoC供电

ALINX FPGA+GPU异架构视频图像处理开发平台介绍

一个更适合工程师和研究僧的FPGA提升课程

AMD推出全新Spartan UltraScale+ FPGA系列

AMD推出Spartan UltraScale+ FPGA系列产品

AMD 扩展市场领先的 FPGA 产品组合,推出专为成本敏感型边缘应用打造的AMD Spartan UltraScale+ 系列

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上为FPGA设计PCB的步骤详解

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十章PWM呼吸灯实验

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十章PWM呼吸灯实验

评论