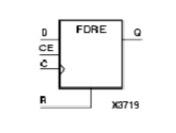

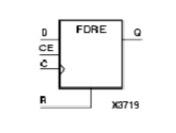

1、源语---FDRE

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据输出(dataout,Q)。当输入的同步复位信号为高时,否决(override)所有输入,并在时钟的上升沿将输出Q为低信号。在时钟的上升沿数据被加载进入D触发器的输入。

FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), // 同步时钟 .D (data_sync0), //异步数据输入 .Q (data_sync1), //同步数据输出 .CE (1'b1), //时钟使能信号 .R (1'b0) //复位信号输入,高电平有效 );

由于数据可能与时钟存在着不同步的情况,尤其是在对同步精度要求高的场合,一般还是用多次FDRE源语使得数据、控制信号等同步,例如在一个三态网数据同步模块中使用了四个D触发器进行数据同步:

`timescale 1ps / 1ps (* dont_touch = "yes" *) module tri_mode_ethernet_mac_0_sync_block #( parameter INITIALISE = 1'b0, parameter DEPTH = 5 ) ( input clk, // clock to be sync'ed to input data_in, // Data to be 'synced' output data_out // synced data ); // Internal Signals wire data_sync0; wire data_sync1; wire data_sync2; wire data_sync3; wire data_sync4; (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg0 ( .C (clk), .D (data_in), .Q (data_sync0), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), .D (data_sync0), .Q (data_sync1), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg2 ( .C (clk), .D (data_sync1), .Q (data_sync2), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg3 ( .C (clk), .D (data_sync2), .Q (data_sync3), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg4 ( .C (clk), .D (data_sync3), .Q (data_sync4), .CE (1'b1), .R (1'b0) ); assign data_out = data_sync4; endmodule

审核编辑 黄昊宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx

+关注

关注

71文章

2167浏览量

121406 -

触发器

+关注

关注

14文章

2000浏览量

61155

发布评论请先 登录

相关推荐

硬件描述语言(HDL)编码技术:xilinx verilog语法技巧

xilinx verilog语法技巧 一 硬件描述语言(HDL)编码技术让您: •描述数字逻辑电路中最常见的功能。 •充分利用Xilinx®器件的架构特性。 1 Flip-Flops

实施可行性警告:时钟驱动太多寄存器

/ host_addr_r_reg [3] {FDRE}据我所知,这是我将单个时钟引脚连接到多个模块的情况。但是从RTL的角度来看,会在每个内部添加额外的缓冲区来解决问题吗?我假设Xilinx工具会在

发表于 10-26 15:00

altera的ip源语在哪里可以获取?在官网找的话要怎么搜索,有知道的大神求告知一下!

1.由于每次通过ip调取不方便移植也麻烦,所以需要获取源语进行例化。有知道的大神求告知,链接代码均可,常用的ip,ram,fifo,pll这些

发表于 01-14 10:15

关于labview输入越南语乱码

请问有没有大佬知道labview支不支持越南语语言啊,我开了unicode输入越南语还是会乱码,可以显示出越南语但是输入到具体结构里面就会乱码。请问有大佬知道怎么解决吗

发表于 09-27 15:57

通信行业最齐全的英语缩语手册

通信行业最齐全的英语缩语手册:通信英语缩语手册通信英语缩语手册A&EM Alarm & Event Management 告警与事件管理 A&VE Audio / Video Editor 音频/视频编辑器 A-A Analog

发表于 02-11 12:43

•43次下载

在Xilinx FPGA上单源SYCL C++实现运行的方法

在此Xilinx研究实验室演示中,解释了单源SYCL C ++示例以及生成在Xilinx FPGA上运行的硬件实现的方法。

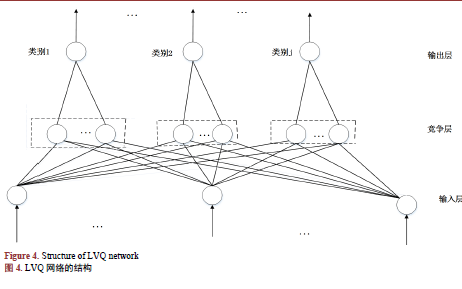

如何使用LVQ进行普米语语谱图的识别说明

本文使用基于学习向量量化算法实现了对普米语语谱图的识别。该算法首先通过傅立叶变换绘制出每条普米语语料的语谱图;再次,提取每张语谱图的图像灰度

发表于 01-22 10:38

•7次下载

Xilinx源语-------FDRE

FDRE代表一个单D型触发器,含的有五个信号分别为: 数据(data,D)、时钟使能(Clock enable,CE)、时钟(Clock)、同步复位(synchronous reset,R)、数据

发表于 01-25 07:27

•3次下载

xilinx源语中IDDR和ODDR介绍

1 IDDR 1.1 介绍 该设计元素是专用的输入寄存器,旨在将外部双数据速率(DDR)信号接收到Xilinx FPGA中。IDDR可用的模式可以在捕获数据的时间和时钟沿或在相同的时钟沿向

Xilinx无源适配器的原理、特点及应用

在测试和验证电子设备时,供电问题常常是一个关键的挑战。作为一家领先的可编程逻辑器件制造商,为了帮助客户解决供电问题,推出了一种创新的解决方案——Xilinx无源适配器。

Xilinx源语---FDRE

Xilinx源语---FDRE

评论