原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目录为“ps_hello/vivado”

前面的实验都是在PL端进行的,可以看到和普通FPGA开发流程没有任何区别,ZYNQ的主要优势就是FPGA和ARM的合理结合,这对开发人员提出了更高的要求。从本章开始,我们开始使用ARM,也就是我们说的PS,本章我们使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性。

前面的实验都是FPGA工程师应该做的事情,从本章节开始就有了分工,FPGA工程师负责把Vivado工程搭建好,提供好硬件给软件开发人员,软件开发人员便能在这个基础上开发应用程序。做好分工,也有利于项目的推进。如果是软件开发人员想把所有的事情都做了,可能需要花费很多时间和精力去学习FPGA的知识,由软件思维转成硬件思维是个比较痛苦的过程,如果纯粹的学习,又有时间,就另当别论了。专业的人做专业的事,是个很好的选择。

1. 硬件介绍

我们从原理图中可以看到ZYNQ芯片分为PL和PS,PS端的IO分配相对是固定的,不能任意分配,而且不需要在Vivado软件里分配管脚,虽然本实验仅仅使用了PS,但是还要建立一个Vivado工程,用来配置PS管脚。虽然PS端的ARM是硬核,但是在ZYNQ当中也要将ARM硬核添加到工程当中才能使用。前面章节介绍的是代码形式的工程,本章开始介绍ZYNQ的图形化方式建立工程。

FPGA工程师工作内容

下面介绍FPGA工程师负责内容。

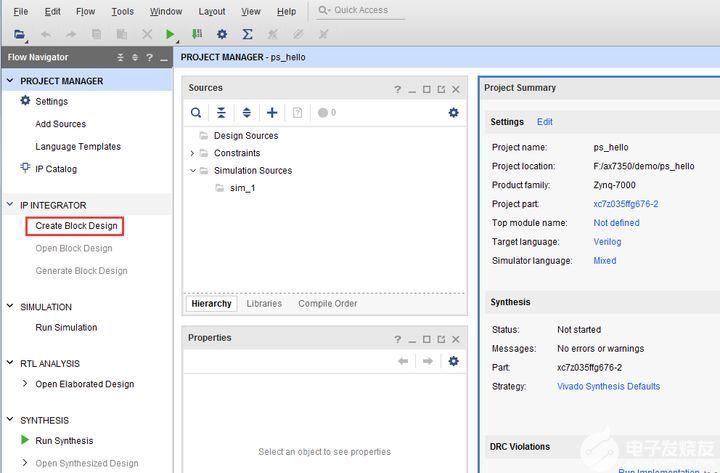

2. Vivado工程建立

2.1 创建一个名为“ps_hello”的工程,建立过程不再赘述,参考“PL的”Hello World”LED实验”。

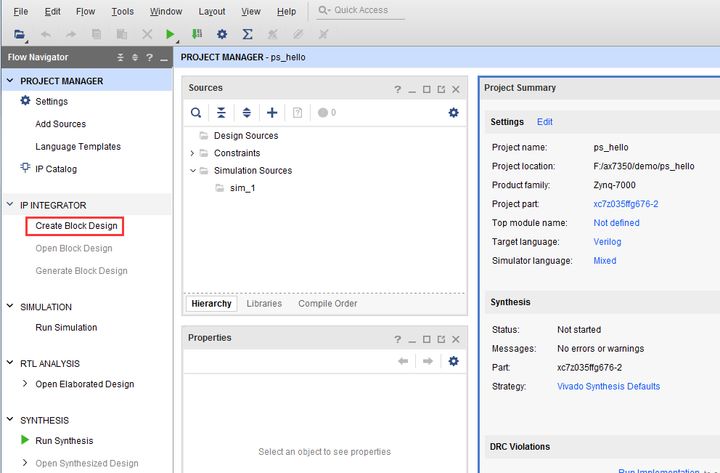

2.2 点击“Create Block Design”,创建一个Block设计,也就是图形化设计

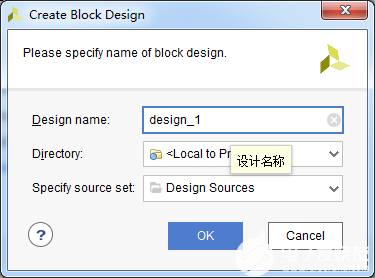

2.3 “Design name”这里不做修改,保持默认“design_1”,这里可以根据需要修改,不过名字要尽量简短,否则在Windows下编译会有问题。

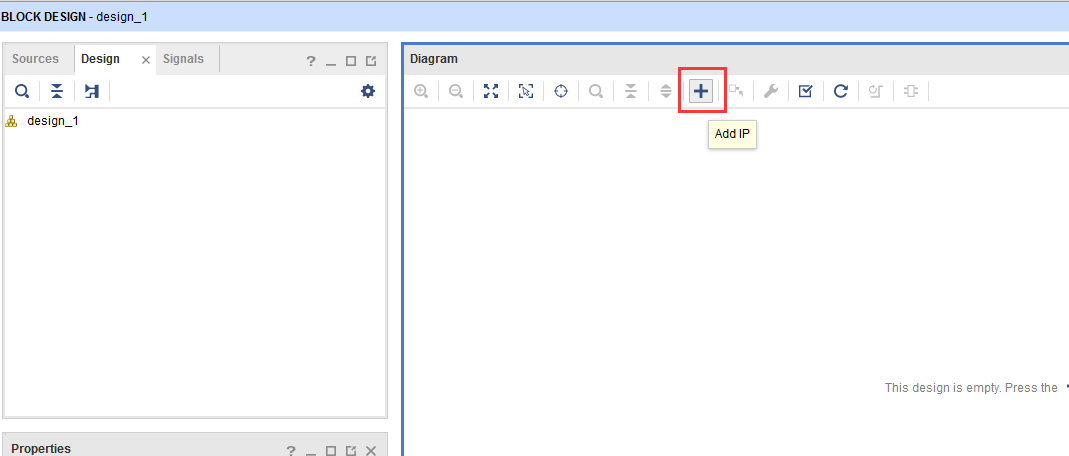

2.4 点击“Add IP”快捷图标

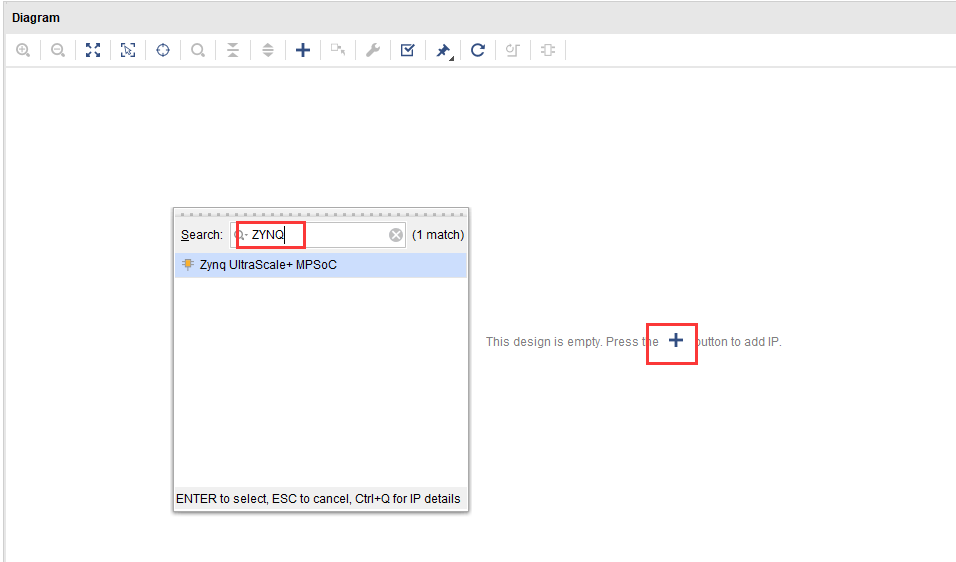

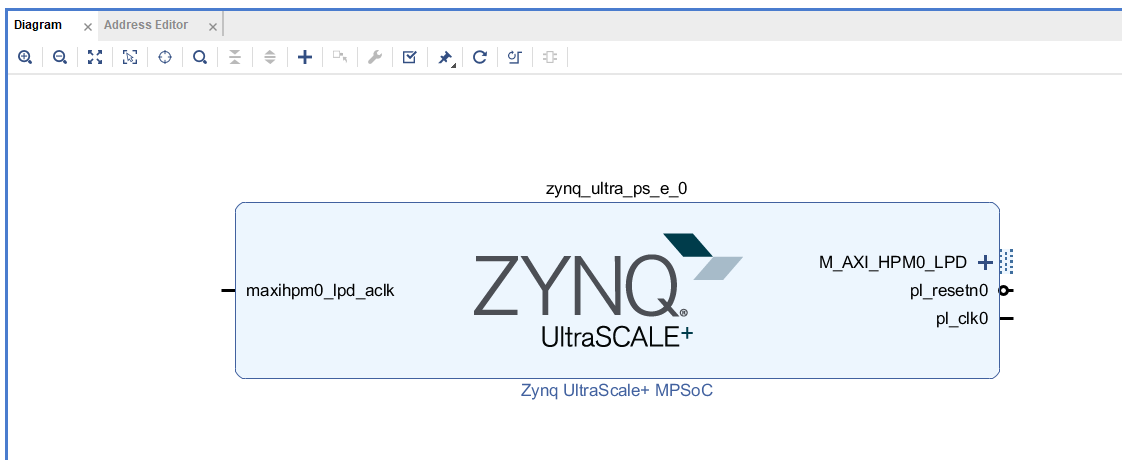

2.5 搜索“zynq”,在搜索结果列表中双击”Zynq UltraScale+ MPSoC”

2.6 双击Block图中的ZYNQ核,配置相关参数

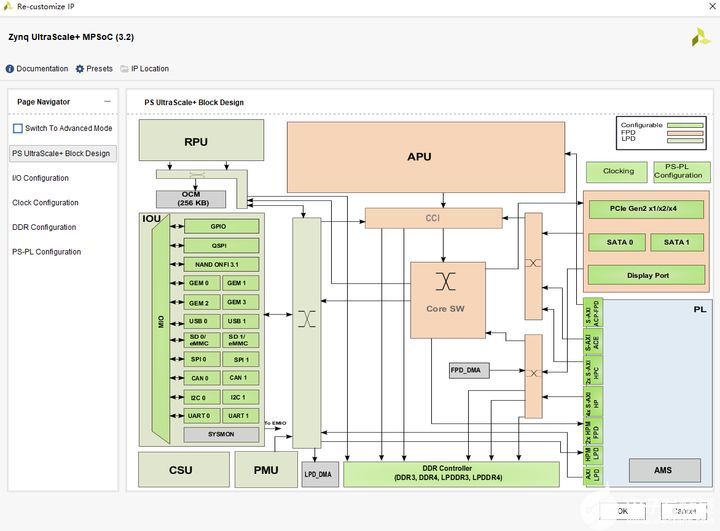

2.7 首先出现的界面是ZYNQ硬核的架构图,可以很清楚看到它的结构,可以参考ug1085文档,里面有对ZYNQ的详细介绍。图中绿色部分是可配置模块,可以点击进入相应的编辑界面,当然也可以在左侧的窗口进入编辑。下面对各个窗口的功能一一介绍。

2.7.1 Low Speed配置

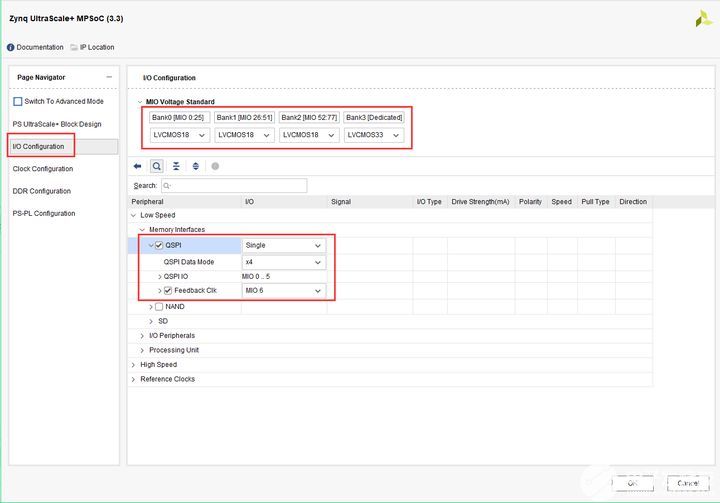

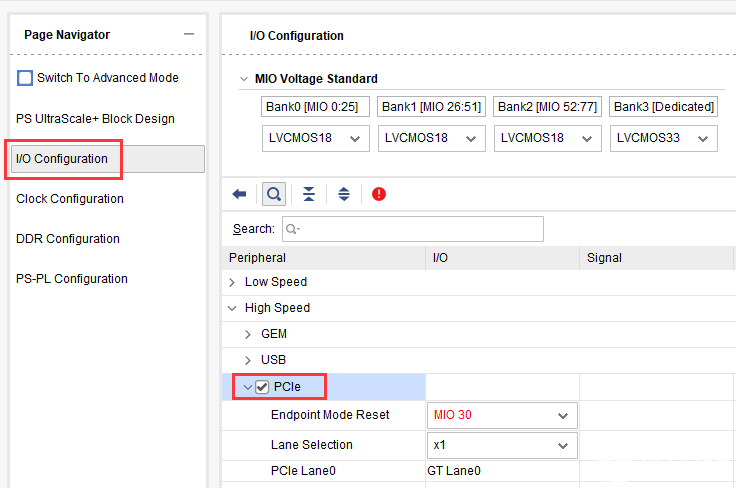

1) 在I/O Configuration窗口,配置BANK0~BANK2电压为LVCMOS18,BANK3电压为LVCMOS33。首先配置Low Speed管脚,勾选QSPI,并设置为”Single”模式,Data Mode为”x4“,勾选Feedback Clk

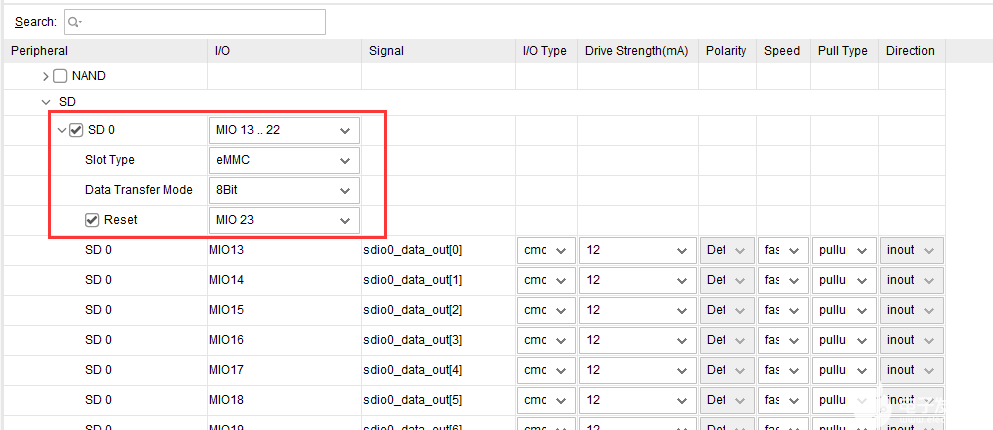

2) (AXU2CGA开发板没有EMMC,不需要勾选此项)勾选SD 0,配置eMMC。选择MIO13..22,Slot Type选择eMMC,Data Transfer Mode为8Bit,勾选Reset,并选择MIO23。

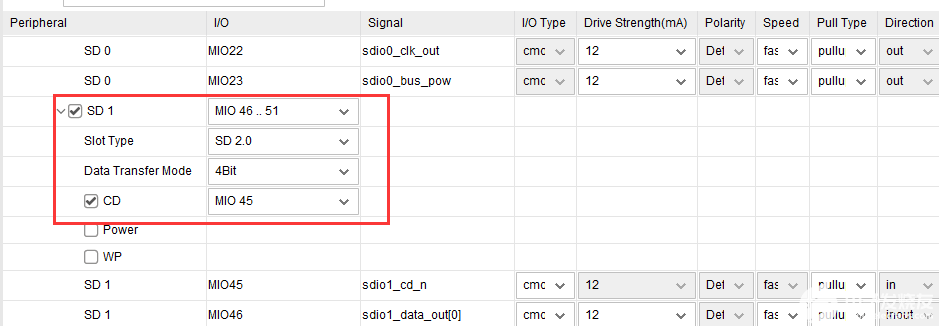

3) 勾选SD 1,配置SD卡。选择MIO 46..51,Slot Type选择SD 2.0,Data Transfer Mode选择4Bit,勾选CD,用于检测SD卡插入,选择MIO45

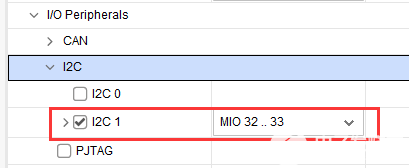

4) 勾选I2C 1,用于EEPROM等的I2C,选择MIO 32..33

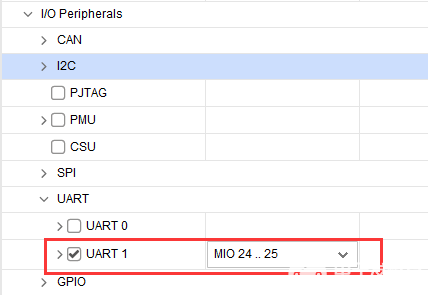

5) 勾选串口UART 1,选择MIO 42..43

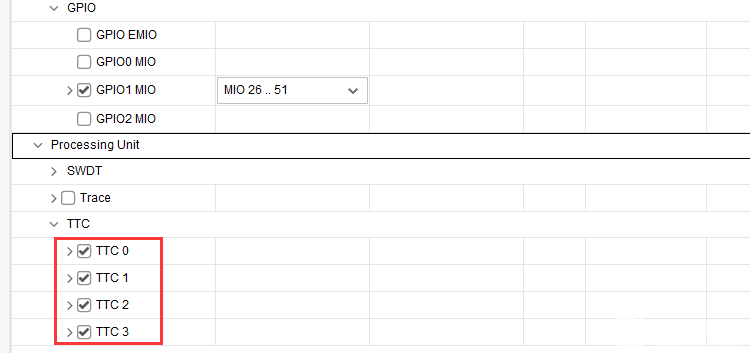

6) 勾选TTC0~TTC 3

2.7.2High Speed配置

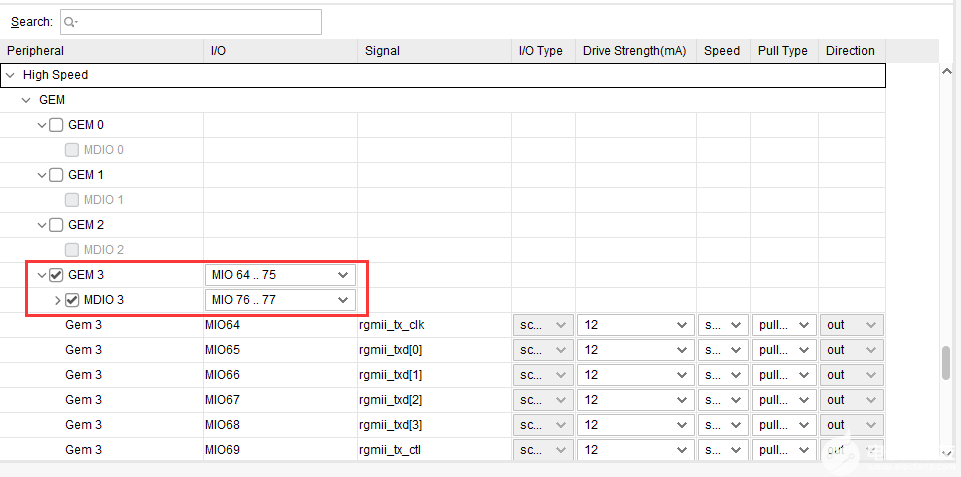

1) High Speed部分首先配置PS端以太网,勾选GEM 3,选择MIO 64..75,勾选MDIO 3,选择MIO 76..77

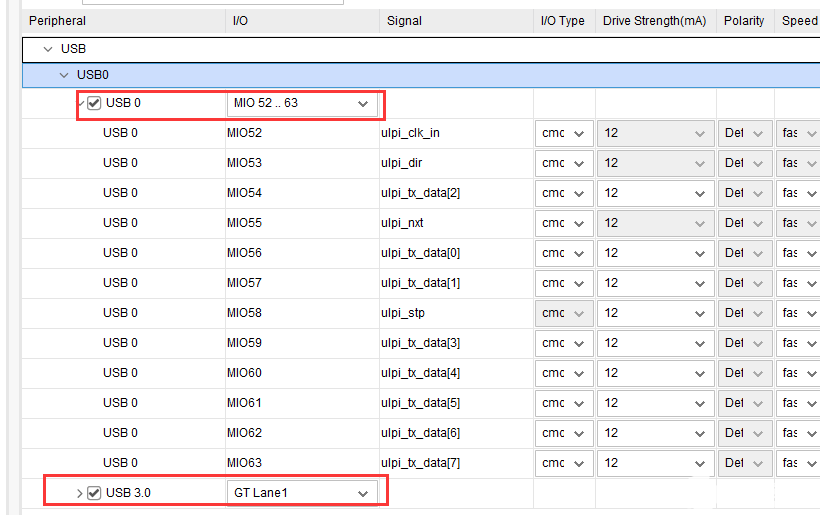

2) 勾选USB 0,选择MIO 52..63,勾选USB 3.0,选择GT Lane1

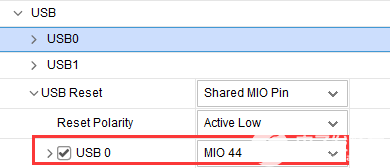

USB复位选择MIO 31

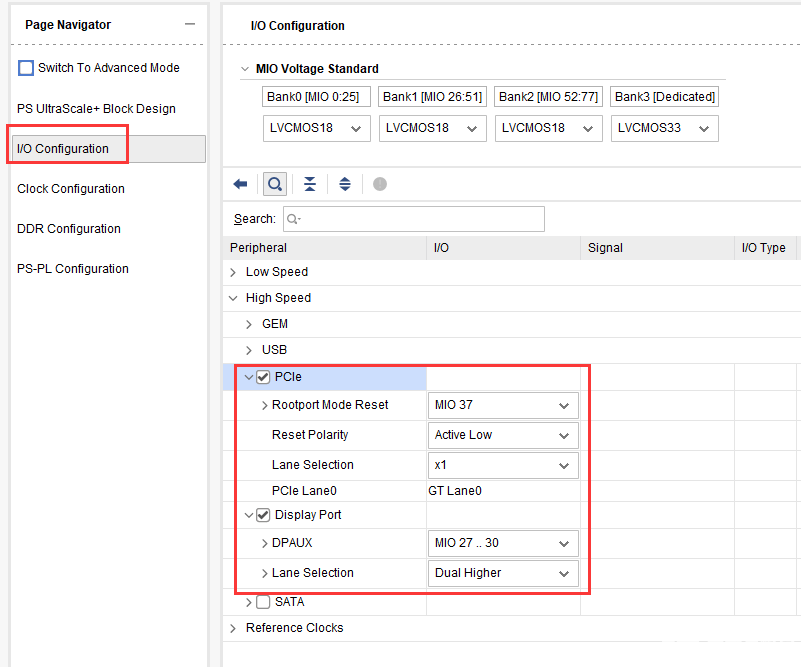

3) 勾选PCIe

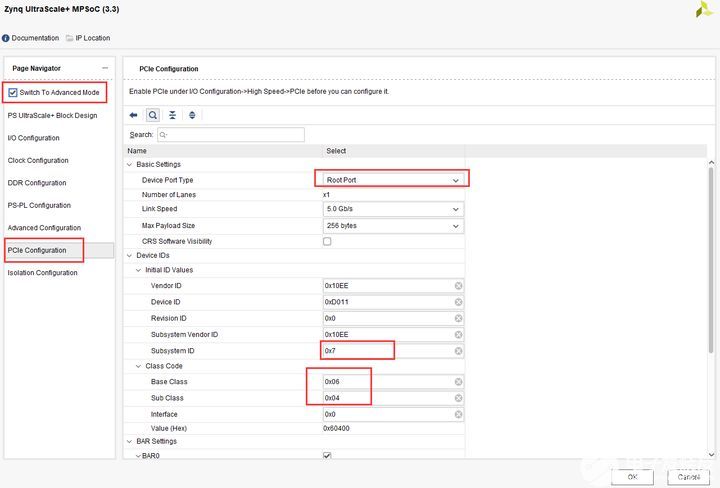

4) 点开Switch To Advanced Mode,选择PCIe Configuration,修改以下几个参数,配置为ROOT模式

5) 回到I/O Configuration,选择GT Lane0,复位选择MIO 37;勾选Display Port,选择MIO 27..30,Lane Selection选择Dual Higher

至此,I/O部分配置完毕

2.7.3 时钟配置

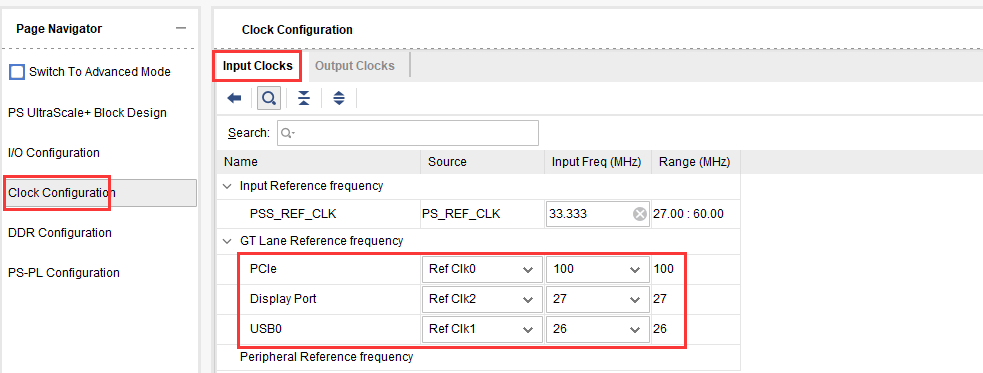

1) 在Clock Configuration界面,Input Clocks窗口配置参考时钟,其中PSS_REF_CLOCK为ARM的参考时钟默认为33.333MHz;PCIe选择Ref Clk0,100MHz;Display Port选择Ref Clk2,27MHz;USB0选择Ref Clk1,26MHz。

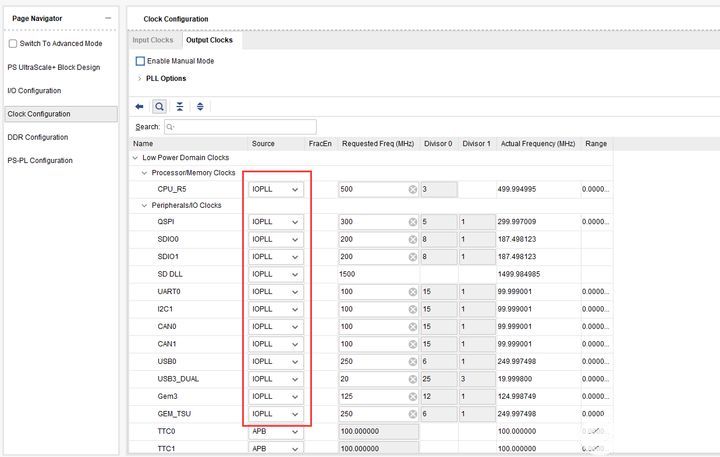

2) 在Output Clocks窗口,如果不是IOPLL,改成IOPLL,保持一致,用同样的PLL

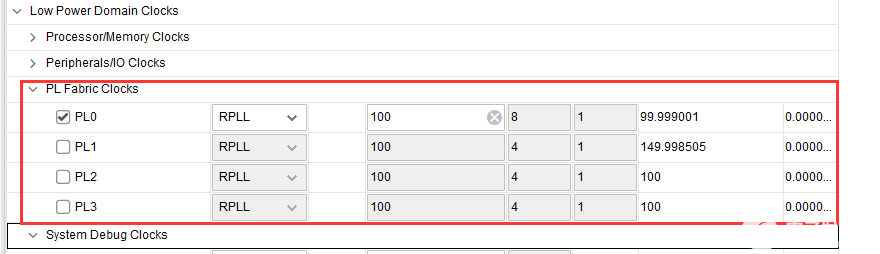

3) PL的时钟保持默认,这是给PL端逻辑提供的时钟。

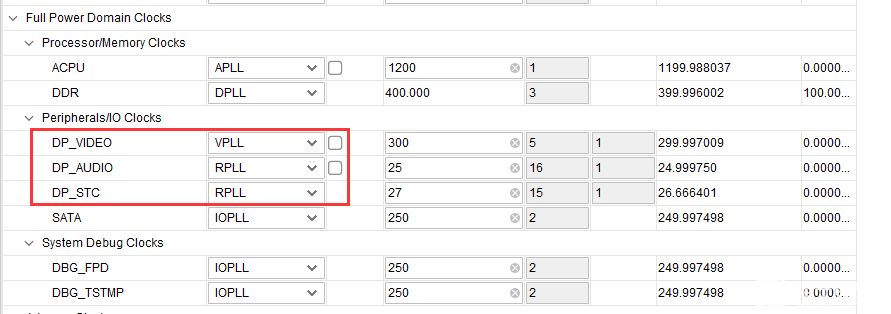

4) Full Power部分,其他保持默认,将DP_VIDEO改为VPLL,DP_AUDIO和DP_STC改为RPLL。

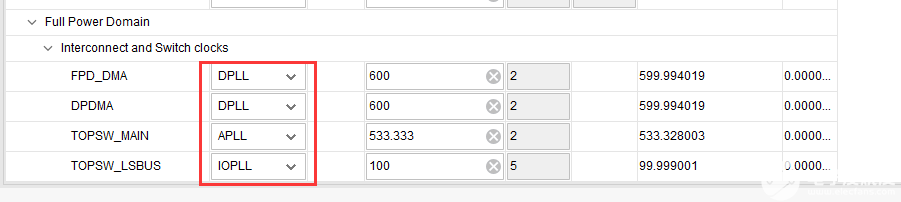

最下面的Interconnect修改如下

其他部分保持默认,至此,时钟部分配置完成。

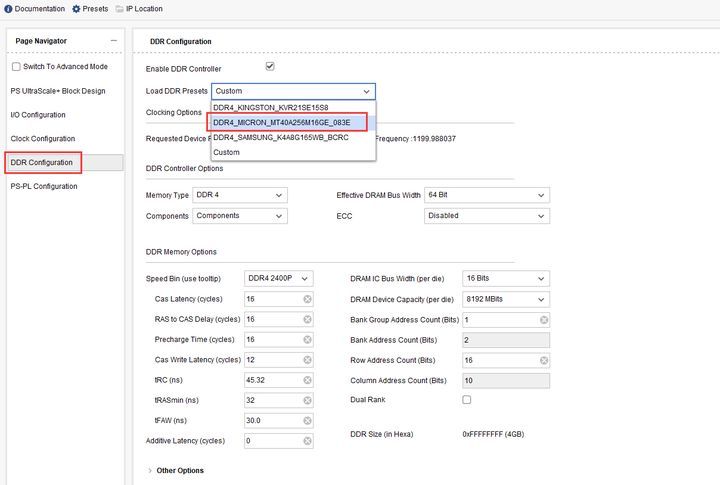

2.7.4 DDR配置

在DDR Configuration窗口中,Load DDR Presets选择”DDR4_MICRON_MT40A256M16GE_083E”

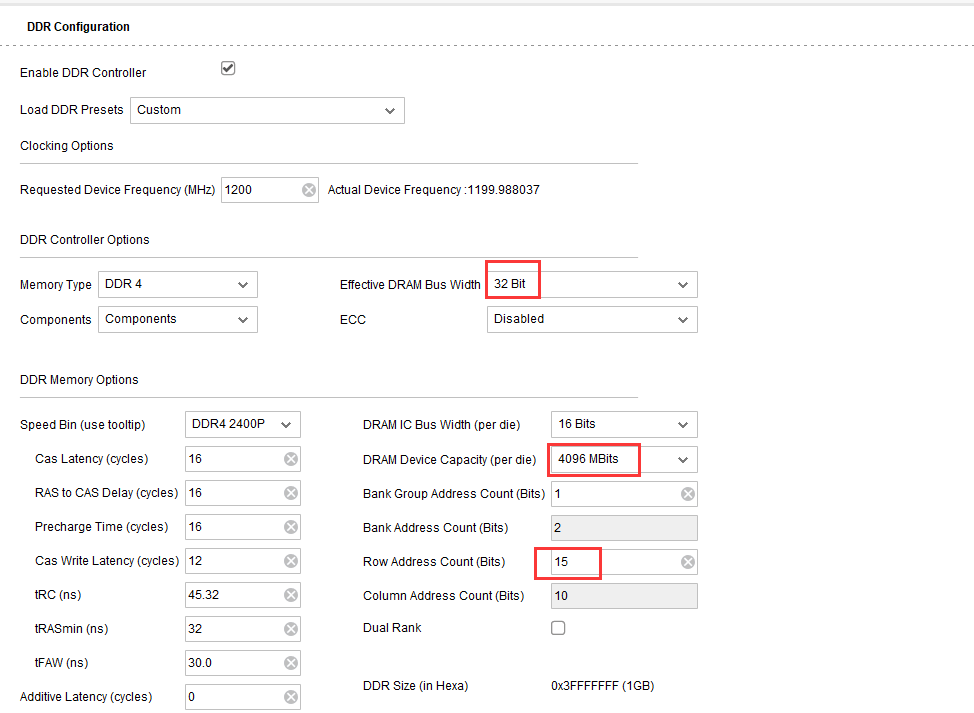

AXU2CGA开发板配置如下:

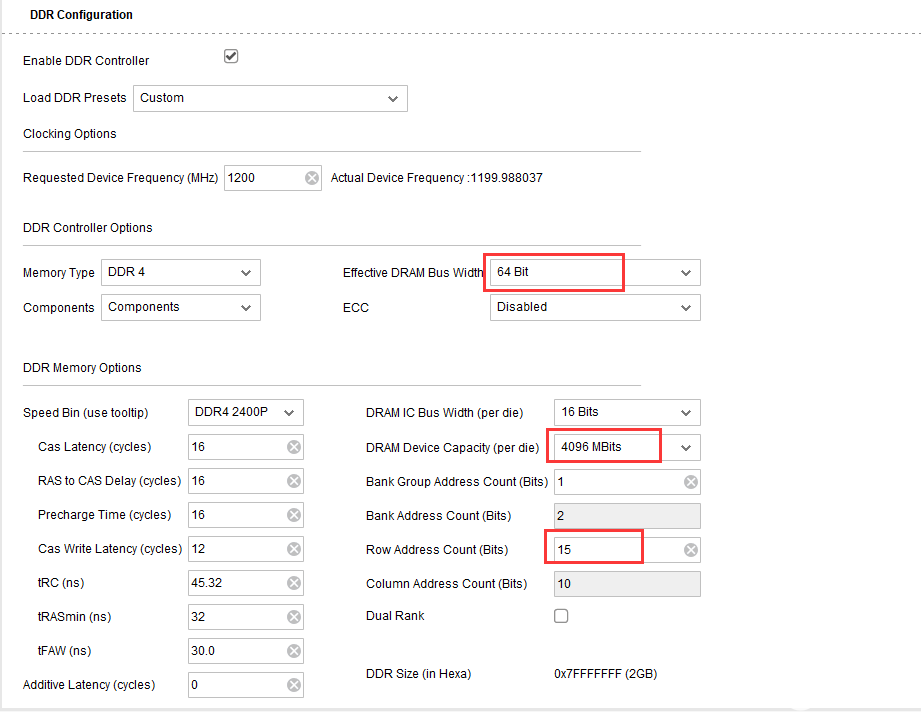

AXU2CGB开发板配置如下:

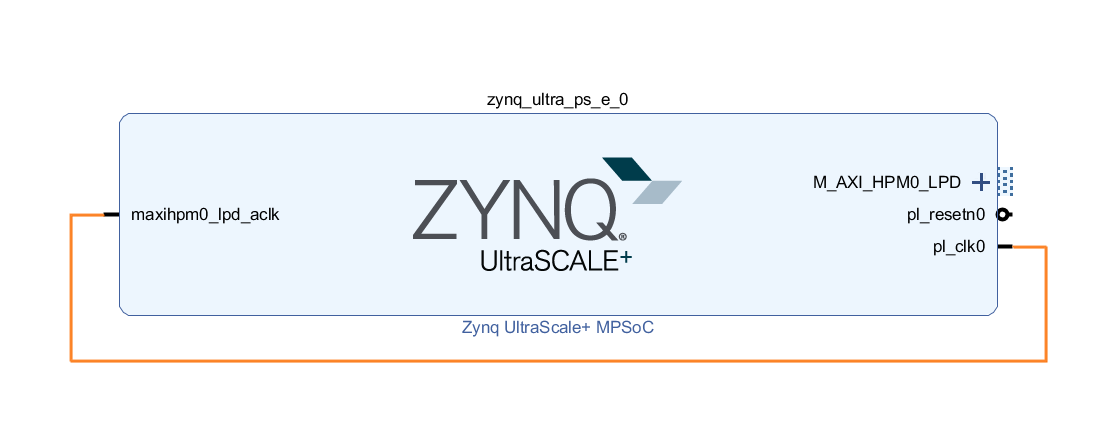

其它保持默认,点击OK,配置完成,并连接时钟如下:

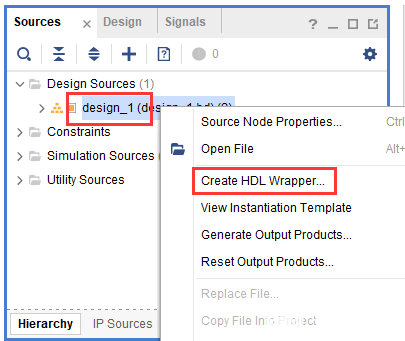

1)选择Block设计,右键“Create HDL Wrapper...”,创建一个Verilog或VHDL文件,为block design生成HDL顶层文件。

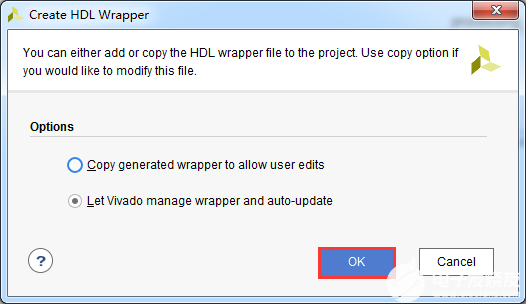

2)保持默认选项,点击“OK”

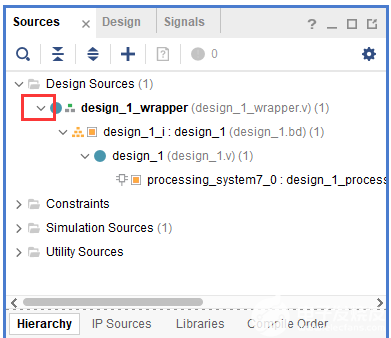

3)展开设计可以看到PS被当成一个普通IP 来使用。

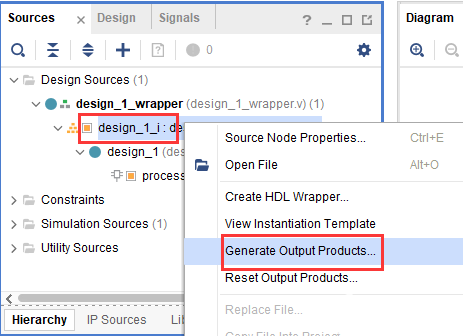

4)选择block设计,右键“Generate Output Products”,此步骤会生成block的输出文件,包括IP,例化模板,RTL源文件,XDC约束,第三方综合源文件等等。供后续操作使用。

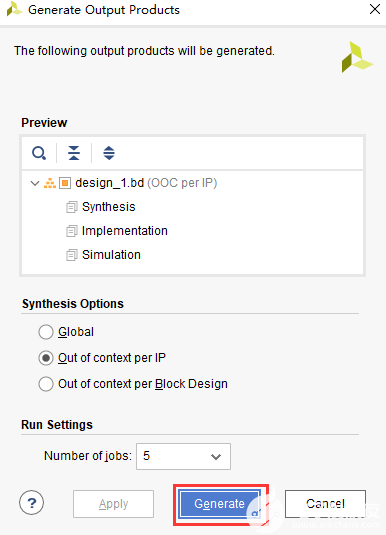

5)点击“Generate”

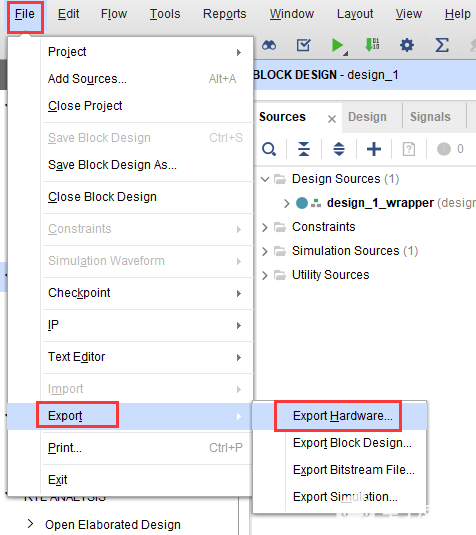

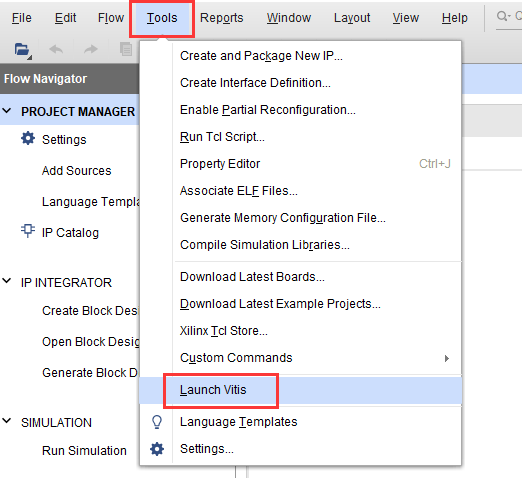

6)在菜单栏“File -> Export -> Export Hardware...”导出硬件信息,这里就包含了PS端的配置信息。

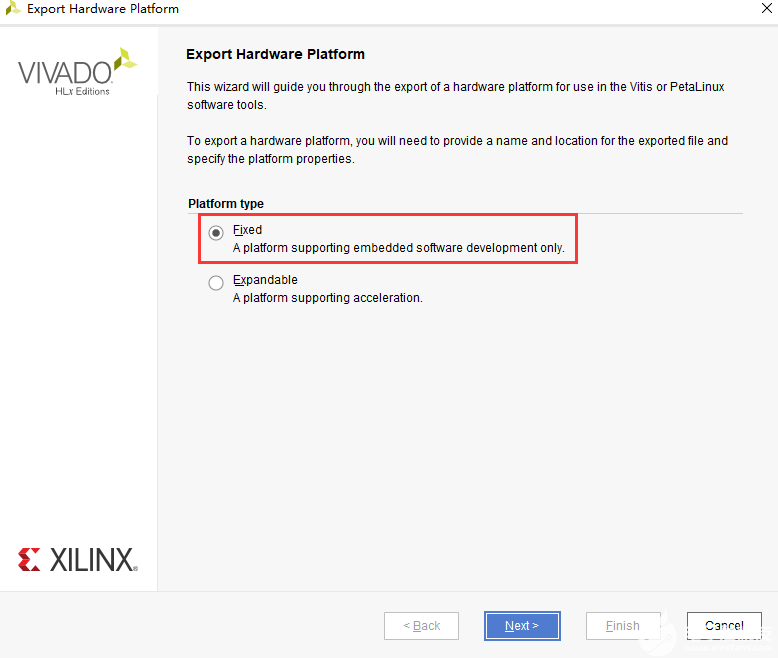

7) 在弹出的窗口中选择Fixed,点击Next

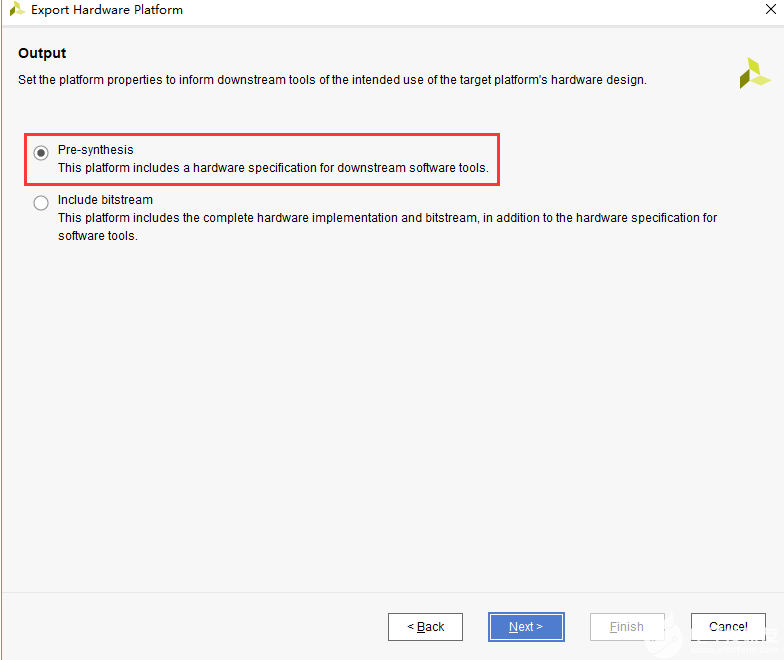

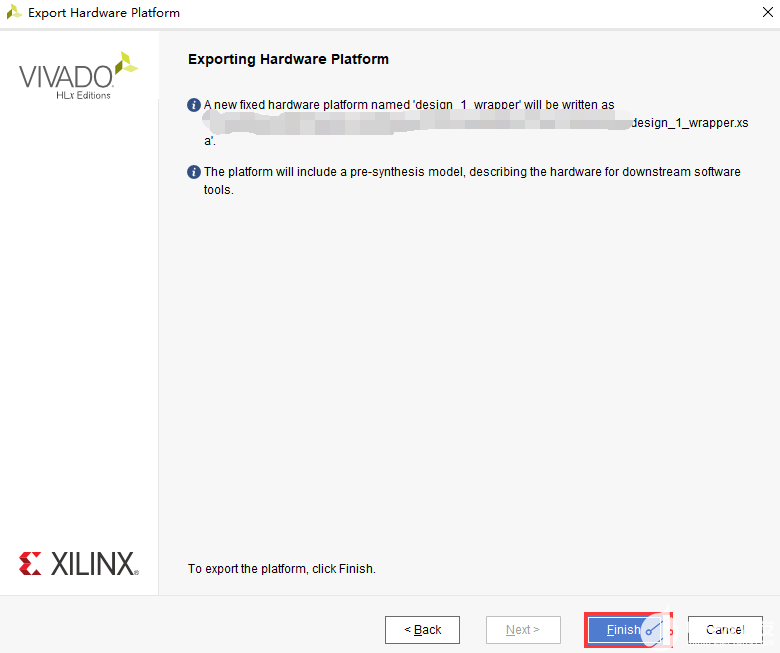

8) 在弹出的对话框中点击“OK”,因为实验仅仅是使用了PS的串口,不需要PL参与,这里就没有使能不选择“Include bitstream”,点击Next

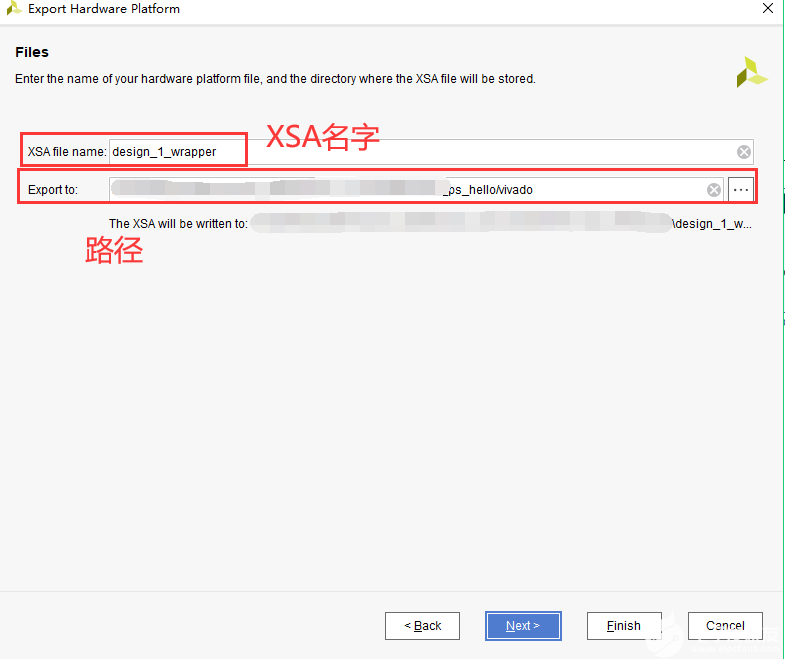

9) 可修改导出名字以及导出路径,默认是在vivado工程目录下的,这个文件可以根据自己的需要在合适的位置,不一定要放在vivado工程下面,vivado和vitis软件是独立的。在这里我们选择默认不做更改。点击Next

点击Finish

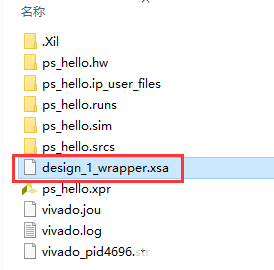

此时在工程目录下可以看到xsa文件,这个文件就是这个文件就包含了Vivado硬件设计的信息,可交由软件开发人员使用。

到此为止,FPGA工程师工作告一段落。

-

FPGA

+关注

关注

1630文章

21780浏览量

604911 -

ARM

+关注

关注

134文章

9147浏览量

368400 -

工程师

+关注

关注

59文章

1571浏览量

68579 -

Zynq

+关注

关注

10文章

610浏览量

47237 -

MPSoC

+关注

关注

0文章

199浏览量

24303

发布评论请先 登录

相关推荐

我的hello world(基于米尔MPSOC开发板)

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

闲话Zynq UltraScale+ MPSoC(连载1)

基于Zynq UltraScale+ MPSoC上运行 Xen 管理程序

Zynq UltraScale+ MPSoC的发售消息

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章Hello World(上)

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计

Zynq UltraScale+ MPSoC的隔离设计示例

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章 Hello World(上)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十八章 Hello World(上)

评论