原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目录为“ps_hello/vivado”

vitis工程目录为“ps_net/vitis”

软件工程师工作内容

以下为软件工程师负责内容。

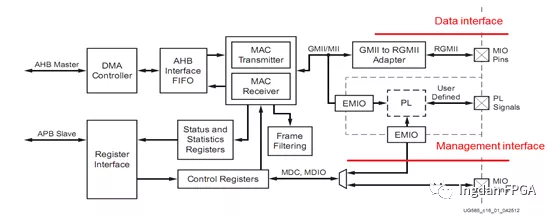

开发板有两路千兆以太网,通过RGMII接口连接,本实验演示如何使用Vitis自带的LWIP模板进行PS端千兆以太网TCP通信。

LWIP虽然是轻量级协议栈,但如果从来没有使用过,使用起来会有一定的困难,建议先熟悉LWIP的相关知识。

1. Vitis程序开发

1.1 LWIP库修改

由于自带的LWIP库只能识别部分phy芯片,如果开发板所用的phy芯片不在默认支持范围内,要修改库文件。也可以直接使用修改过的库替换原有的库。

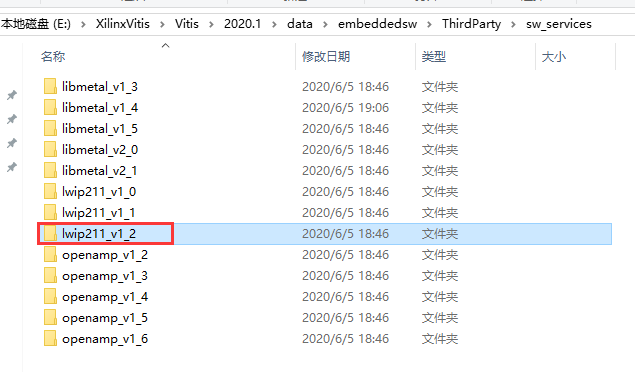

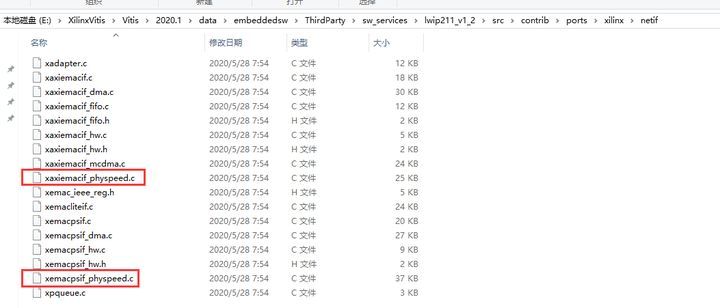

1) 找到库文件目录“X:\xxx\Vitis\2020.1\data\embeddedsw\ThirdParty\sw_services”

2)找到要修改的文件目录“lwip211_v1_2\src\contrib\ports\xilinx\netif”中文件“xaxiemacif_physpeed.c”和“xemacpsif_physpeed.c”要修改。

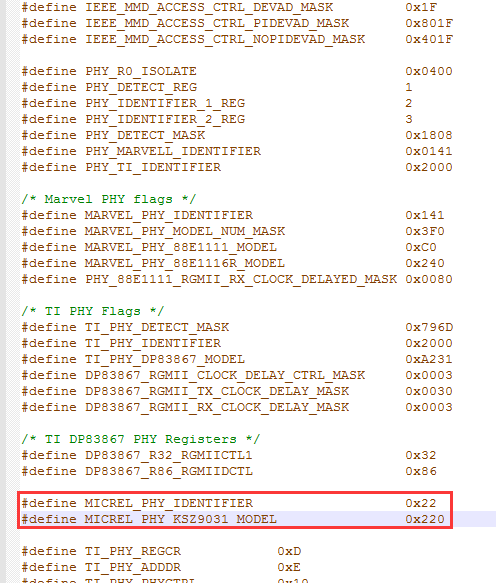

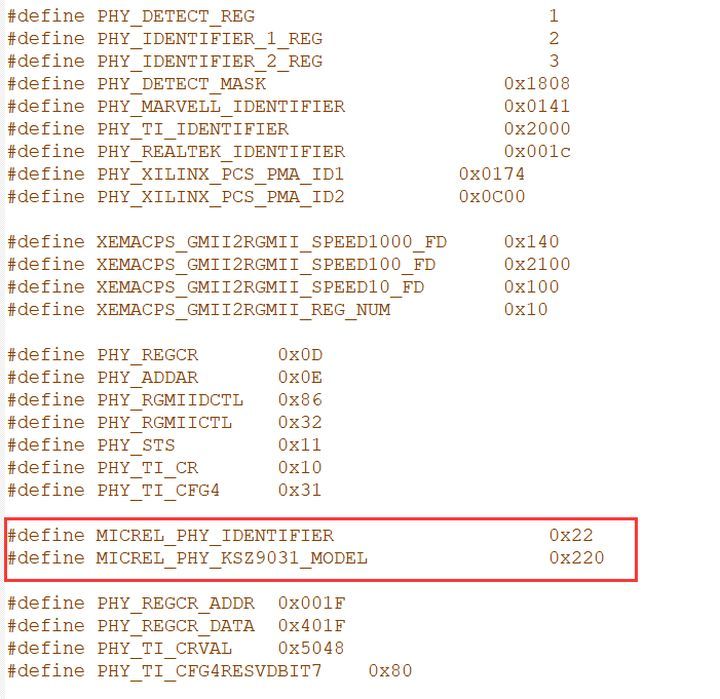

3)修改PL端的“xaxiemacif_physpeed.c”文件,添加相关宏定义

4)添加phy速度获取函数

unsignedintget_phy_speed_ksz9031(XAxiEthernet*xaxiemacp,u32phy_addr){ u16control; u16status; u16partner_capabilities; xil_printf("StartPHYautonegotiation\r\n"); XAxiEthernet_PhyWrite(xaxiemacp,phy_addr,IEEE_PAGE_ADDRESS_REGISTER,2); XAxiEthernet_PhyRead(xaxiemacp,phy_addr,IEEE_CONTROL_REG_MAC,&control); //control|=IEEE_RGMII_TXRX_CLOCK_DELAYED_MASK; control&=~(0x10); XAxiEthernet_PhyWrite(xaxiemacp,phy_addr,IEEE_CONTROL_REG_MAC,control); XAxiEthernet_PhyWrite(xaxiemacp,phy_addr,IEEE_PAGE_ADDRESS_REGISTER,0); XAxiEthernet_PhyRead(xaxiemacp,phy_addr,IEEE_AUTONEGO_ADVERTISE_REG,&control); control|=IEEE_ASYMMETRIC_PAUSE_MASK; control|=IEEE_PAUSE_MASK; control|=ADVERTISE_100; control|=ADVERTISE_10; XAxiEthernet_PhyWrite(xaxiemacp,phy_addr,IEEE_AUTONEGO_ADVERTISE_REG,control); XAxiEthernet_PhyRead(xaxiemacp,phy_addr,IEEE_1000_ADVERTISE_REG_OFFSET, &control); control|=ADVERTISE_1000; XAxiEthernet_PhyWrite(xaxiemacp,phy_addr,IEEE_1000_ADVERTISE_REG_OFFSET, control); XAxiEthernet_PhyWrite(xaxiemacp,phy_addr,IEEE_PAGE_ADDRESS_REGISTER,0); XAxiEthernet_PhyRead(xaxiemacp,phy_addr,IEEE_COPPER_SPECIFIC_CONTROL_REG, &control); control|=(7<<12); /* max number of gigabit attempts */ control |=(1<<11); /* enable downshift */ XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_COPPER_SPECIFIC_CONTROL_REG, control); XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET,&control); control |= IEEE_CTRL_AUTONEGOTIATE_ENABLE; control |= IEEE_STAT_AUTONEGOTIATE_RESTART; XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET, control); XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET,&control); control |= IEEE_CTRL_RESET_MASK; XAxiEthernet_PhyWrite(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET, control); while(1){ XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_CONTROL_REG_OFFSET,&control); if(control & IEEE_CTRL_RESET_MASK) continue; else break; } xil_printf("Waiting for PHY to complete autonegotiation.\r\n"); XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_STATUS_REG_OFFSET,&status); while(!(status & IEEE_STAT_AUTONEGOTIATE_COMPLETE)){ sleep(1); XAxiEthernet_PhyRead(xaxiemacp, phy_addr, IEEE_STATUS_REG_OFFSET, &status); } xil_printf("autonegotiation complete \r\n"); XAxiEthernet_PhyRead(xaxiemacp, phy_addr,0x1f,&partner_capabilities); if((partner_capabilities &0x40)==0x40)/* 1000Mbps */ return1000; elseif((partner_capabilities &0x20)==0x20)/* 100Mbps */ return100; elseif((partner_capabilities &0x10)==0x10)/* 10Mbps */ return10; else return0;}

5) 修改函数“get_IEEE_phy_speed”,添加对KSZ9031的支持。

unsignedget_IEEE_phy_speed(XAxiEthernet*xaxiemacp){

u16phy_identifier;

u16phy_model;

u8phytype;#ifdefXPAR_AXIETHERNET_0_BASEADDR

u32phy_addr=detect_phy(xaxiemacp);

/*GetthePHYIdentifierandModelnumber*/

XAxiEthernet_PhyRead(xaxiemacp,phy_addr,PHY_IDENTIFIER_1_REG,&phy_identifier);

XAxiEthernet_PhyRead(xaxiemacp,phy_addr,PHY_IDENTIFIER_2_REG,&phy_model);/*DependinguponwhatmanufacturerPHYisconnected,adifferentmaskis*neededtodeterminethespecificmodelnumberofthePHY.*/

if(phy_identifier==MARVEL_PHY_IDENTIFIER){

phy_model=phy_model&MARVEL_PHY_MODEL_NUM_MASK;

if(phy_model==MARVEL_PHY_88E1116R_MODEL){

returnget_phy_speed_88E1116R(xaxiemacp,phy_addr);

}elseif(phy_model==MARVEL_PHY_88E1111_MODEL){

returnget_phy_speed_88E1111(xaxiemacp,phy_addr);

}

}elseif(phy_identifier==TI_PHY_IDENTIFIER){

phy_model=phy_model&TI_PHY_DP83867_MODEL;

phytype=XAxiEthernet_GetPhysicalInterface(xaxiemacp);

if(phy_model==TI_PHY_DP83867_MODEL&&phytype==XAE_PHY_TYPE_SGMII){

returnget_phy_speed_TI_DP83867_SGMII(xaxiemacp,phy_addr);

}

if(phy_model==TI_PHY_DP83867_MODEL){

returnget_phy_speed_TI_DP83867(xaxiemacp,phy_addr);

}

}

elseif(phy_identifier==MICREL_PHY_IDENTIFIER)

{

xil_printf("Phy%disKSZ9031\n\r",phy_addr);

get_phy_speed_ksz9031(xaxiemacp,phy_addr);

}

else{

LWIP_DEBUGF(NETIF_DEBUG,("XAxiEthernetget_IEEE_phy_speed:DetectedPHYwithunknownidentifier/model.\r\n"));

}#endif#ifdefPCM_PMA_CORE_PRESENT

returnget_phy_negotiated_speed(xaxiemacp,phy_addr);#endif}

6) 修改PS端“xemacpsif_physpeed.c”文件添加宏定义

7) 添加phy速度获取函数

staticu32_tget_phy_speed_ksz9031(XEmacPs*xemacpsp,u32_tphy_addr){

u16_ttemp;

u16_tcontrol;

u16_tstatus;

u16_tstatus_speed;

u32_ttimeout_counter=0;

u32_ttemp_speed;

u32_tphyregtemp;

xil_printf("StartPHYautonegotiation\r\n");

XEmacPs_PhyWrite(xemacpsp,phy_addr,IEEE_PAGE_ADDRESS_REGISTER,2);

XEmacPs_PhyRead(xemacpsp,phy_addr,IEEE_CONTROL_REG_MAC,&control);

control|=IEEE_RGMII_TXRX_CLOCK_DELAYED_MASK;

XEmacPs_PhyWrite(xemacpsp,phy_addr,IEEE_CONTROL_REG_MAC,control);

XEmacPs_PhyWrite(xemacpsp,phy_addr,IEEE_PAGE_ADDRESS_REGISTER,0);

XEmacPs_PhyRead(xemacpsp,phy_addr,IEEE_AUTONEGO_ADVERTISE_REG,&control);

control|=IEEE_ASYMMETRIC_PAUSE_MASK;

control|=IEEE_PAUSE_MASK;

control|=ADVERTISE_100;

control|=ADVERTISE_10;

XEmacPs_PhyWrite(xemacpsp,phy_addr,IEEE_AUTONEGO_ADVERTISE_REG,control);

XEmacPs_PhyRead(xemacpsp,phy_addr,IEEE_1000_ADVERTISE_REG_OFFSET,

&control);

control|=ADVERTISE_1000;

XEmacPs_PhyWrite(xemacpsp,phy_addr,IEEE_1000_ADVERTISE_REG_OFFSET,

control);

XEmacPs_PhyWrite(xemacpsp,phy_addr,IEEE_PAGE_ADDRESS_REGISTER,0);

XEmacPs_PhyRead(xemacpsp,phy_addr,IEEE_COPPER_SPECIFIC_CONTROL_REG,

&control);

control|=(7<<12); /* max number of gigabit attempts */

control |=(1<<11); /* enable downshift */

XEmacPs_PhyWrite(xemacpsp, phy_addr, IEEE_COPPER_SPECIFIC_CONTROL_REG,

control);

XEmacPs_PhyRead(xemacpsp, phy_addr, IEEE_CONTROL_REG_OFFSET,&control);

control |= IEEE_CTRL_AUTONEGOTIATE_ENABLE;

control |= IEEE_STAT_AUTONEGOTIATE_RESTART;

XEmacPs_PhyWrite(xemacpsp, phy_addr, IEEE_CONTROL_REG_OFFSET, control);

XEmacPs_PhyRead(xemacpsp, phy_addr, IEEE_CONTROL_REG_OFFSET,&control);

control |= IEEE_CTRL_RESET_MASK;

XEmacPs_PhyWrite(xemacpsp, phy_addr, IEEE_CONTROL_REG_OFFSET, control);

while(1){

XEmacPs_PhyRead(xemacpsp, phy_addr, IEEE_CONTROL_REG_OFFSET,&control);

if(control & IEEE_CTRL_RESET_MASK)

continue;

else

break;

}

XEmacPs_PhyRead(xemacpsp, phy_addr, IEEE_STATUS_REG_OFFSET,&status);

xil_printf("Waiting for PHY to complete autonegotiation.\r\n");

while(!(status & IEEE_STAT_AUTONEGOTIATE_COMPLETE)){

sleep(1);

XEmacPs_PhyRead(xemacpsp, phy_addr,

IEEE_COPPER_SPECIFIC_STATUS_REG_2,&temp);

timeout_counter++;

if(timeout_counter ==30){

xil_printf("Auto negotiation error \r\n");

return;

}

XEmacPs_PhyRead(xemacpsp, phy_addr, IEEE_STATUS_REG_OFFSET,&status);

}

xil_printf("autonegotiation complete \r\n");

XEmacPs_PhyRead(xemacpsp, phy_addr,0x1f,

&status_speed);

if((status_speed &0x40)==0x40)/* 1000Mbps */

return1000;

elseif((status_speed &0x20)==0x20)/* 100Mbps */

return100;

elseif((status_speed &0x10)==0x10)/* 10Mbps */

return10;

else

return0;

return XST_SUCCESS;}

8)修改函数“get_IEEE_phy_speed”,添加对KSZ9031的支持

staticu32_tget_IEEE_phy_speed(XEmacPs*xemacpsp,u32_tphy_addr){

u16_tphy_identity;

u32_tRetStatus;

XEmacPs_PhyRead(xemacpsp,phy_addr,PHY_IDENTIFIER_1_REG,

&phy_identity);

if(phy_identity==MICREL_PHY_IDENTIFIER){

RetStatus=get_phy_speed_ksz9031(xemacpsp,phy_addr);

}elseif(phy_identity==PHY_TI_IDENTIFIER){

RetStatus=get_TI_phy_speed(xemacpsp,phy_addr);

}elseif(phy_identity==PHY_REALTEK_IDENTIFIER){

RetStatus=get_Realtek_phy_speed(xemacpsp,phy_addr);

}else{

RetStatus=get_Marvell_phy_speed(xemacpsp,phy_addr);

}

returnRetStatus;}

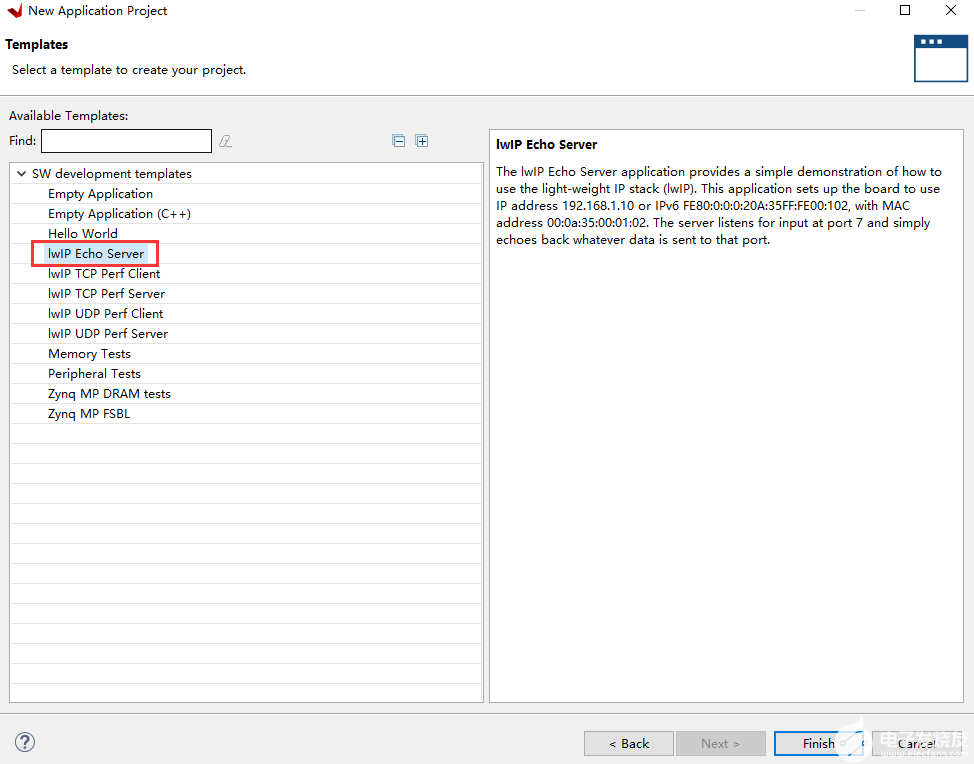

1.2 创建APP工程时基于LWIP模板

2.下载调试

测试环境要求有一台支持dhcp的路由器,开发板连接路由器可以自动获取IP地址,实验主机和开发板在一个网络,可以相互通信。

2.1 以太网测试

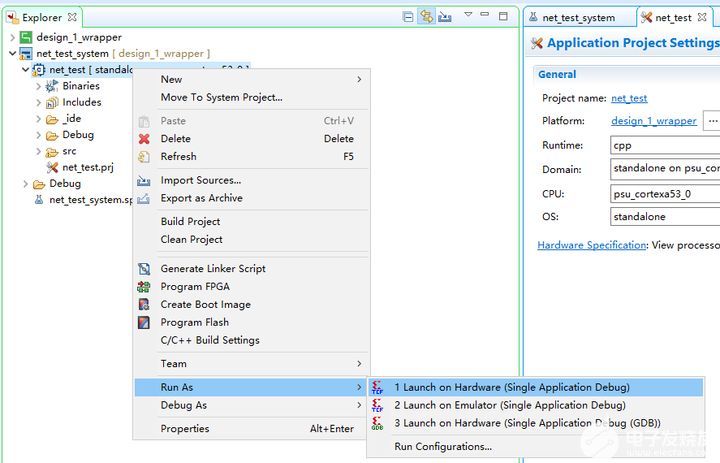

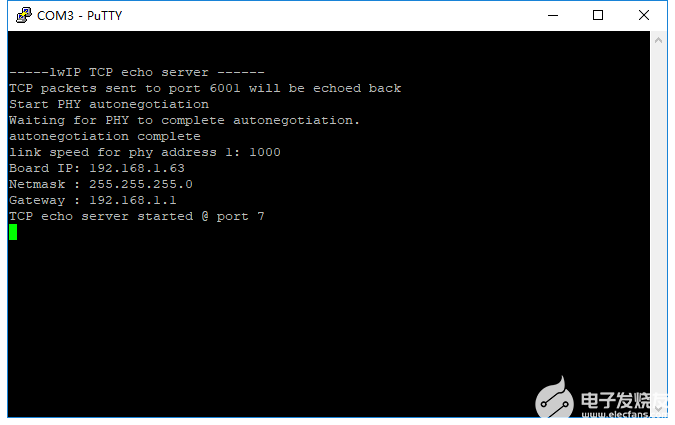

1) 连接串口打开串口调试终端,连接好PS端以太网网线到路由器,运行Vitis下载程序

2)可以看到串口打印出一些信息,可以看到自动获取到地址为“192.168.1.63”,连接速度1000Mbps,tcp端口为7

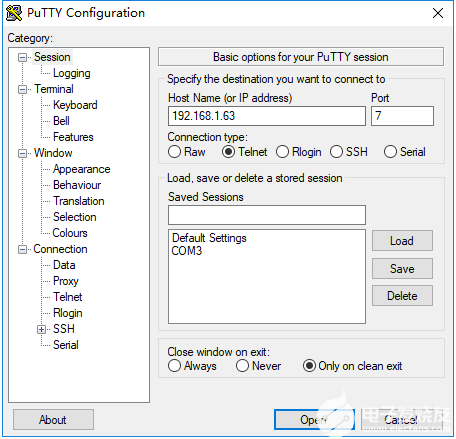

3) 使用telnet连接

4) 当输入一个字符时,开发板返回相同字符

3. 实验总结

通过实验我们更加深刻了解到Vitis程序的开发,本实验只是简单的讲解如何创建一个LWIP应用,LWIP可以完成UDP、TCP等协议,在后续的教程中我们会提供基于以太网的具体应用,例如ADC采集数据通过以太网发送,摄像头数据通过以太网发送上位机显示。

-

FPGA

+关注

关注

1637文章

21841浏览量

608516 -

以太网

+关注

关注

40文章

5487浏览量

173295 -

LwIP

+关注

关注

2文章

88浏览量

27596 -

Zynq

+关注

关注

10文章

612浏览量

47500 -

MPSoC

+关注

关注

0文章

199浏览量

24412

发布评论请先 登录

相关推荐

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

闲话Zynq UltraScale+ MPSoC(连载1)

闲话Zynq UltraScale+ MPSoC(连载5)

Zynq UltraScale+ MPSoC的发售消息

米尔科技Zynq UltraScale+ MPSoC技术参考手册介绍

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

【正点原子FPGA连载】第二十五章HDMI方块移动实验 -摘自【正点原子】新起点之FPGA开发指南_V2.1

Zynq UltraScale+ MPSoC以太网接口调试

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计

Zynq UltraScale+ MPSoC中的隔离方法

Zynq UltraScale+ MPSoC的隔离设计示例

Zynq UltraScale+ MPSoC验证数据手册

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十五章PS端以太网使用之lwip

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十五章PS端以太网使用之lwip

评论