近日,西安紫光国芯半导体有限公司(以下简称“紫光国芯”)在第63届国际电子器件大会(IEDM 2020)上公开发表了技术论文——《采用3D混合键合技术具有34GB/s/1Gb带宽和0.88pJ/b能效接口的异质集成嵌入式LPDDR4/LPDDR4X DRAM》(A Stacked Embedded DRAM Array for LPDDR4/4Xusing Hybrid Bonding 3D Integration with 34GB/s/1Gb 0.88pJ/b Logic-to-MemoryInterface)。该论文的发表,是紫光国芯在超高带宽、超低功耗DRAM方向技术积累和持续创新的最新突破。

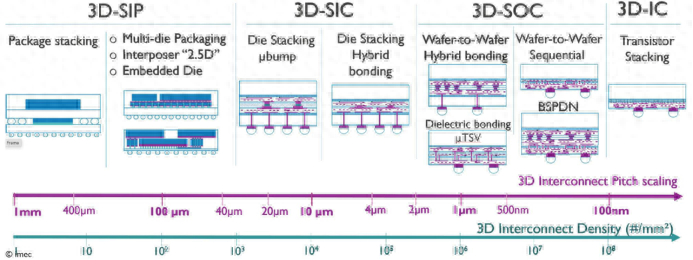

受限于传统计算机体系的冯-诺依曼架构,存储器带宽与计算需求之间的鸿沟(即“存储墙”问题)日益突出。采用硅通孔(TSV)技术的高带宽存储器(HBM)是业界给出的一个可选解决方案,但其每数据管脚的工作频率仍然较高(约4Gbps),存在功耗较大的缺点。比如HBM采用了x10um级微凸块(Micro-Bump)堆叠DRAM,其数据IO数量有限且寄生电容和功耗较大,进而限制了带宽的增加。 西安紫光国芯依托多年对存储器和ASIC体系结构的深入研究,开发完成了异质集成嵌入式DRAM平台(SeDRAM),提供了业界最高的单位带宽和能效,并设计实现了完全兼容国际JEDEC标准的的4Gbit LPDDR4芯片。

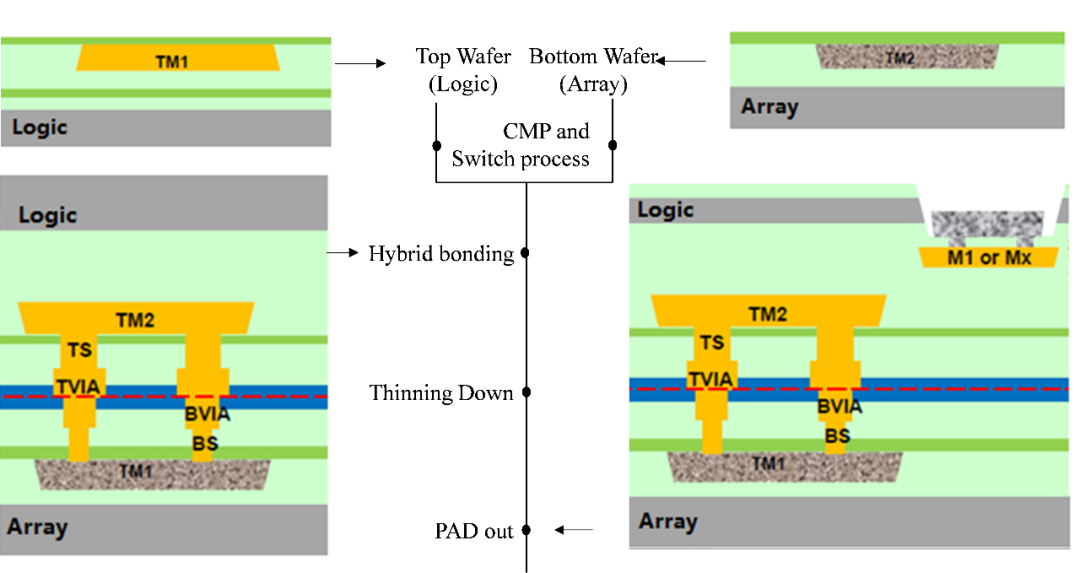

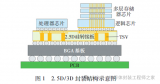

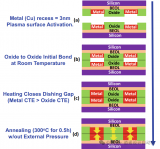

图1. SeDRAM技术流程示意图 紫光国芯在论文中介绍了SeDRAM平台的实现流程(如图1):首先,流片生产不同工艺下的DRAM存储晶圆(DRAM Wafer)和搭载有外围电路的逻辑晶圆(Logic Wafer),并通过平坦化、曝光和刻蚀等异质集成工艺,在两张晶圆上分别制成用于后续步骤的接触孔(LTVIA和LBVIA);然后,将逻辑晶圆翻转,通过 Cu-Cu 互连的方式,将两张晶圆直接键合;最后,将逻辑晶圆减薄至约3um厚度,并从逻辑晶圆背面开口完成PAD制作。 相比于HBM的微凸块(MicroBump)工艺,通过直接键合方式的异质集成工艺,接触孔可达110,000个/mm2,实现了百倍量级的密度提升,而且连接电阻低至0.5欧姆。从而实现了从逻辑电路到存储阵列之间每Gbit高达34GB/s的带宽和0.88pJ/bit的能效。

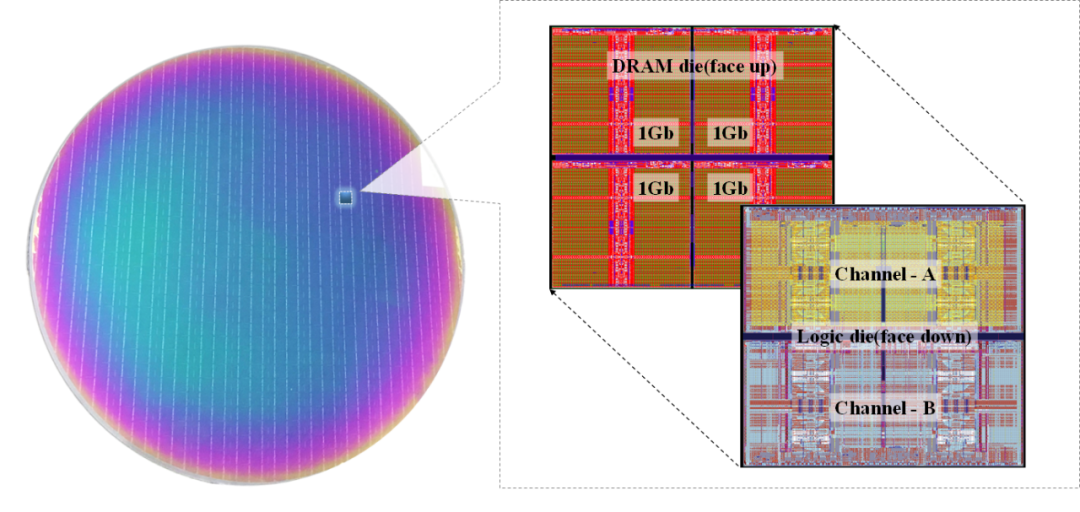

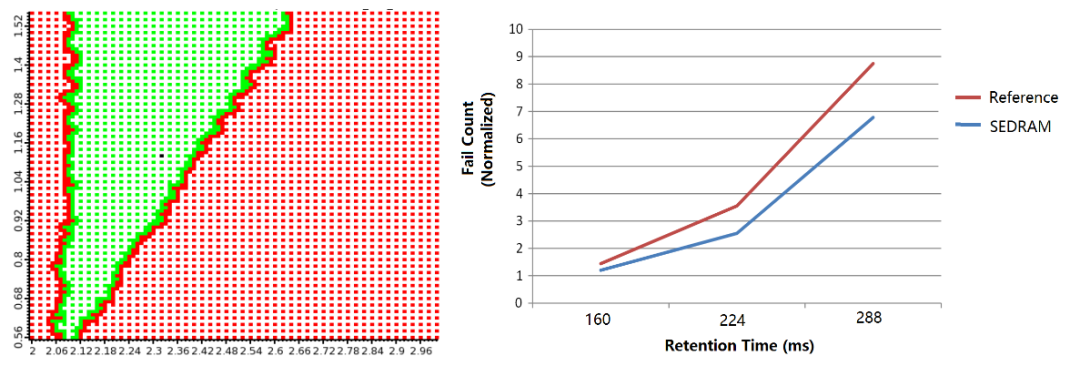

图2. 采用SeDRAM技术开发的4Gb LPDDR4产品的晶圆(左)和版图(右) 紫光国芯开发的4Gbit LPDDR4是业内首款异质集成的标准接口DRAM产品(如图2)。该产品为双通道,数据位宽X16,在每颗芯片中集成超过64,000个异质集成接触孔。在晶圆测试阶段,该产品表现出优异性能,读取时间超过测试机台能支持的最快时钟周期0.56ns。在颗粒测试阶段,该产品在包括高温(95℃),高压(VDD2=1.2v, VDD1=2v)以及低压(VDD2=1.05v, VDD1=1.65v)在内的多个测试条件下,通过了业界最高水平4266Mbps数据率的测试。该产品在高温测试条件下,保持时间达到96ms,与同等DRAM工艺下的传统平面产品相比更具优势。

图3. 4Gb LPDDR4产品的读取时间测试结果(左)和数据保持时间测试结果(右) 感谢武汉新芯和台湾力积电分别支持逻辑芯片及异质集成、和存储芯片代工合作,论文得以在IEDM 2020顺利发表,这是紫光国芯在超高带宽、超低功耗DRAM方向技术积累和持续创新的最新突破。通过4Gbit LPDDR4产品的开发,SeDRAM平台不仅为传统DRAM产品的开发提供了新路径,更为人工智能(AI)和高性能计算(HPC)等领域的高带宽、高能效需求提供了有效解决方案。

原文标题:西安紫光国芯在IEDM 2020发表 异质集成嵌入式DRAM(SeDRAM)论文

文章出处:【微信公众号:西安紫光国芯半导体】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

嵌入式

+关注

关注

5082文章

19123浏览量

305151 -

DRAM

+关注

关注

40文章

2315浏览量

183483 -

存储器

+关注

关注

38文章

7492浏览量

163829 -

紫光

+关注

关注

2文章

412浏览量

34025

原文标题:西安紫光国芯在IEDM 2020发表 异质集成嵌入式DRAM(SeDRAM)论文

文章出处:【微信号:gh_fb990360bfee,微信公众号:西安紫光国芯半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

紫光国芯:采用3D混合键合技术的异质集成嵌入式DRAM

紫光国芯:采用3D混合键合技术的异质集成嵌入式DRAM

评论