今天我们继续讲解

机制

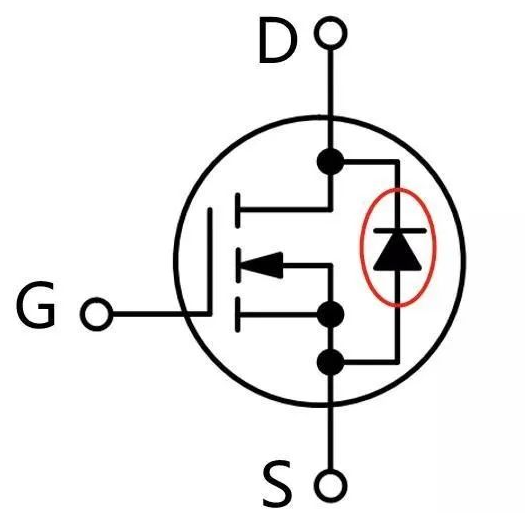

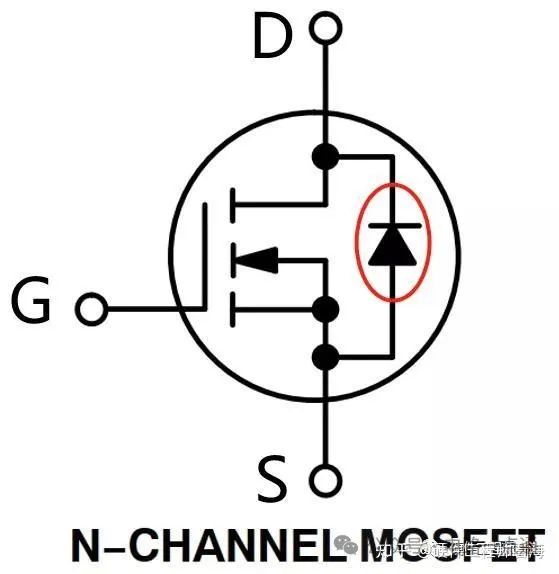

在双极性运行(PN结,比如MOSFET的体二极管,在导电时)条件下,任何类型的SiC器件都可能出现双极退化效应。这种效应主要是由SiC晶体上早先存在的基底面位错(BPD)触发的。在双极运行期间,电子与空穴的复合所释放出的能量导致堆垛层错在BPD处蔓延。该堆垛层错将蔓延至芯片的表面,然后停止蔓延。图22中的左图所示的、被扩大的堆垛层错覆盖的区域,已经无法再导电,因此芯片的有效有源区域缩小。

图22.SiC器件中的叠层缺陷的俯视图和横截面

结合潜在的物理背景因素,可以得出双极退化是:

一种有可能发生或不发生的机制。当器件不存在BPD时(或者BPD不受复合事件影响时),将不存在双极退化效应。

所有SiC器件都存在的一种效应。由于BPD是SiC衬底(晶圆)中的一种常见缺陷,所以任何拥有PN结的SiC器件都可能发生双极退化,而无论器件类型是什么,生产厂家是谁。

一种饱和效应。一旦堆垛层错蔓延至器件表面,双极退化就会饱和。取决于通过PN结的电流和结温等运行条件,从初始状态到饱和的时间可以是几分钟到几小时的累积双极运行时间。

在应用中的影响

如前所述,内部拥有扩大的叠层缺陷的区域似乎表现出更大的电阻,因而流经它的电流即减小。图23显示了有缺陷和无缺陷的SiC器件的热图像(EMMI)。可以清楚地看到,拥有堆垛层错的区域因为流经的电流很小几乎没有产生热量。

图23. 有少量缺陷(黑色小三角形,见箭头)的和无缺陷的SiC MOSFET在导通模式下的EMMI图。颜色表示电流密度(蓝色代表密度小,红色代表密度大),加粗黑线代表器件的无源区域。

从试验中可以证实,双极退化只会使SiC器件的有源区域减小,进而使得MOSFET的RDS(on)变大,体二极管的VSD变大。器件的其它基本参数(如击穿电压、开关行为和氧化层可靠性)未发生改变。

因此,如果碳化硅器件有少量缺陷,并且饱和后的RDS(on)或VSD增大幅度仍然位于数据表给出的范围以内,则它在运行中不会有长期的负面影响。

CoolSiC MOSFET——消除风险的策略

英飞凌已采取专门的措施来确保其交付给客户的产品拥有稳定的性能。已采取两种措施来确保有可能使用体二极管的所有CoolSiC MOSFET,在发出时不存在任何导致不符合数据表规定的双极退化。

其中包括采取优化的芯片生产工艺以抑制叠层缺陷的形成,并结合有效的验证措施。

责任编辑:xj

原文标题:浅谈SiC MOSFET体二极管双极性退化问题

文章出处:【微信公众号:英飞凌工业半导体】欢迎添加关注!文章转载请注明出处。

-

二极管

+关注

关注

147文章

9627浏览量

166307 -

MOSFET

+关注

关注

147文章

7156浏览量

213145 -

SiC

+关注

关注

29文章

2804浏览量

62607

原文标题:浅谈SiC MOSFET体二极管双极性退化问题

文章出处:【微信号:yflgybdt,微信公众号:英飞凌工业半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

常见二极管故障及维修方法

PiN二极管和SiC二极管的区别

SiC二极管的工作原理和结构

测量二极管的正确方法有哪些

肖特基二极管与其他二极管的区别

SemiQ推出高性能1700V SiC肖特基二极管和双二极管模块

SiC MOSFET体二极管双极性退化问题

SiC MOSFET体二极管双极性退化问题

评论