近日,美光发布了用于DRAM的新型1α制造工艺。并计划首先将其用来制造DDR4和LPDDR4存储器,并在之后将其用于生产他们所有类型的DRAM。如今,扩展DRAM已经变得异常困难。但据介绍,该制造技术有望显着降低DRAM成本。这个神秘的“1α”会有多神奇?我们一起来看看。

芯片制造的目标就是缩小电路以在芯片上容纳更多的晶体管或存储单元。60年前,第一批芯片的元件——晶体管可以用肉眼看到。现在相同的组件只有几纳米宽。那是它的十亿分之一!

更小的晶体管开关速度更快,能耗更少,而且,通过纯粹的规模经济,制造成本也更低。跳到我们最新的技术节点,它是当今世界上最先进的。它在性能、能效和制造成本方面都会有重大改进。

想象一下,如果汽车以同样的速度进步的话。他们可以在一眨眼的功夫从0加速到60英里/小时,只需要几滴燃料就可以环游地球。

现在,制造芯片这个事是复杂的。制造一个现代芯片需要一千多个独立的过程和测量步骤——所有这些步骤都必须近乎完美。这些步骤是在先进的设备上完成,这些机器由数百家专业公司生产,使用超纯材料,在巨大的洁净室中进行,那里的空气中颗粒比月球上的空气还要少。

由于这种复杂性,行业往往遵循类似的节奏从一个节点到另一个节点。并通过芯片上最小的特征来引用它们。例如,在很久之前,我们还处于180纳米节点,大约十年前,我们已在22纳米节点上。

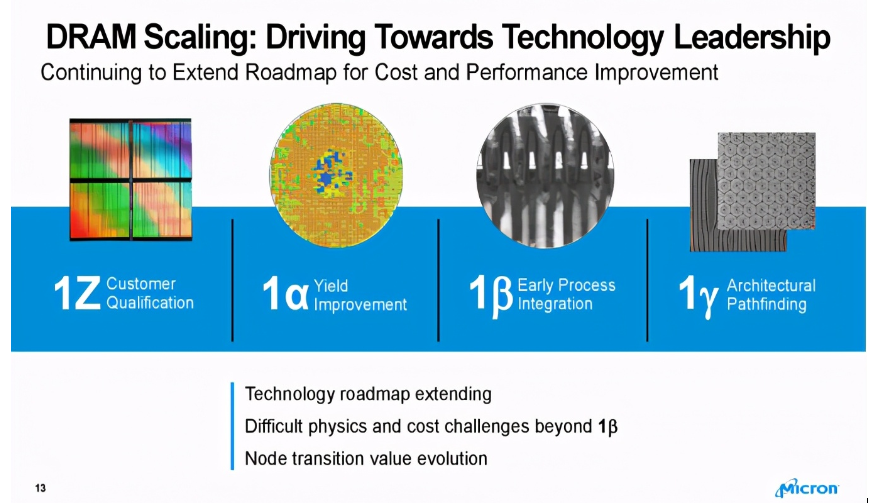

但是几年前,在内存世界里发生了一件有趣的事情。我们不再讨论确切的数字,而是开始使用像1x, 1y和1z这样的术语。特别是DRAM,节点的名称通常对应于存储单元阵列中活动区域的一半间距的大小——“半间距”。至于1α,你可以把它看作是第四代的10nm级别,其半节距从10到19nm。当我们从1x纳米到1y 1z和1α时,这个尺寸会变得越来越小。我们从1x开始,但随着我们继续缩小并命名下一个节点,我们到达了罗马字母表的末尾。这就是为什么我们改用希腊字母α,β的缘故。

从尺寸的角度来看,我们说的小到底有多小?

芯片在直径300mm的硅片上可一次制造数百个。每个芯片都有指甲盖那么大。如今,一个晶体管在一个典型的存储芯片上,能有着80亿比特的存储空间。

限制光刻

半导体行业每年或每隔二十年就会收缩设备。我们知道如何在只有一个原子厚的材料薄膜上进行刻蚀,我们也会有选择地去除材料的能力。那么,现在有什么不同呢?

也许最困难的挑战是定义晶圆片上的电路模式。第一部分叫做光刻(用光在石头上写字!)。它类似于前数码摄影的过程,光线通过一个小的透明版的照片照射到光敏纸上。在我们的案例中,我们使用巴士大小的机器,通过放置在透明方形石英上称为光掩模的模式照射深紫外光。但原理是一样的。

这是一个物理问题。多亏了 “瑞利准则”,或者衍射极限,这让人们认为不可能投射出一个小于所用光波长一半的特征的图像。只是不可能制造出足够锐利的光束来做出精确的图案。在我们的例子中,波长是193nm,所以我们的工作远远低于衍射极限。

现在有一种新的光刻工具,它使用更小的32 nm波长的极紫外线(EUV),但由于一些复杂的原因,我们认为它还没有准备好。其中一个原因是波长太短,光线不能穿过玻璃,所以传统的光学透镜不起作用。15年前,人们认为EUV光刻技术可以用于32纳米节点。EUV的时代将会到来,但它不是1α在微米级别的正确解决方案。

“愚弄”光线,违背瑞利准则

我们使用许多技术来绕过衍射极限。第一种方法是修改光掩模上的图案,使其形成尖锐的特征。目前最先进的技术被称为计算光刻技术,它使用大量的处理能力从晶圆上所需的图案有效地进行反向工程掩模。

第二是利用水对光的衍射比空气小这一事实,使晶圆在水下暴露。实际上,我们用一滴水来取代最终镜头和晶圆片表面之间的气隙。这种方法可以使我们达到40nm以下,这是一个很大的改进,但并不是一直都能成功。

多重图案

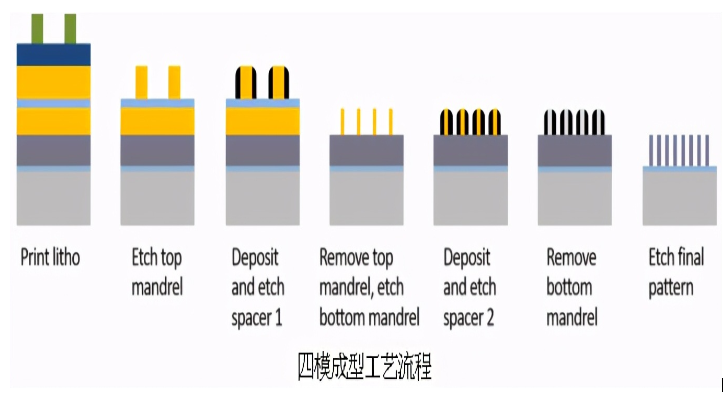

解决分辨率的方法是添加一系列非光刻步骤,神奇地将一个“大”特征变成两个,成为四个特征,每个特征的大小都是原来的四分之一。有很多不同的方法可以同时实现这一点,但我必须指出,早在2007年,美光是第一个使用双模式开发闪存的公司。

这样简化了很多工作,基本的想法是用步进器创造特征,在这些特征的侧面涂上不同的材料,然后去掉原来的特征(sacrificial features)。得到Voilà -两个半尺寸的功能!重复这个过程,我们有了所需的 1α的四个特征大小。

清洗和重复

现在我们知道我们可以精确地绘制出我们需要的微小特征,但我们离一个完整的模具还有很长的路要走,更不用说大批量生产了。我们只是为一层的功能做了轮廓,要知道每个芯片中有几十层。自豪的是,我们可以精确地将层层对齐,这称之为叠加。准确无误地做到这一点是让整个过程顺利进行的关键。

然后,我们必须把图案转换成有功能的电路设备,比如控制读写数据的晶体管,以及能够存储代表“1”和“0”的电荷的又高又瘦的电容器。这一过程意味着要精确控制材料的组成以及这些材料的机械和电学特性,而且每次都要做完全相同的事情。

我们不仅整合了我们自己的创新,而且与供应商合作伙伴紧密合作。我们正在将最新和最先进的技术应用于各个领域:新材料(如更好的导体和更好的绝缘体),以及用于沉积、修改或选择性去除或蚀刻这些材料的新机械。

我们已经将晶圆厂发展成一个以AI驱动、高度自动化的智能工厂。正如我前面提到的,要在晶圆厂内制造一个现代化的芯片,需要一千多步骤,每一步都必须完美。

半导体制造不像制造汽车。你不能返回并修复流程中早期引入的缺陷。任何缺陷都被埋在后面的层下面。成功的关键是数据,以及从数据中获得的洞察力。来自几十万个传感器的数据涌入我们10千万亿字节的制造执行系统。我们每天通过检查系统输入100多万张图像,并使用深度学习在问题发生之前发现问题。芯片制造可能是地球上最复杂的工程了。

我们是怎么做到的?

美光的工程团队是如何能够在短时间内将1α节点拉下来,并将我们置于行业前沿的。答案就在美光数万名工程师和科学家身上。

从我们的技术开发、设计、产品和测试工程人员到制造和质量,这是所有相关学科之间协作精神的证明。这也证明了我们的团队成员的热情和坚韧,以永久的“全员待命”模式运作,这使美光走在DRAM技术的前沿。

责任编辑人:CC

-

制造工艺

+关注

关注

2文章

179浏览量

19760 -

工艺技术

+关注

关注

0文章

18浏览量

9526

发布评论请先 登录

相关推荐

详解电容的测试条件

安森美推出基于BCD工艺技术的Treo平台

一文详解OSP工艺PCB板的优缺点

概伦电子NanoSpice通过三星代工厂3/4nm工艺技术认证

CMOS工艺技术的概念、发展历程、优点以及应用场景介绍

一文解析Molex端子压接工艺技术标准

MEMS封装中的封帽工艺技术

三星与Arm携手,运用GAA工艺技术提升下一代Cortex-X CPU性能

一文弄懂半导体掩膜版制造工艺及流程

一文详解1α工艺技术

一文详解1α工艺技术

评论