19世纪,物理学家阿米西曾在义大利佛罗伦斯的实验室里,把一滴液体加在标本上方,藉此改善显微镜的成像品质。100多年后,现在全球的半导体产业采纳阿米西的创新技术,把晶片浸在浅薄的液体层中,制造出的电路线宽,可望媲美病毒大小。

20世纪40年代,约翰·巴丁和沃尔特·布拉顿在贝尔实验室进行研发,研发晶体管的过程中将钨丝电极移到金粒的旁边,加上负电压,而在金粒上加了正电压,突然间,在输出端出现了和输入端变化相反的信号,他们将此器件命名为Transistor—晶体管,从此人类步入了飞速发展的电子时代。

半导体行业发展至今,离不开很多优秀的领路人,他们靠自己的智慧生产了一个个里程碑事件,他们依靠自己的力量在所热爱的行业中发光发热,用100%热情与投入吸引着一代又一代的热血青年加入半导体这个有意思的行业,今天我们一起盘点下集成电路发展史上的十大里程碑事件!

闪光时刻:1947年,美国贝尔实验室的巴丁(J.Bardeen)、布拉顿(W. Brattain)、肖克莱(W.Shockley)三人发明了晶体管,获得了1956年诺贝尔物理学奖。

发生背景: 1947年,约翰·巴丁和沃尔特·布拉顿在贝尔实验室进行研发,研发晶体管的过程中将钨丝电极移到金粒的旁边,加上负电压,而在金粒上加了正电压,突然间,在输出端出现了和输入端变化相反的信号。初步测试的结果显示:电压放大倍数为2,上限频率可达1万Hz。此后的几天,他们把试验装置进行了改进,测得的功率增益为大于18。他们将此器件命名为Transistor—晶体管。从此人类步入了飞速发展的电子时代。这是微电子技术发展历程中第一个里程碑。

世界上第一颗锗点接触式晶体管诞生两年之后,肖克利首次提出了晶体管理论。1953年,出现了锗合金晶体管。1954年1月,贝尔实验室的化学家MorrisTanenbaum利用摩根·斯巴克斯和戈登·蒂尔的生长界面成分变化技术,成功制造了第一个硅晶体管。

诞生意义: 晶体管彻底改变了电子领域,为更小,更便宜的收音机,计算器和计算机等铺平了道路,第一个晶体管和MOSFET被列在电子领域的IEEE里程碑列表中,MOSFET是现代电子设备的基本组成部分,在现代电子系统中无处不在。在1960年至2018年期间,估计总共制造了13亿个MOSFET(至少占所有晶体管的99.9%),使MOSFET成为历史上制造最广泛的器件。 大多数晶体管是由非常纯的硅制成的,有些是由锗制成的,但有时会使用某些其他半导体材料。在场效应晶体管中,晶体管可以仅具有一种电荷载流子,或者在双极结型晶体管器件中可以具有两种电荷载流子。与真空管相比,晶体管通常更小并且需要更少的功率来工作。某些真空管在非常高的工作频率或高工作电压下比晶体管具有优势。多家制造商已将许多类型的晶体管制成标准化规格。

闪光时刻:

1958年,德州仪器的杰克·基尔比(Jack Kilby,被誉为“集成电路之父”)展示了第一款集成电路。他于2000年获诺贝尔物理学奖。

诞生背景:

20世纪50年代,晶体管已得到了一定的发展。人们已经可以用硅做出分立的电阻、电容、二极管和三极管。彼时,在德州仪器的工程师Jack Kilby认为,既然能用单一材料硅制作这些分立器件,就能把这些器件做在一起。所以,1958年9月12日,JackKilby借助已有的几种锗器件,把金属蒸镀在锗管的“发射极”和“基极”上,再用蚀刻技术做成接触点,然后连接起来,制成了世界上第一块集成电路。

尽管该装置相当粗略,但是当Jack Kilby按下开关,示波器显示屏上却赫然出现了不间断的正弦波形。试验证明他的发明成功了,他彻底解决了此前一直悬而未决的问题。Jack Kilby在1976年发表的文章《集成电路的诞生》中写道:“细想之后,我发现我们真正需要的其实就是半导体,具体来说,就是电阻器和电容器(无源元件)可以采用与有源元件(晶体管)相同的材料制造。我还意识到,既然所有元件都可以用同一块材料制造,那么这些元件也可以先在同一块材料上就地制造,再相互连接,最终形成完整的电路。

但是,Jack Kilby的发明是混合集成电路(Hybrid IC),而不是单片集成电路(monolithic IC)芯片,Kilby的IC具有外部电线连接,这使其难以批量生产。

在Jack Kilby的发明半年后,罗伯特·诺伊斯(Noyce)在仙童半导体公司发明了第一个真正的单片式IC芯片,是一种新的集成电路,比Kilby的实现更实用。诺伊斯的设计是由硅制成的,而Kilby的芯片是由锗制成的。Noyce的单片IC将所有组件放在硅芯片上,并用铜线连接它们,Noyce的单片IC是使用平面工艺制造的,该工艺由他的同事Jean Hoerni在1959年初开发。现代IC芯片基于Noyce的单片IC,而不是Kilby的混合IC。

诞生意义:

集成电路的发明是应用需求和技术发展及创新思想共同作用的结果,开启了以微电子技术为基础的计算机和信息技术迅猛发展的新篇章。

闪光时刻:

平面加工工艺(光刻)的发明(1957年)和摩尔定律的提出(1965年)诞生背景:1957年,美国DOF实验室首先将光刻技术引入到半导体技术中,为集成电路技术和产业按照摩尔定律发展奠定了基础。仙童公司的Noyce 将光刻技术,巧妙利用起来,实现了精细晶体管和集成电路图形结构,由此导致了平面工艺的诞生。 光刻技术是集成电路制造中利用光学-化学反应原理和化学、物理刻蚀方法,将电路图形传递到单晶表面或介质层上,形成有效图形窗口或功能图形的工艺技术。从1960年开始,光刻法被用于在Si上制作大量的微小晶体管,当时分辨力为5μm,如今除可见光光刻之外,更出现了X射线和荷电粒子刻画等更高分辨率方法,光刻是集成电路制造过程中的关键环节。目前国内自主研发芯片的困境便主要来源于高质量光刻设备的缺乏。

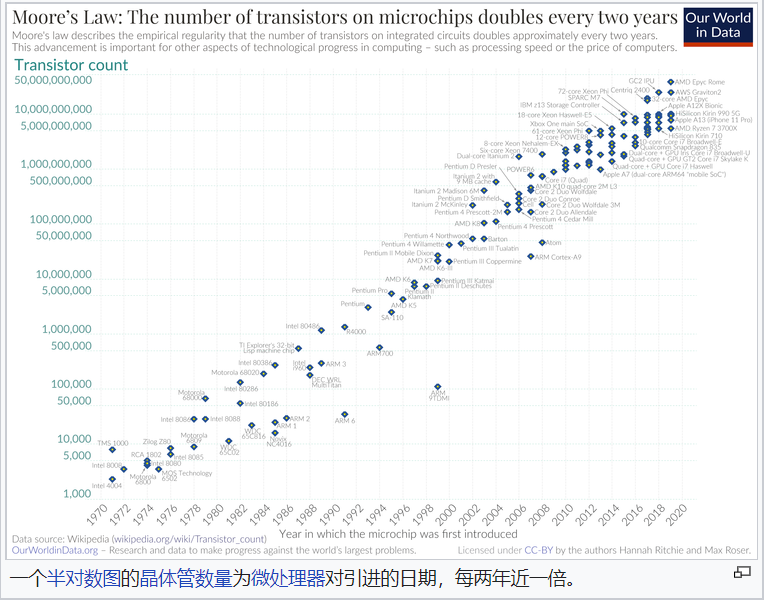

1959年7月,Noyce研究出一种二氧化硅的扩散技术和pn结的隔离技术,并创造性地在氧化膜上制作出精细的铝膜连线,使元件和导线合成一体,从而为半导体集成电路的平面制作工艺、为工业大批量生产奠定了坚实的基础。与Kilby在锗晶片上研制集成电路不同,Noyce 直接盯住硅-地球上含量最丰富的元素之一,商业化价值更大,成本更低。自此大量的半导件被制造并商用,风险投资开始出现,半导体初创公司涌现,数量更多、功能更强、结构更复杂的集成电路被发明。 1965年4月19日,《电子学》杂志(Electronics Magazine)第114页发表了摩尔(时任仙童半导体公司工程师)撰写的文章〈让集成电路填满更多的组件〉,文中预言半导体芯片上集成的晶体管和电阻数量将每年增加一倍。 1975年,摩尔在IEEE国际电子组件大会上提交了一篇论文,根据当时的实际情况对摩尔定律进行了修正,把"每年增加一倍"改为"每两年增加一倍",而普遍流行的说法是"每18个月增加一倍"。但1997年9月,摩尔在接受一次采访时声明,他从来没有说过"每18个月增加一倍",而且SEMATECH路线图跟随24个月的周期。 大抵而言,若在相同面积的晶圆下生产同样规格的IC,随着制程技术的进步,每隔一年半,IC产出量就可增加一倍,换算为成本,即每隔一年半成本可降低五成,平均每年成本可降低三成多。就摩尔定律延伸,IC技术每隔一年半推进一个世代。

诞生意义:

光刻技术的发明,为集成电路技术和产业按照摩尔定律发展奠定了基础,实现了精细晶体管和集成电路图形结构,由此导致了平面工艺的诞生。

摩尔定律是简单评估半导体技术进展的经验法则,其重要的意义在于长期而言,IC制程技术是以一直线的方式向前推展,使得IC产品能持续降低成本,提升性能,增加功能。

闪光时刻:

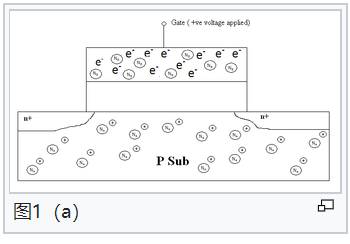

1960年,MOSFET器件发明;1963年,COMS(互补金属氧化物半导体)技术被提出;1966年,美国RCA公司研制出CMOS集成电路。诞生背景: 1955年,Carl Froschand Lincoln Derrick偶然覆盖的硅的表面的晶片有一层二氧化硅,氧化层阻止了某些掺杂剂进入硅晶片,同时允许其他掺杂剂,从而发现了半导体表面氧化的钝化作用。他们的进一步工作证明了如何在氧化物层中蚀刻小开口以将掺杂剂扩散到硅晶片的选定区域中。1957年,他们发表了一篇研究论文,他们开发的技术被称为氧化物扩散掩膜,稍后将在制造中使用MOSFET器件。

贝尔实验室的Mohamed M. Atalla于1950年代后期处理表面状态问题。他认为,在干净的硅晶片上生长非常薄的高质量热生长的SiO2,将中和表面状态,足以制成实用的场效应晶体管。 1960年,贝尔实验室的Kahng和Atalla制备出了第一支MOS场效应晶体管(MOSFET);1963年,任职于仙童公司白程师F.M.Wanlass和C.T.Sah首次提出CMOS技术,由低功来高效率的CMOS替代了传统的TTL(Transistor-to-Transi Logic,晶体管-晶体管逻辑)电路。如今,95%以上的集成电芯片都是基于CMOS工艺,可以说没有CMOS,就没有之后整集成电路的发展。 早期的CMOS元件虽然功耗比常见的TTL电路要低,但为工作速度较慢,所以大多数应用CMOS的场合都和降低功耗、延长电池使用时间有关,例如电子表。不过经过长期的研究与良,如今的CMOS元件无论在可集成的面积、工作速度、功耗,还是在制造的成本上看,都比当时另外一种主流的半导体制程BJT (Bipolar Junction Transistor,双极结型晶体管)有优势,很多在BJT无法实现或是成本太高的设计,利用CMOS皆可迎刃而解。诞生意义:

MOSFET的发展引发了电子技术领域的一场革命,称为MOS革命或MOSFET革命,为早期半导体行业的技术和经济增长提供了动力。 从1960年代后期开始,MOSFET的影响在商业上变得很重要。这导致了电子行业的一场革命,此后几乎以各种方式影响了日常生活。MOSFET的发明被认为是现代电子技术的诞生,并且是微型计算机革命的核心。 CMOS集成电路因为具有功耗低源电人阻抗高、噪声容限高、电源电压范围宽、输出电压幅度与电源电压接近、对容限迟和跃迁时间等优点所以发展极为迅速 CMOS集成电路的问世开创了微功耗电子学的先河,为如今的大规模集成电路发展奠定了坚实基础,具有里程碑意义。

闪光时刻:

1967年,DRAM(动态随机存取存储器)发明;1971年,全球第一款微处理器4004由Intel公司推出。诞生背景:1966年,Dennard提除了DRAM的想法,当时他的MOS项目非常有希望,但相当复杂,因为每一比特的信息需要使用六个晶体。于是,他利用业余时间研究自己的新想法,并且最终找到了通过存取晶体管将电荷写入电容,然后通过同一个晶体管读出的替代方法。1967年,Dennard 和IBM公司针对他的“单晶体管动态随机存取存储器”(DRAM)申请了专利。在一块芯片上集成的元件数超过10万个,或门电路数超过万门的集成电路,称为超大规模集成电路。1988年,16M DRAM问世,在1c㎡大小的硅片上集成有3500万个晶体管,标志着进入超大规模集成电路(VLSI)阶段。超大规模集成电路研制成功,是微电子技术的一次飞跃,大大推动了电子技术的进步从而带动了军事技术和民用技术的发展。

20世纪60年代随着集成电路的发明和应用,一场制造轻便桌面计算器的竞赛揭开了帷幕。那时,半导体产业的研究者已普遍意识到,用新的MOS技术来创建一个包含多种功能的芯片在理论上是可行的。短短几年后,Intel公司便于1971年成功地研制出实际上第一款微处理器4004,由2300个晶体管构成了一款包括运算器、控制器在内的可编程序运算芯片。使得微处理器成为继晶体管、集成电路后的又一重大发明。可以说,中央处理单元的发明与应用改变了整个世界的科技发展,掀起了一场新的技术革命。

诞生意义:DRAM的简单性、低成本和低功耗与第一款低成本微处理器相结合开启了小型个人电脑的时代。Intel 4004微处理器是世界上第一款商用计算机微处理器,它是“一件划时代的作品”。它在单片内集成了2250个晶体管,晶体管之间的距离是10μm,能够处理4bit的数据,每秒运算6万次,运行的频率为108kHz,成本不到100美元。Intel公司的首席执行官戈登·摩尔将4004称为“人类历史上最具革新性的产品之一”。

闪光时刻:

铜互连技术的发明

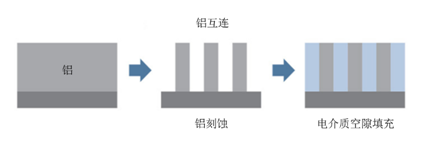

诞生背景: 集成电路最初用铝作为导体,二氧化硅作为绝缘体(电介质),构建一个互连层,来将多个器件连接在一起。整个互连的过程由铝沉积在晶圆表面开始,随后通过选择性刻蚀形成布线图案,沉积氧化物绝缘体,并利用化学机械平坦化(CMP)工艺将粗糙的表面变得平坦。

20世纪 80 年代后期,随着器件特征尺寸继续缩小,越来越薄的铝线无法实现所需的速度和电性能,因此需要一种性能更优的导电材料,以适应继续缩小的器件尺寸,同时保持芯片制造商预期的成本效益。多年来,该行业的发展大致遵循摩尔定律,即晶体管密度每 18 个月翻一倍。然而,由于铝互连的电性能局限性,芯片的微缩将无法继续进行,业内人士便开始寻找可替代材料。 人们首先想到的是铜,它具有更低的电阻率,且可实现更快的器件速度。此外,铜并不像铝那样容易发生电迁移,所以具有更高的可靠性。电迁移中,电流推动导线中的金属原子,会导致电阻增加,最终造成电路故障。然而,使用等离子(带电气体)工艺刻蚀铜的方法并不可行。由于铜不容易形成挥发性化合物,因此,通过干法刻蚀并不能轻松地将其从晶片表面除去。芯片若要实现进一步微缩,亟需一种合适的新导体,或截然不同的图形化工艺,或两者的组合。 业内一直在研究其它导体材料,相较之下,铜的电气特性使其成为最佳选择。工程师开始考虑使用镶嵌工艺,即借鉴大马士革的珠宝行业,先在基底金属上刻蚀图案,再将贵金属嵌入图案之中。该工艺绕过刻蚀铜的难题,先沉积和刻蚀电介质材料,形成由沟槽和孔洞组成的图案(即镶嵌金属的模具)。然后,仅将金属填充到图案中,而不是在整个晶圆表面沉积金属膜。

闪光时刻:

浸入式光刻技术的发明

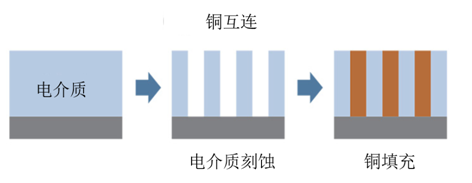

诞生背景: 在浸入式光刻技术之前,继436nm、365nm、248nm之后,采用的是193nm干式光刻技术,但在65 纳米技术节点上遇到了困难,试验了很多技术(如157nm干式光刻技术等)但都无法很好的突破这一难题。等到2002年底浸入式技术迅速成为光刻技术中的新宠,而此前业界并没有认为浸入式技术有如此大的功效。此技术在原来的193nm干式光刻技术平台之上,因为此种技术的原理清晰及配合现有的光刻技术变动不大,获得了人们的极大赞赏。 浸没式光刻技术需要在光刻机投影物镜最后一个透镜的下表面与硅片上的光刻胶之间充满高折射率的液体。图 l 为传统光刻和浸没式光刻的对比示意图。投影物镜的数值孔径:NA=nsinθ

图1 传统光刻和浸没式光刻示意图 其中,n为投影物镜与硅片之间介质的折射率,θ为光线最大入射角。在最大入射角相同的情况下,浸没式光刻系统的数值孔径比传统光刻系统增大了n倍。而从傅里叶光学的角度, 数值孔径扮演着空间频率低通滤波器阈值的角色。注人高折射率的浸没液体可以使更高空间频率的光波人射到光刻胶上, 因此成像分辨率得以提高。 如今,EUV技术慢慢开始替代了一部分的浸没式光刻,EUV技术以波长为10-14纳米的极紫外光作为光源的光刻技术。具体为采用波长为13.4nm 的紫外线。极紫外线就是指需要通过通电激发紫外线管的K极然后放射出紫外线。EUV光刻采用波长为10-14纳米的极紫外光作为光源,可使曝光波长一下子降到13.5nm,它能够把光刻技术扩展到32nm以下的特征尺寸。 EUV光刻所能提供的高分辨率已经被实验所证实。光刻机供应商已经分别实现了20nm和14nm节点的SRAM的曝光,并与193i曝光的结果做了对比。显然,即使是使用研发机台,EUV曝光的分辨率也远好于193i。14nm节点图形的曝光聚焦深度能到达250nm以上。

闪光时刻:多晶硅栅/high-k基MOS管和金属栅/high-k基MOS管发明诞生背景: 由于Si-SiO2良好的界面特性以及SiO2薄膜的优异性能,纯硅基MOS器件具有优异的界面性能和热稳定性,并且致密的SiO2薄膜能够阻止更多的氧气和水分子进入栅介质层。此外,多晶硅与衬底硅的功函数差值较小,有利于降低器件的阈值电压,从而提高器件开关速度。 然而,当特征长度降至65nm节点时,就会出现短沟道效应,显著增大器件的功耗。为了控制短沟道效应,更小尺寸器件要求进一步提高栅电极电容。这能够通过不断减小栅氧厚度而实现,但随之而来的是栅电极漏电流的提升。当二氧化硅作为栅电极绝缘层且氧化层厚度低于5.0nm时,漏电流就变得无法忍受了。

解决上述问题的方法就是使用高介电常数绝缘材料取代二氧化硅,采用这种材料可以在不增加电学厚度的前提下允许增加绝缘层厚度,进而能够降低漏电流。经过反复试验,基于铪(Hf)的high-k绝缘材料取代二氧化硅作为栅电极的绝缘层。high-k介质的引入能在一定程度上缓解SiO2厚度减小引起的隧穿效应,进而减小泄漏电流,降低器件功耗。然而,当特征长度降至45nm节点时,多晶硅/high-k基MOS器件出现严重的多晶硅耗尽效应。多晶硅的高电阻率也严重影响了MOS器件的高频特性。 此外,在早期的高介电常数材料的研发中就已经发现了high-k介质与多晶硅栅电极不匹配的问题。这一问题不仅会导致在高介电材料与多晶硅材料的界面上产生大量的缺陷,还会降低器件的电子迁移率。后一问题是由于电荷散射而引起的,这也是将这两种材料结合在一起的固有表现。因此,金属栅替代了多晶硅栅,被用于纳米晶体管和先进晶体管结构。 金属栅极是为了和high-k栅介质材料兼容而提出的。一方面,金属作为良导体,不会产生耗尽层,有效地消除了多晶硅耗尽效应,同时也使金属栅极无需通过掺杂提高导电性:另一方面,与多晶硅栅极相比,金属栅极材料自由电子浓度远大于反型层载流子浓度,使得金属栅极能够有效抑制high-k介质低能光学声子与沟道载流子耦合,从而降低声子散射,提高载流子迁移率。

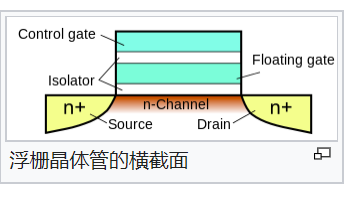

闪光时刻:浮栅(Floating Gate)存储器件发明诞生背景: 伴随着整个半导体微电子产业的发展,存储器也在以惊人的速度发展。以动态存储器(DRAM)为例,每个功能元件的尺寸不断减小,价格不断下降,每个存储单元工作所需的电子数目也越来越少。DRAM中的电容如果不能提供足够多的电子给放大器,整个存储器将被噪声所淹没,将不能保证信息存储的可靠性。 当每个存储单元的电子数目因集成度的提高变得越来越小时,存储器中的MOS场效应晶体管将逐渐变得不定,而使整个存储器的可靠性难以得到保证。 单电子存储器的出现使存储器继续维持高速发展成为可能,目前已经实现室温下的对背景电荷不敏感的单电子存储器,因此实际应用的前景非常光明。从目前设计制备出来的单电子存储器来看,它们的工作通常只需控制几百个、几十个甚至几个电子就可以实现数据的存储,因此它们的功耗非常低。

单电子晶体管是单电子存储器的最主要的组成部分,单电子晶体管的特性在一定程度上决定了基于它制备的存储器的性能,所以它的发展在很大程度上制约单电子存储器的发展。在单电子存储器中,使用对电荷超敏感的库仑计对存储单元中的电荷进行探测,来确定存储单元的状态。这些超敏感的库仑计是将单电子晶体管和浮栅与被测的对象集成在一起,利用单电子晶体管对栅极电荷的敏感性来实现电荷的探测。而在另一些单电子存储器中则是利用单电子晶体管中的库仑阻塞现象,通过控制源、漏和栅极电压来实现对源(或漏)上电子数目的精确控制,然后利用其他的放大部分(如MOSFET等)来实现数据的存储。其中的单电子晶体管有些具有单个量子点结构,而有些则具有纳米线结构。 浮栅量子点的存储器是依据量子点的库仑阻塞原理设计和制备的。依据Fowler—Nordheim隧穿原理,利用栅极来控制电子进出量子点,使量子点在库仑阻塞区域的边界达到两个稳定的电压值,此时系统的两个稳定态对应着量子点两个不同的势能。通过电容耦合一个单电子晶体管(库仑计)或者利用MOS场效应管来对量子点的状态进行探测,便可以确定出系统的状态。为了实现单电子器件的高密度存储,就必须精确控制量子点的形状和位置,因此这些器件的制备通常具有一定的难度,但是利用扫描探针技术可以制备出常温下就可以正常工作的单电子存储器;如果使用纳米硅颗粒来制备器件,它们也可以在室温下工作,并且不受背景电荷涨落的影响。

FGMOS可以通过将标准MOSFET栅极绝缘来制造。通过绝缘使得其栅极与外界没有电阻连接;然后在浮栅上方沉积多个次级栅极或输入电极,并与其电隔离。由于浮栅完全被高电阻材料包围,输入电极和浮栅之间仅有电容耦合,因此,就其直流工作点而言,浮栅是浮动节点。 在需要修改浮栅电荷量的应用,每个FGMOS会添加一对额外的小晶体管,以实现注入和隧穿操作。每个晶体管的栅极连接在一起;隧穿晶体管的源极、漏极和体端子相互连接,形成电容隧穿结构。注入晶体管以正常方式连接,并施加特定电压以产生热载流子,然后通过电场将热载流子注入浮栅。 在纯电容应用中,FGMOS晶体管既可以制造成N型,也可以做成P型。对于电荷改变的应用,隧穿晶体管(以及FGMOS)需要嵌入到阱中,因此该技术决定了可以使用的FGMOS的类型。

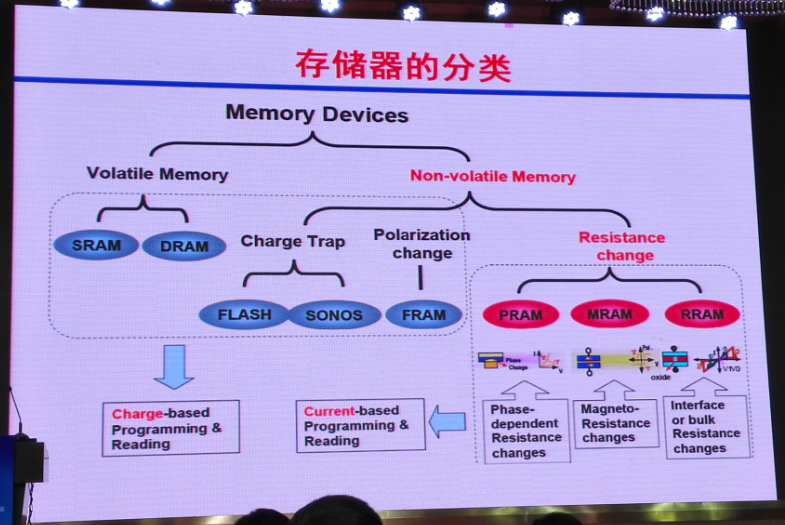

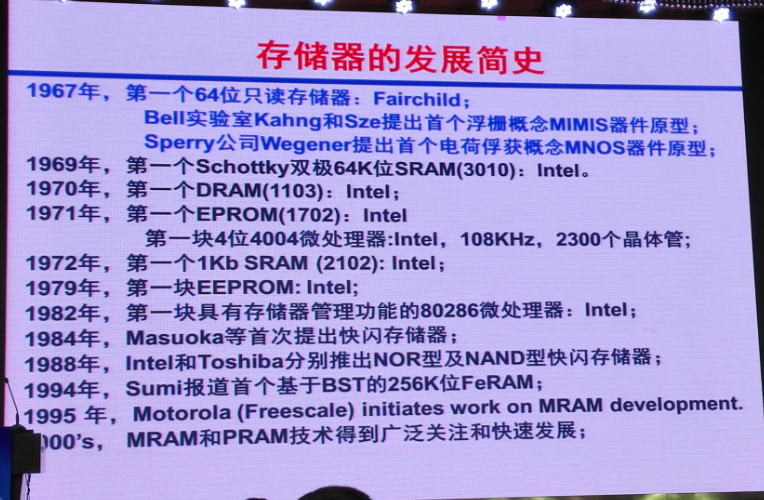

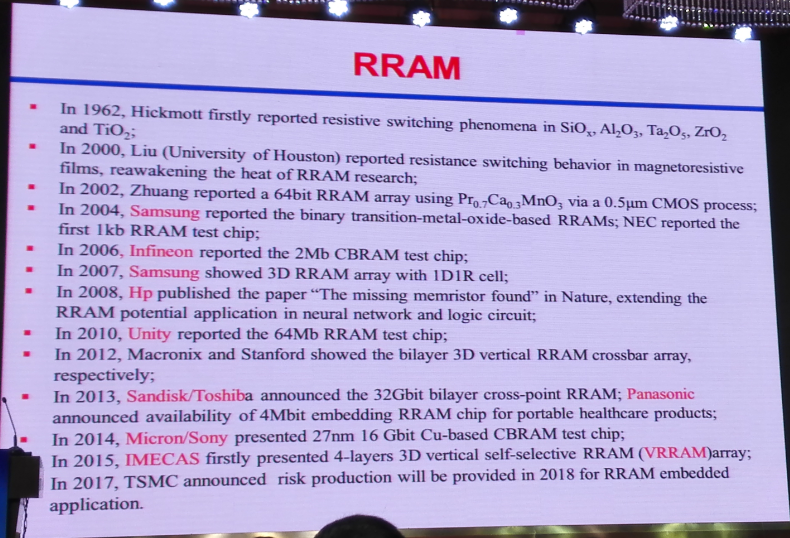

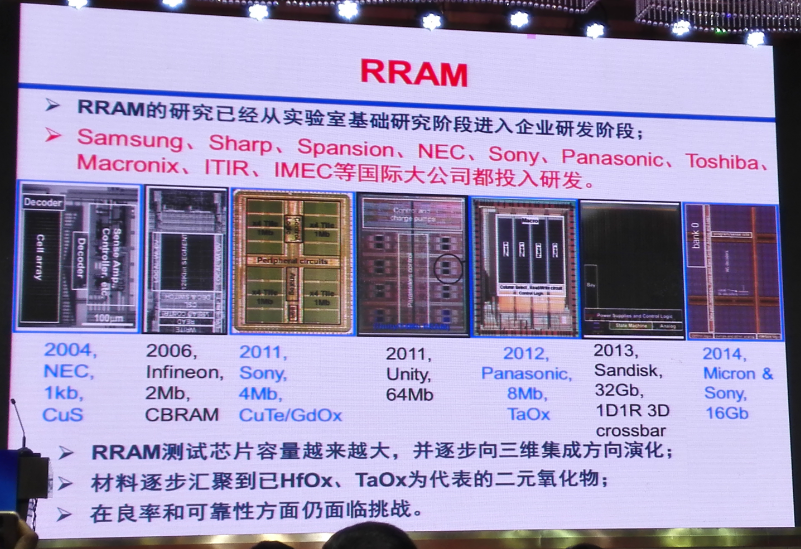

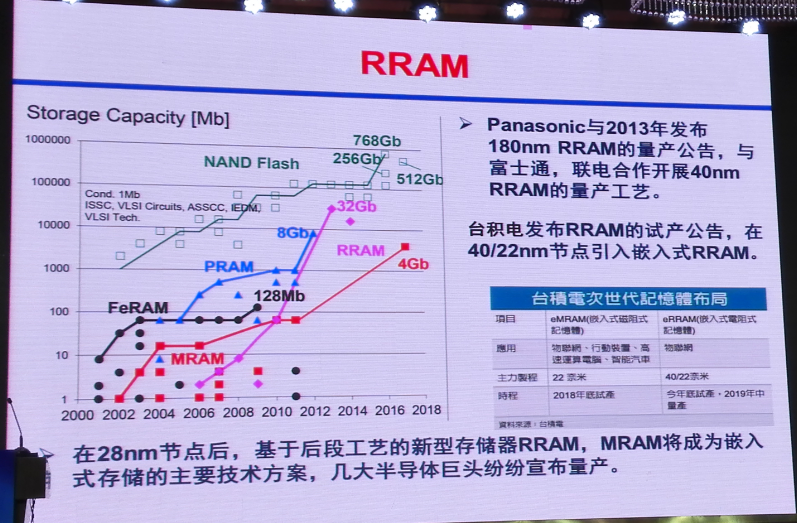

闪光时刻:新型RRAM存储器件发明诞生背景: 存储器分为易失性和非易失性两大类。当今,易失性存储器最重要的两类是SRAM和DRAM。非易失性存储器的种类很多,市场份额最大的是闪存(FLASH),其他的还有SONOS、铁电存储器(FRAM)、相变存储器(PRAM)、磁存储器(MRAM)和阻变存储器(RRAM)等。此外,SRAM、DRAM、FLASH、SONOS和FRAM这五种是基于电荷的存储器,这类存储器本质上是通过电容的充放电来实现的。而PRAM、MRAM和RRAM则是基于电阻的转变来实现的。

存储器距今已发明了50周年。1967年,第一个64位只读存储器由仙童公司发明。闪存也是在这一年由Bell实验室所提出。Intel在存储器发展的早期做出了很多贡献,比如第一个SRAM和第一个EEPROM都由该公司推出。闪存之所以是在90年代才大规模应用,是因为直到1988年,Intel和东芝才分别提出了NOR和NAND两种类型的闪存集成架构。

RRAM相比MRAM和PRAM,研究要稍晚。虽然这个现象早在1962年就被报道了,但没有引起学术界和工业界的关注。直到2000年,美国休斯敦大学在APL上发表了一篇关于“在庞磁阻氧化物薄膜器件中发现电脉冲触发可逆电阻转变效应”的文章后,夏普公司买了该专利,才对RRAM开始了业界的开发,自此以后才引起学术界和业界的研究。主流存储器厂商也纷纷投入力量,开始对RRAM的研究。RRAM也已经由实验室阶段进入到企业的研发阶段。

从容量上看,这三类新型存储器,MRAM最高达4Gb,PRAM最高达8Gb,RRAM最高达32Gb。它们和闪存相比,容量差别还很大,但是不要忘记,这三者的读写速度都比闪存要快1000倍以上。

以上就是我们想要分享给大家的集成电路发展史上的十大里程碑事件,目前半导体行业圈内优秀的研发人员还有很多,他们分布在产业链的上中下游,分布在全世界各地,正为自己热爱的这份事业披荆斩棘,希望在前方道路努力奔跑的大家,能够熠熠闪光!

责任编辑:lq

-

集成电路

+关注

关注

5463文章

12669浏览量

375607 -

晶体管

+关注

关注

78文章

10434浏览量

148543 -

光刻技术

+关注

关注

1文章

151浏览量

16569

原文标题:集成电路发展史上的十大里程碑事件

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

雷曼光电入选ICDT 2026显示行业十大突破性进展榜单

中软国际在金融科技出海征程再添关键里程碑

亿纬锂能绿色制造体系建设取得里程碑式突破

立讯精密在高速互连领域取得里程碑式突破

回顾那些具有里程碑意义的Arm架构产品(1)

奥托立夫祝贺一汽大众达成3000万辆里程碑

华为兆瓦超充入选2026年度中国汽车十大技术趋势

意法半导体卫星数字广播芯片组荣获IEEE里程碑奖

北京奔驰迎来成立20周年的重要里程碑

爱立信携手Telstra创下全新行业里程碑

国内首条碳基集成电路生产线正式投产运营

集成电路发展史上的十大里程碑事件!

集成电路发展史上的十大里程碑事件!

评论