对于逻辑级数较高的路径,常用的方法之一是在其中插入流水寄存器,将路径打断,从而降低逻辑延迟,这在HDL代码中实现起来比较容易。此外,从RTL代码风格角度讲,对于关键模块,设计时常将其输入/输出端口寄存。这起到了隔离关键路径的作用。

但是,如果使用的RTL代码是HLS转换生成的,例如使用Vitis HLS综合的,其可读性较差,想要在其生成的HDL代码中插入寄存器就变得比较困难。为此,我们想到了能否在C代码中插入寄存器,并保证Vitis HLS综合后的结果是寄存器。

这要解决四个问题:一是这样的C代码要具备一定的可复用性,比如,以模板函数的形式呈现。二是这样的C代码是参数化的,尤其是数据类型,因为需要寄存的数据其数据类型不尽相同。这仍然可以借助模板函数实现。三是保证这个函数不被优化合并掉。因为这个函数功能比较单一,输出等于输入,这就要用到INLINE的功能。四是C语言是不具备时序特征的,要实现输出与输入的延迟,就要借助相应的pragma,我们想到了Latency。

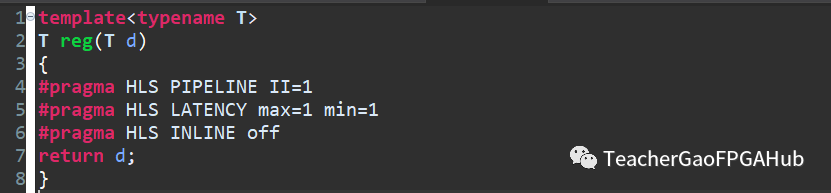

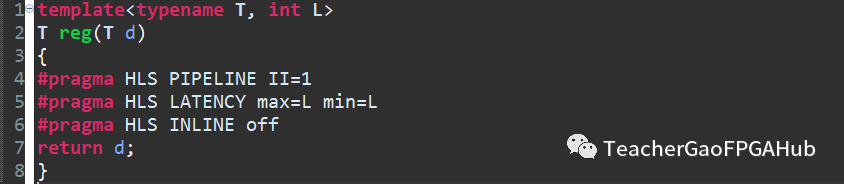

在此基础上,我们构造了下面的C++代码。不难看出,这是一个模板函数,数据类型是参数化的,使用了三个pragma。其中PIPELINE用于限定II为1,LATENCY用于限定延迟为1,INLINE用于防止该函数被合并。

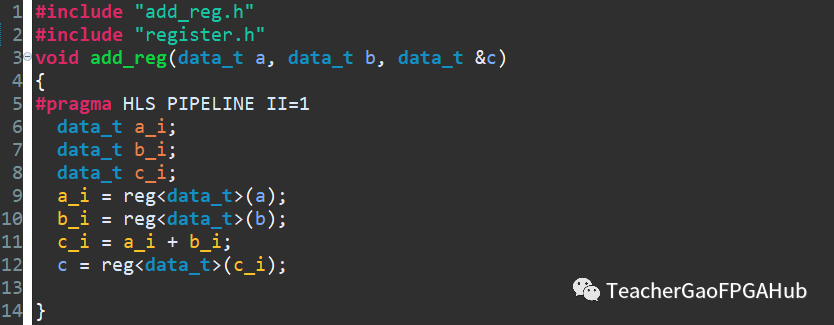

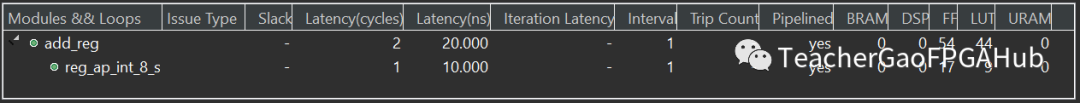

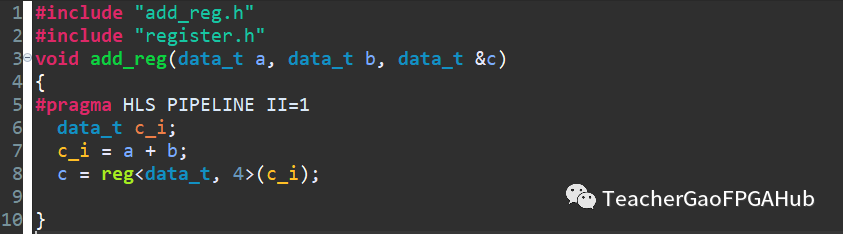

看一个具体的使用案例,如下图所示代码。功能很简单,就是实现两个数的相加。这里对两个输入数据a和b分别做了寄存,同时对结果c也做了寄存。最终的综合报告显示Latency为2,和我们预期的一致。对于生成的HDL代码,将其添加到Vivado中进行综合,综合后的结果也是符合预期的。

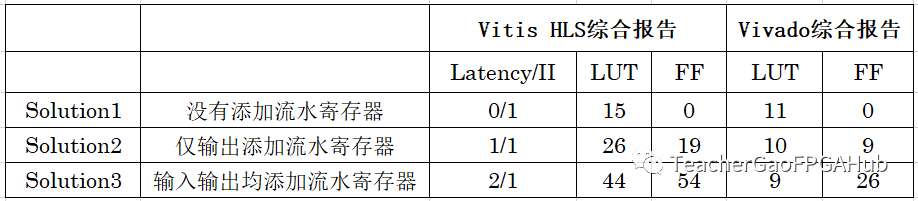

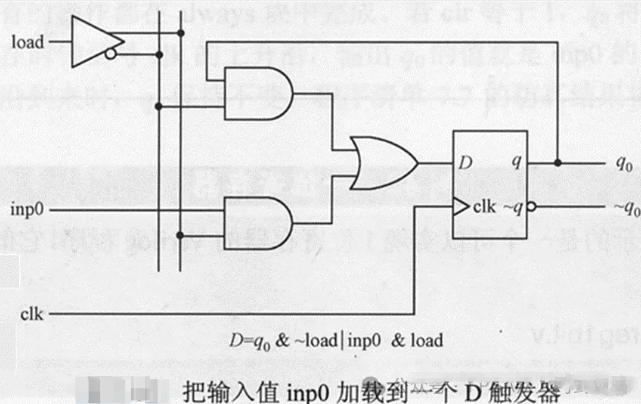

这里,我们对比一下三种情形。情形1:不添加流水寄存器;情形2:仅对输出添加流水寄存器;情形3:输入输出均添加流水寄存器。Vitis HLS综合结果以及其生成的HDL代码在Vivado下的综合结果对比如下图所示。首先,可以看到Latency符合预期,同时II始终为1;其次,Vivado下综合后的资源利用率与Vitis HLS的结果是不一致的。这一点也很容易理解,因为Vivado综合时会有很多优化。

进一步,我们看到这里的延迟为1,如果需要两级延迟,就要两次调用模板函数。能否将延迟的时钟周期也设置成参数呢?答案是肯定的,如下图代码所示。这里定义了L,用来管理延迟的时钟周期个数,对应pragma Latency的min和max值。

原文标题:在C代码中插入寄存器

文章出处:【微信公众号:Lauren的FPGA】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

寄存器

+关注

关注

31文章

5388浏览量

121714 -

C语言

+关注

关注

180文章

7618浏览量

138438 -

代码

+关注

关注

30文章

4852浏览量

69413

原文标题:在C代码中插入寄存器

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

STC15系列常用寄存器汇总免费下载

ADS1299如何在寄存器中配置右腿驱动?

PCM5142如何在FPGA中通过SPI配置寄存器?

寄存器间接寻址和寄存器寻址的区别

微处理器中寄存器的作用

通用寄存器是什么意思

寄存器的类型和作用

寄存器的输入输出方式

寄存器故障分析

寄存器是什么意思?寄存器是如何构成的?

如何在C代码中插入寄存器?

如何在C代码中插入寄存器?

评论