美国的Pixilica已与RV64X合作,提出了一套新的图形指令集,旨在融合CPU-GPU ISA,并将其用于3D图形和媒体处理,从而为FPGA创建了开源参考实现。

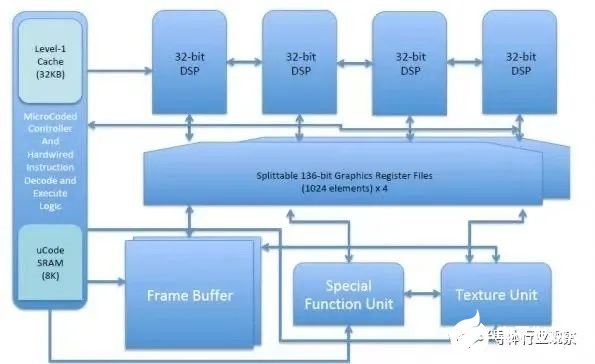

RV64X的参考实现包括了指令/数据SRAM缓存(32KB),微码SRAM(8KB),双功能指令解码器,实现RV32V和X的硬连线,用于自定义ISA的微码指令解码器,四向量ALU( 32位/ ALU –固定/浮动),136位寄存器文件(1K元素),特殊功能单元,纹理单元和可配置的本地帧缓冲区。

该实现的设计足够灵活,因此可以实现自定义pipeline阶段,自定义几何/像素/帧缓冲阶段,自定义细分器和自定义实例化操作。通过定制的可编程性和可扩展性对该实现进行了优化,使其体积小巧且面积小。

Europena工具开发商Codasip的高级市场总监Roddy Urquhart说,这是RISC-V生态系统的优势之一。

他说:“ RV64X GPU对于R5生态系统而言是一次了不起的胜利。” Codasip的Roddy Urqhart表示:“如果要创建特定于域的处理器,关键活动之一就是选择符合您软件需求的指令集架构(ISA)。”

“有些公司是从头开始创建指令集的,但是如果您有这样的ISA,则可能要付出移植软件的代价。今天,RISC-V开放式ISA可以提供一个很好的起点和一个软件生态系统,”他说。

RISC-V ISA以模块化的方式设计,使处理器设计人员不仅可以添加任何标准扩展,还可以创建自己的自定义指令,同时保持完全的RISC-V兼容性。

他仅用47条指令就指出了RISC-V(RV32I)的基本ISA。使用此基础集比创建具有类似功能的专有指令要容易得多,并且意味着该软件已经可以从RISC-V生态系统中获得。

许多用例需要乘法,这表明[M]扩展会有用,并且利用16位压缩[C]指令来提高代码密度是明智的,因此通常使用数量为101条指令的RV32IMC集。

使用RISC-V作为起点将确保直接使用通用软件(例如RTOS或协议栈)即可。如果您还需要浮点计算,那么RV32GC(G = IMAFD)指令可能是合适的,此外还包括原子[A],单精度浮点[F]和双精度浮点[D]扩展。甚至RV32GC也只有164条指令。

由于易于使用,因此标准扩展名是一个方便的选择。但是,有些可能会大大增加指令集的复杂性。例如,打包的SIMD扩展的完整集合[P]添加了331条附加指令。在许多情况下,可以使用定制指令为特定应用提供足够的增益,而潜在的硅面积和功耗开销则更低。

“为特定领域的处理器选择了起点,然后有必要弄清楚需要哪些特殊指令来满足您的计算要求。这需要仔细分析您需要在处理器核心上运行的软件。概要分析工具可以识别计算热点,一旦知道了这些热点,设计人员就可以创建自定义指令来解决这些热点,”他说。

这使设计人员可以通过尝试添加或删除指令,然后再次对软件进行性能分析以及评估更改是否实现了目标来进行迭代。这可以在开源指令集模拟器和工具链(例如GNU或LLVM)中完成,但是手工修改这些工具对于工具链专家来说是一件很麻烦的事情。

另一种方法是使用处理器描述语言描述指令集。“在Codasip Studio中,可以使用CodAL处理器描述语言创建处理器的指令精确(IA)模型。可以从以下位置自动生成包括编译器,指令集模拟器(ISS),调试器和分析器的SDK”,Urquhart说。

通过高级别描述ISA并自动生成SDK,可以快速迭代实验以扩展指令集。这样,可以为特定于域的处理器(有时称为专用指令处理器(ASIP))选择经过充分优化的ISA。与手动更改相比,自动生成SDK不仅更快,而且更不容易出错,这意味着设计过程更便宜,更可预测,从而避免了不必要的风险和路线图中断。

责任编辑:PSY

-

显卡

+关注

关注

16文章

2437浏览量

67726 -

架构

+关注

关注

1文章

515浏览量

25492 -

RISC-V

+关注

关注

45文章

2292浏览量

46210

发布评论请先 登录

相关推荐

RISC-V架构及MRS开发环境回顾

RISC-V 与 ARM 架构的区别 RISC-V与机器学习的关系

基于risc-v架构的芯片与linux系统兼容性讨论

来真的?Milk-V 即将推出的 RISC-V 设备已经能使用 AMD 卡皇 7900XTX 显卡了?!

RISC-V,即将进入应用的爆发期

观点评论 | RISC-V,伟大里程碑

里程碑!RISC-V架构进军显卡

里程碑!RISC-V架构进军显卡

评论