关于PCB的设计经验,看这边~干货满满!笔记本准备好~

1、如果设计的电路系统中包含FPGA器件,则在绘制原理图前必需使用Quartus II软件对管脚分配进行验证。(FPGA中某些特殊的管脚是不能用作普通IO的)

2、4层板从上到下依次为:信号平面层、地、电源、信号平面层;6层板从上到下依次为:信号平面层、地、信号内电层、信号内电层、电源、信号平面层。6层以上板(优点是:防干扰辐射),优先选择内电层走线,走不开选择平面层,禁止从地或电源层走线(原因:会分割电源层,产生寄生效应)。

3、多电源系统的布线:如FPGA+DSP系统做6层板,一般至少会有3.3V+1.2V+1.8V+5V。

3.3V一般是主电源,直接铺电源层,通过过孔很容易布通全局电源网络。

5V一般可能是电源输入,只需要在一小块区域内铺铜。且尽量粗(你问我该多粗——能多粗就多粗,越粗越好)

1.2V和1.8V是内核电源(如果直接采用线连的方式会在面临BGA器件时遇到很大困难),布局时尽量将1.2V与1.8V分开,并让1.2V或1.8V内相连的元件布局在紧凑的区域,使用铜皮的方式连接,如下图:

总之,因为电源网络遍布整个PCB,如果采用走线的方式会很复杂而且会绕很远,使用铺铜皮的方法是一种很好的选择!

4、邻层之间走线采用交叉方式:既可减少并行导线之间的电磁干扰(高中学的哦),又方便走线(参考资料1)。如下图为某PCB中相邻两层的走线,大致是一横一竖。

5、模拟数字要隔离,怎么个隔离法?布局时将用于模拟信号的器件与数字信号的器件分开,然后从ad芯片中间一刀切!

模拟信号铺模拟地,模拟地/模拟电源与数字电源通过电感/磁珠单点连接。

6、基于PCB设计软件的PCB设计也可看做是一种软件开发过程,软件工程最注重“迭代开发”的思想,我觉得PCB设计中也可以引入该思想,减少PCB错误的概率。

(1) 原理图检查,尤其注意器件的电源和地(电源和地是系统的血脉,不能有丝毫疏忽)

(2) PCB封装绘制(确认原理图中的管脚是否有误)

(3) PCB封装尺寸逐一确认后,添加验证标签,添加到本次设计封装库

(4) 导入网表,边布局边调整原理图中信号顺序(布局后不能再使用OrCAD的元件自动编号功能)

(5) 手工布线(边布边检查电源地网络,前面说过:电源网络使用铺铜方式,所以少用走线)

总之,PCB设计中的指导思想就是边绘制封装布局布线边反馈修正原理图(从信号连接的正确性、信号走线的方便性考虑)。

7、晶振离芯片尽量近,且晶振下尽量不走线,铺地网络铜皮。多处使用的时钟使用树形时钟树方式布线。

8、连接器上信号的排布对布线的难易程度影响较大,因此要边布线边调整原理图上的信号(但千万不能重新对元器件编号)

9、多板接插件的设计:

(1) 使用排线连接:上下接口一致

(2) 直插座:上下接口镜像对称

10、模块连接信号的设计:

(1) 若2个模块放置在PCB同一面,如下:管教序号大接小小接大(镜像连接信号)

(2) 若2个模块放在PCB不同面,则管教序号小接小大接大

这样做能放置信号像上面的右图一样交叉。当然,上面的方法不是定则,我总是说,凡事随需而变(这个只能自己领悟),只不过在很多情况下按这种方式设计很管用罢了。

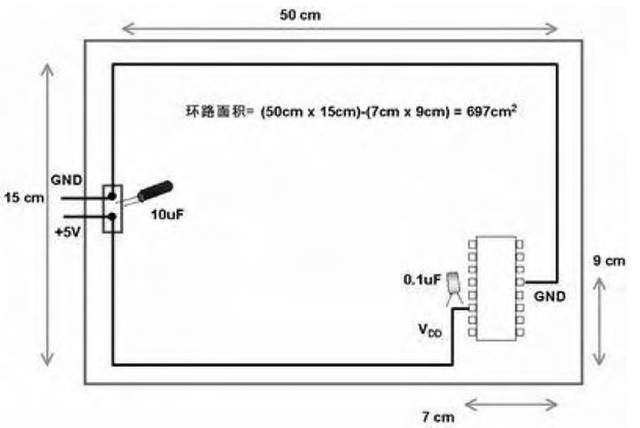

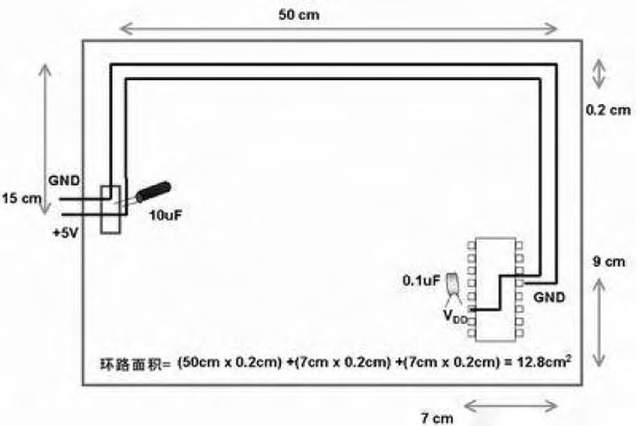

11、电源地回路的设计:

上图的电源地回路面积大,容易受电磁干扰

上图通过改良——电源与地线靠近走线,减小了回路面积,降低了电磁干扰(679/12.8,约54倍)。因此,电源与地尽量应该靠近走线!而信号线之间则应该尽量避免并行走线,降低信号之间的互感效应。

原帖来源:link.zhihu.com/?target=https%3A//bbs.elecfans.com/jishu_528858_1_1.html

-

电源

+关注

关注

185文章

17930浏览量

252562 -

dsp

+关注

关注

554文章

8065浏览量

351521 -

pcb

+关注

关注

4333文章

23210浏览量

401472 -

封装

+关注

关注

127文章

8095浏览量

143724 -

模拟信号

+关注

关注

8文章

1151浏览量

52780

发布评论请先 登录

相关推荐

加固笔记本什么意思

加固笔记本与商务笔记本的区别究竟是什么?

笔记本网络连接故障

国巨产品在笔记本电脑上的应用

用TAS5631做音频功放,需要怎么做才能使芯片准备好呢?

笔记本电脑上电感的应用

英伦科技15.6寸裸眼3D笔记本——颠覆你的视觉体验

各行业应如何挑选适合的加固笔记本?

stm8外部时钟未准备好是怎么回事?

全坚固笔记本丨工业笔记本丨三防笔记本相较于普通笔记本有哪些优势?

关于PCB的设计经验 干货满满笔记本准备好!

关于PCB的设计经验 干货满满笔记本准备好!

评论