根据摩尔定律集成电路上可以容纳的晶体管数目在大约每经过18个月便会增加一倍。这也意味着,半导体材料的改善对芯片性能的提升至关重要。

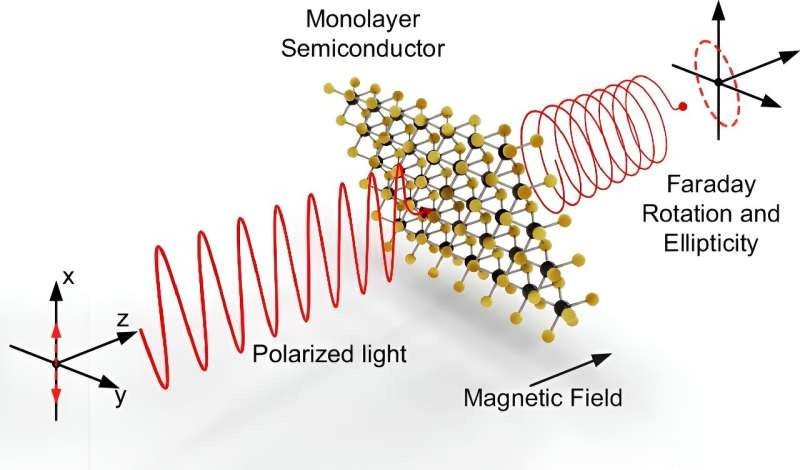

据外媒报道,美国宾夕法尼亚州立大学的科学家发表在《自然-通讯》的一项新研究显示,他们成功研制出了一种超薄二维材料晶体管,这将大大提升未来芯片的性能。

宾夕法尼亚州立大学工程学院工程科学与力学的助理教授萨普塔什·达斯(Saptarshi Das)表示,我们现在生活在一个由数据驱动的互联网世界,随之而来的是大数据对存储和处理能力的挑战。

而晶体管作为集成电路领域重要组成部分,想要存储和处理更多的数据,就需要使用更多的晶体管。但随着晶体管特征尺寸的缩小,想要进一步提升芯片性能,就需要更小更薄的半导体材料。

当前使用的三维硅材料已经用于制作晶体管有60年左右的历史,其尺寸几乎已经达到了极致。特别是5nm制程工艺后,传统晶体管微缩提升性能难以为继,这也使得硅在晶体管中的应用越来越具有挑战性。

因此,众多科学家都在新技术、新工艺、新材料等方面一直进行积极探索,发现二维材料有着先天的优势。因为这些二维材料的产生厚度能够比目前实际应用的三维硅材料薄10倍。

研究中,科学家通过使用金属有机化学气相沉积技术生长了单层二硫化钼和二硫化钨,该技术来自宾夕法尼亚州立大学的二维晶体联盟NSF材料创新平台(2DCC-MIP)。

此外,为验证新型二维晶体管的性能,科学家分析了与阈值电压、亚阈值斜率、最大与最小电流之比、场效应载流子迁移率、接触电阻、驱动电流和载流子饱和速度相关的统计指标。

达斯教授指出,经过一系列的测试证实了新晶体管的可行性,这意味着新型晶体管不仅能够让下一代芯片更快、更节能,还能够承受更多存储和数据处理性能。

据了解,台积电5nm制程工艺已经量产,而3nm制程工艺将于今年进行试产,2022年量产。此外,有消息称台积电已经成功开发了2nm制程工艺,将在2023年上半年进行风险生产,并将在2024年开始批量生产。

如果超薄二维材料晶体管进入应用阶段,那么1nm制程工艺想比也将很快实现。

责任编辑:PSY

-

芯片

+关注

关注

455文章

50732浏览量

423251 -

晶体管

+关注

关注

77文章

9684浏览量

138094 -

半导体材料

+关注

关注

11文章

532浏览量

29560

发布评论请先 登录

相关推荐

如何测试晶体管的性能 常见晶体管品牌及其优势比较

我国科学家研制出具有仿生三维架构的新型电子皮肤系统

麻省理工学院研发全新纳米级3D晶体管,突破性能极限

晶体管和二极管的区别是什么

GaN晶体管的基本结构和性能优势

上海科学家精准操控原子“人造”蓝宝石 为低功耗芯片研制开辟新路

芯片晶体管的深度和宽度有关系吗

二维材料 ALD 的晶圆级集成变化

科学家研制出一款新型柔性X射线探测器

M3芯片有多少晶体管

康奈尔大学科学家研制出5分钟快速充电锂电池

美国科学家研制出超薄二维材料晶体管 大大提升未来芯片的性能

美国科学家研制出超薄二维材料晶体管 大大提升未来芯片的性能

评论