2019 年底在旧金山举办的年度国际电子元件会议(IEDM)上,台积电公布的两个报告标志着集成电路制造迈入了EUV 光刻时代。第一个报告宣布了应用EUV 光刻技术的7 纳米世代的改良版芯片已经于2019 年正式量产,我们知道这个技术已经用在2019 年生产的麒麟990 5G 这颗有多于100 亿个晶体管的芯片上。

第二个报告宣布了2020 年量产的5 纳米世代将会有十几层的制程用EUV 光刻技术来完成,取代多于它四倍(四十几层)的193 纳米浸润式光刻技术。果然,2020 年秋天,华为mate40和苹果公司的5G 旗舰手机已经搭载台积电制造的5 纳米世代的芯片。日前,苹果更宣布用于Mac PC 的新芯片:这片5 纳米世代的芯片上含有160 亿个晶体管。EUV 光刻技术使摩尔定律得以延续。

ASML 上周财报中指出该公司于2020 年底庆祝第100 台EUV 极紫外光光刻系统出货。中国台湾目前更是全球EUV最大的装机基地。EUV 光刻技术历经20 余年的实验室研发,以及12 年的量产研发,至今成为半导体先进制程中最重要的生产工具。ASML 全球副总裁暨技术开发中心主任严涛南,正是推动EUV 应用在量产阶段的灵魂人物。

接下来我们看一下由严涛南先生撰写的文章:ASML 极紫外光(EUV)光刻技术的量产历程

ASML 全球副总裁暨技术开发中心主任严涛南博士

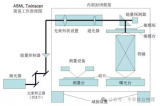

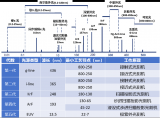

EUV 光刻技术采用锡的电浆来产生波长为13.5 纳米的光源,以及用钼硅多层反射薄膜来把光传递到芯片上。不同于一般的紫外光光刻技术,EUV 光刻技术得在低真空中运作,技术难度更高。

EUV 光刻技术以实验室形式的研发(日本,美国,欧洲,包括ASML和Cymer)已经走过了二十多年却仍达不到量产的技术要求,但也没有被放弃。理由只有一个:因为没有showstopper(明显的重大问题)。当时业界普遍认为如果EUV 能用于量产就可以让摩尔定律延续生命。这是个巨大的诱惑。台积电是全球最大的半导体代工厂,在先进制程独占鳌头,其开发所有新技术的目的只有一个:最终用于量产。而开发用于量产的EUV 光刻技术就落到了我的肩上。

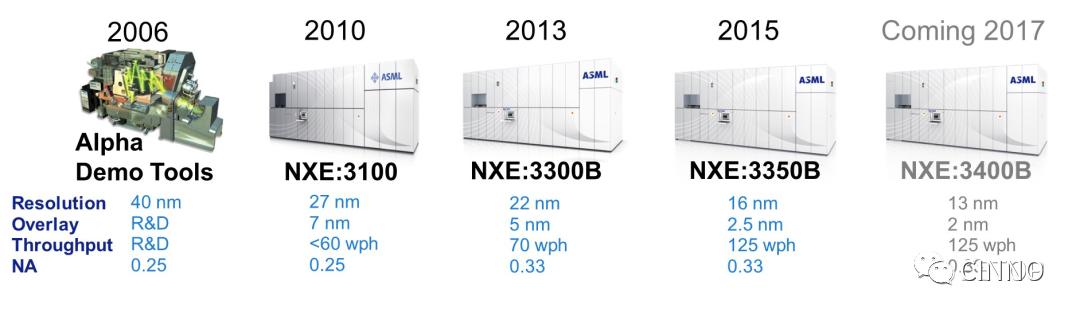

量产的要求极高,要知道EUV 光刻技术的种种瓶颈,就必须在当时仅有的EUV 光刻设备上做实验。2006 年,标志着EUV 实验室研发阶段的结束。那年,我现在的东家ASML 交出了两台EUV 样机,叫做Alphademo tool (ADT)。其中一台由纽约州的Albany 纳米中心获得,另一台落户比利时微电子研发中心(imec)──ASML 的长期合作伙伴。因为台积电是imec 的「核心伙伴」成员,我派了一位光刻技术专家去那里蹲点。尽管那台样机故障频频,但从他寄回来的芯片中,我们看到了一线希望,决定继续往下走。

2010 年的春天,在当时台积电研发组长蒋尚义博士(后为台积电共同营运长)的主导下,我们向ASML 订了一台型号为NXE:3100(数值孔径为0.25)的EUV 光刻机台。那款机型是继ADT 后的EUV 研发机台。ASML 一共做了六台,分别运往了三星、imec、英特尔、东芝、海力士和台积电。光源是美国Cymer 公司提供的。

因为是第一次采用激光电浆(laser-producedplasma,LPP)技术来产生波长为13.5 纳米的EUV 光,3100 的光源非常弱,最佳状态时只能输出10 瓦的功率,是现在量产机台(输出功率250 瓦)的二十五分之一,而且可靠性低,经常故障。但我相信它是可以进步的,因为研发中的下一代光源在Cymer 的实验室里已经演示出高于10 瓦数倍的功率,虽然只是短暂的瞬间,而不是七天二十四小时持续发光。

而且那时我们第一要关心的不是光源的输出功率,而是光刻机台镜头的解析度。镜头是ASML 的合作伙伴ZEISS 做的。虽然数值孔径都是0.25,NXE:3100 的镜头比起ADT 来有很大的进步,我们看到它已经可以在芯片上曝出10 纳米世代需要的图案!再者,ASML 的下一代机型NXE:3300 有更高的0.33 的数值孔径,意味着更高的解析度。还是在蒋先生的全力支持下,我们订购了NXE:3300,继续往前冲。

2012 年底,张忠谋董事长问我:「你觉得EUV 成功的机率有多少?」我答「80%」,他说:「那你很乐观噢!某人说只有50%」。回想起来,当时在大老板前面讲出80% 的成功机率确实是有点胆大。但我还是信心满满。为什么?

义无反顾,全力以赴,合作无间

ASML 从一开始就认知到开发EUV 量产光刻机台是个极高风险但又是高回报的事业。而且延续摩尔定律是它的社会责任。因为风险极高,所以ASML 的竞争对手从一开始就没有打算要开发量产的EUV 技术。它的社长对我说:「EUV 是不会成功的;ASML 会蚀掉所有的开发成本」。其实那时有这样的想法是很正常的,持这样观点的人也很多。

但ASML 不是一般的公司。决定它在EUV 光刻机台技术上成功的因素有三个:

决定开发EUV 光刻机台后,公司将全力以赴,投入了所有可能的资源来降低风险,使它成功。

技术长Martin van den Brink 亲自挂帅,事无巨细,都一一过问。

和像台积电这样的重要客户共同开发。

对台积电来说也一样。因为已经决定了,就要全方位的投入。蒋先生和我们分享过这样一段话:「我一生中做过许多技术方面的决定。我决定的方向可能当时来说不是最好的。但是我一旦决定了,就会把所有的资源投入到那里,让它成功。另一个或许是当时更好的方向已经无关紧要了,因为它已经出局了」。

我义无反顾,全心全意地投入EUV 的开发。每天一定会穿好无尘衣进入无尘室去看我的机器:了解它们的状况,做出相应的决定。公司内部有人说我是公司里唯一一位每天进无尘室的处长。不知是褒义还是贬义。但我知道:绝对不能只听报告,然后在办公室或会议室里隔空指挥,特别是当机器的可靠性还很低时。为了让机器的利用率达到最高,我需要看了机器当时的状况后,决定让它接着曝实验芯片,或是把它拉下来做机器本身的实验。为了赶进度,我们和ASML 共同开发:很多实验都是在荷兰或美国初步进行一下,然后直接在台积电的3300 光刻机台上完成的。

在通往量产的路上,人们最担心的是光源的输出功率是否最终能达到250 瓦。这是量产机台所必须有的。因为单价很高,EUV 光刻机台要有高的稼动率来压制芯片的生产成本。上面提到,光刻机台最要紧的是镜头的解析度。那时ZEISS 做的镜头已经不是问题。光源的输出功率变成了主要问题。

2013 年十月底,我们的第一台NXE:3300 开始曝光,但从十一月开始的好长一段时间,光源的功率都无法超越10 瓦。透过不断的实验,到了2014 年第二季,功率爬到了40 瓦左右。然后接着一连串的实验都没法让它继续提升:主要表现在高于40 瓦输出功率的稳定性欠佳。整个夏天,我们和ASML 在新竹、荷兰、美国不停地做实验。

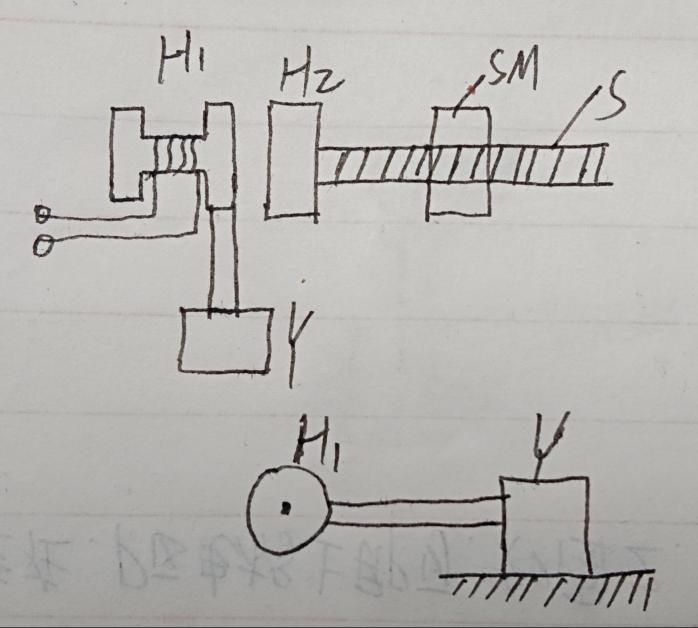

EUV 光的产生是用二氧化碳激光每秒5 万次去轰击液态锡滴。出来的EUV 光通过一个直径为0.65 公尺的椭球反光镜送进光刻机台里头。锡滴位于椭球反光镜的一个焦点,机器的进口位于它的另一个焦点。所以,保持这块反光镜不被雾化就成了关键中的关键。

为什么会雾化?因为锡滴被激光轰击后气化,在腔内扩散,会沉积在镜子上。因此,我们在反光镜周围输入氢气。EUV 光能把氢分子分离为氢原子。而氢原子又能与锡结合,变成气态的氢化锡,然后被抽出腔体。不让反光镜雾化的关键是把二氧化碳激光的功率,氢气的流量和氢气的压力调到最佳组合。当然还有其他关键的地方。总之,这个十亿美元的游戏就是要怎样把EUV 光的稳定的输出功率调高,再调高,调得更高。

EUV光源

2014 年10 月的一个晚上是个分水岭。 那晚我在公司餐厅匆匆用了餐,就进入无尘室和ASML 的伙伴们一起用Cymer 那里先调出来的初步数据做一个崭新的实验。 经过参数的微调,输出功率持续上升。 九点过后,我们第二台3300 上的EUV 光源第一次输出了90瓦的稳定功率。 这是全世界的第一次! 能达到90 瓦,250 瓦就希望很大,因为只差不到三倍,而我们已经从10 瓦走到了90 瓦,那是九倍。 我立即意识到,EUV 光刻技术的量产应该会成功。 顿时一股暖流涌上心头,我一生都会记得那一个晚上。

接下来的任务更加艰巨:为了证明光源的输出功率不只是最佳的的实验数据,我被长官要求证明这部光刻机台能连续一个月平均每天曝光五百片芯片。我去和ASML 商量。我们决定:加快步伐把锡滴管和椭球反光镜的更换频率降低,因为它们的更换在那个时候需要几十个小时。期间光刻机台不能曝光。其中最重要的改进是把锡滴的体积减半,来减少锡滴管的消耗及椭球反光镜的污染,从而降低它们的更换频率,但不能让每次激光轰击产生的EUV 能量降低。

台积电和ASML 成立了One Team,日夜不停地改进光源的各项参数。这项任务在2015 年上半年完成了。在那之后,One Team 在各个方面都取得了进步,包括一次又一次地改进各项参数来延长反光镜的寿命。在这里我要感谢我以前的EUV 研发团队及和我们紧密合作的ASML 的伙伴──我现在的同事们。

打造一个全新的生态系统

以上的工作是艰难的,但是还是不足的。EUV 光刻量产技术是到目前为止半导体工业最大的开发计划,它的成功需要整个半导体业界的力量。为了说服ASML 开发,从2013 年起的五年内,台积电、三星、英特尔加在一起付给了ASML 超过十亿欧元研发费用来共襄盛举。为了达成此任务,ASML 援助它的供应商:2012 年,它花了二十五亿美元收购了美国Cymer 公司;2016 年,它花了十亿欧元入股德国ZEISS 公司,并在之后的六年内提供ZEISS 七点六亿欧元研发费用。这些举动都是为了确保EUV 光刻技术的成功。

要成功将EUV 技术导入芯片的量产阶段,除了光刻机台外,还需要开发一个EUV 光刻技术专门的生态系统。这个系统包括光阻与光罩。其实光罩本身就是一个子系统,它在台积电的开发也是由我负责。

当初,虽然193 纳米光阻那时已是成熟的技术,也是日本供应商的天下,但是由于已看到EUV 要走到量产不是一、两年的事,一般光阻供应商都不愿意在EUV光阻上投入太多资源。唯有JSR 有战略眼光。在小柴社长的支持下,我们和JSR 进行了长期的不间断的合作,确保了我们的EUV 光刻机台有光阻可用,以及EUV 光阻本身的开发。

光罩技术的开发更加困难。唯二的光罩基材(maskblank)供应商也是日本公司。这里要提一下Hoya 公司。我们努力地合作,但它做的EUV 光罩基材一开始充满了缺陷。而且它自己没法全然知道,因为它自己的检测设备解析度没有我们的高。所以他们的工程师要靠我们的反馈来改进他们的制程。Hoya 的光罩基材事业部部长堀川先生提出请求,让我们每个月能有固定的采购来维持它小小的EUV光罩基材生产线。为了量产,不能只用实验室里做出来的东西; 有了生产线,制程才能改进。

我们答应了他的请求。为了提高光罩基材缺陷的检测解析度,我们和KLA 的工程师合作,把一台光罩检测机改良为光罩基材缺陷专用的检测机。然后我们可以一次次地反馈给Hoya 的工程师们,而他们就按照我们的反馈调参数,又一次次地把新的光罩基材送过来。到了2016年,光罩基材的缺陷已经降到十到二十颗左右。

我们也和本地供应商合作,例如和家登精密合作开发EUV 用的双层光罩盒。与此同时,台积电2011 年加入的国际半导体联盟SEMATECH 及日本半导体联盟EIDEC,也来共襄盛举。这两个组织都百分之百致力于EUV 生态系统的开发。ZEISS 的EUV AIMS 光罩影像机及Lasertec 的EUV 光罩基材检测机器就是在这些联盟的资助下完成开发的。

总之,EUV 量产的开发是光刻机台加上生态系统再加上制程的开发,缺一不可。在这里应该感谢以前台积电EUV 团队里的每一位成员的辛勤付出,ASML 同事们顽强的拼搏,其他半导体公司的相关研发人员的不懈努力,以及所有开发EUV 相关技术的供应商及研究单位。EUV 量产的成功归功于我们的共同努力,唯有如此,这个技术才有成功的今天。

2015 年春SPIE 国际光电工程学会年会上有人问我:「你们的B 计划是什么?」我回答:「我们没有 B 计划」,因为那时我已坚信我们的A 计划会成功。

EUV 挽救了摩尔定律

二十多年的前期研发不算,仅量产用的EUV 光刻技术的开发就走了足足十二年。ASML 更是直接投入了大量人力物力,这还不算ASML 在光刻机台方面多年的技术积累和产业界的全力合作。所以大事业的成功是成年累月不懈的努力。是不可能一步登天,一蹴而就的。

EUV 光刻技术最终是成功了。摩尔定律的生命被延续了。不然,集成电路的进步会在2018 年量产的7 纳米那代就嘎然而止了。而现在呢,EUV 光刻技术已经应用于7 及5 纳米世代的量产。2020 年十月,台积电魏哲家执行长宣布:3 纳米世代将于2022 年下半年投入量产。正如193 纳米浸润式光刻技术让摩尔定律延续了十年(五个世代的集成电路),EUV 光刻技术也将会让摩尔定律至少延续再一个十年。届时,集成电路制造已经走到了埃米世代了。

原文标题:挽救摩尔定律:EUV光刻机20年量产历程

文章出处:【微信公众号:传感器技术】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

458文章

51518浏览量

429419 -

光刻机

+关注

关注

31文章

1159浏览量

47723 -

EUV

+关注

关注

8文章

609浏览量

86332

原文标题:挽救摩尔定律:EUV光刻机20年量产历程

文章出处:【微信号:WW_CGQJS,微信公众号:传感器技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

击碎摩尔定律!英伟达和AMD将一年一款新品,均提及HBM和先进封装

摩尔定律是什么 影响了我们哪些方面

组成光刻机的各个分系统介绍

日本首台EUV光刻机就位

光刻机的工作原理和分类

“自我实现的预言”摩尔定律,如何继续引领创新

台积电A16制程采用EUV光刻机,2026年下半年量产

英特尔突破技术壁垒:首台商用High NA EUV光刻机成功组装

光刻机的发展历程及工艺流程

ASML 首台新款 EUV 光刻机 Twinscan NXE:3800E 完成安装

20年EUV光刻机量产历程挽救摩尔定律

20年EUV光刻机量产历程挽救摩尔定律

评论