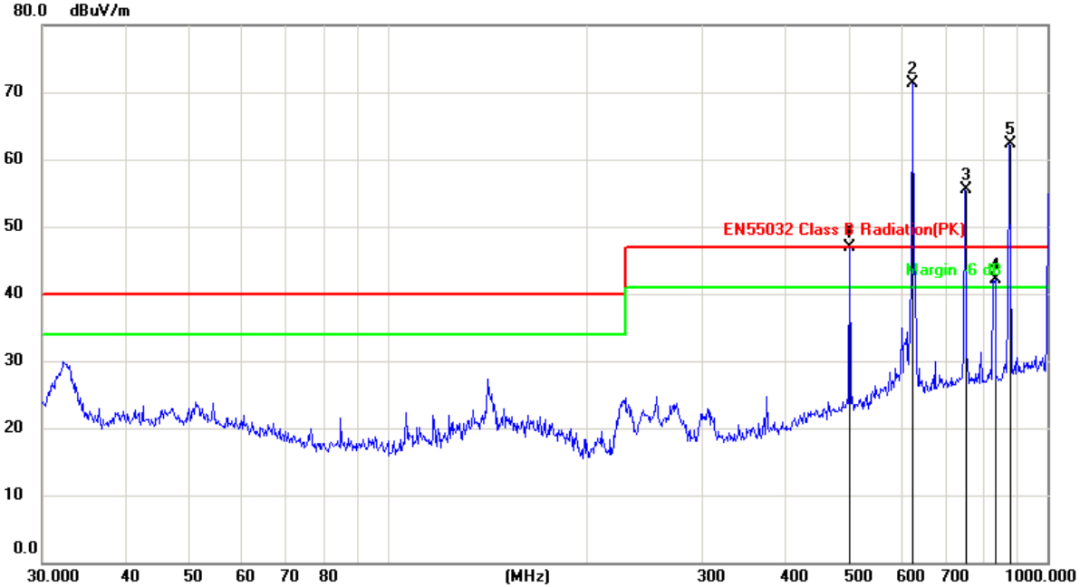

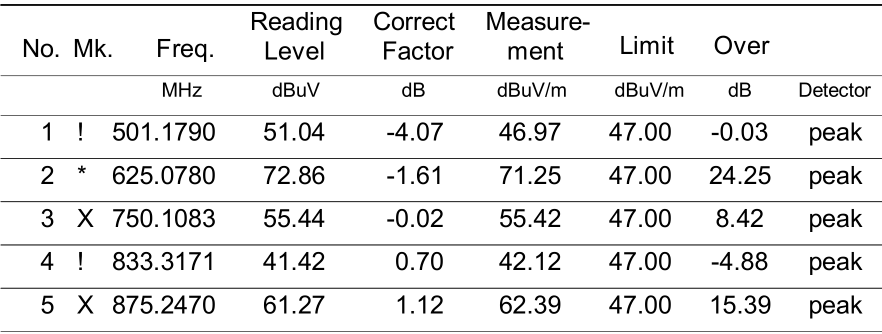

在电磁兼容的辐射发射测试中,最常见的就是时钟辐射超标(如下图所示)。可以说70%的辐射超标都是时钟问题引起的,因为时域中周期性的信号对应频域中离散的频谱,所以时钟能量比较集中,这在频谱上的表现就是:时钟频点(时钟基频以及倍频)上能量很高,而非时钟频点几乎没有能量。

那么我们如何分析测试数据并且改善辐射呢?

二测试数据分析

分析辐射数据之前,我们先简单了解一下时钟最基本的一个特点:倍频。如下图所示,常见的梯形波在频域上是有很多间隔规律的单支的,比如一个24MHz的摄像头时钟,那么f0=24MHz,在频域上每隔24MHz就会有一个单支能量很高(24MHz,48MHz,72MHz,96MHz,120MHz……)。

所以想要从测试数据上分析时钟源头,就需要计算出每个相邻时钟单支的频率间隔△f,f0=△f。比如上述测试数据中:

f5-f3=875.2470-750.1083≈125MHz

f3-f2=750.1083-625.0780≈125MHz

f2-f1=625.0780-501.1790≈125MHz

从计算结果中可以知道,1号点、2号点、3号点、5号点是125MHz时钟的倍频(4号点833MHz是实验室中手机的噪声,可以忽略)

三辐射超标的原因

分析出了超标的时钟频率,就可以很轻松的通过频谱仪或者原理图和pcb找到时钟来自哪一个芯片的哪个时钟信号。但是这并不代表我们可以很好解决时钟问题,因为时钟辐射的路径多种多样,又可能包含差模、共模辐射。即使找到了辐射路径,也不一定能降低辐射,因为时钟是我们电子产品需要的有用信号,很多滤波手段会影响信号完整性,从而导致功能异常或者降低稳定性和一致性。这就需要我们在电磁兼容和产品性能中取一个平衡,这让很多工程师越来越憔悴。

不过别慌,只要我们沉住气,一步一步分析问题,总有海阔天空、枯木逢春的一天。接下来我们看看时钟辐射超标的几个常见原因:

1.排线是时钟辐射的良好天线,比如屏排线,摄像头排线,喇叭排线等。很多排线本身没有时钟线,但是会耦合到时钟噪声,所以也需要注意,无论是输入排线(①)还是输出排线(②),都要在接口处做好滤波措施,如有必要,最好再加上磁环。另外,排线的屏蔽接地是非常重要的,一根屏蔽接地良好的排线,可以降低10-30db的辐射。

2.一般CPU都会有参考时钟,如果参考时钟晶体附近有长走线,那么时钟噪声很容易耦合到长走线,从而辐射出去。所以走线要远离晶体,晶体附近也要做好包地处理。

3.很多数据线上也会有时钟噪声(④和⑥),一般在数据线源端做好RC滤波,R取值22或者33欧姆(也可以考虑换成磁珠,增强滤波),C取值33pf以内。

4.时钟走线本身辐射是最强的(⑤和⑦),所以一定要全程包地线处理,走线越短越好,源端滤波最好采用磁珠+电容的方式,磁珠取值60-600欧姆@100MHz,电容取值33pf以内。因为时钟超标一般是100-1000MHz,磁珠用于降低100-500MHz的噪声(500Mhz以上也有较好的滤波效果),电容用于降低500-1000MHz的噪声。

5.PCB上的长走线(⑧)有时候也带有较强的时钟噪声,因为芯片内部电路设计问题,或者pcb走线设计有问题会耦合到时钟噪声。对于长走线,应该用频谱仪探针看看是否有噪声,然后进行滤波。这类走线如果速率很低或者对信号完整性要求很低,就可以加大滤波参数,所以较好解决。

6.靠近时钟线的走线(⑨)很容易耦合到噪声,所以时钟线未包地的情况下,其他走线要远离时钟等高速信号,降低耦合程度。

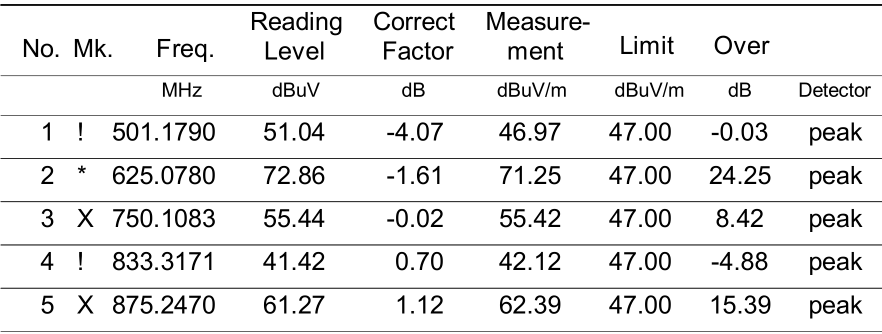

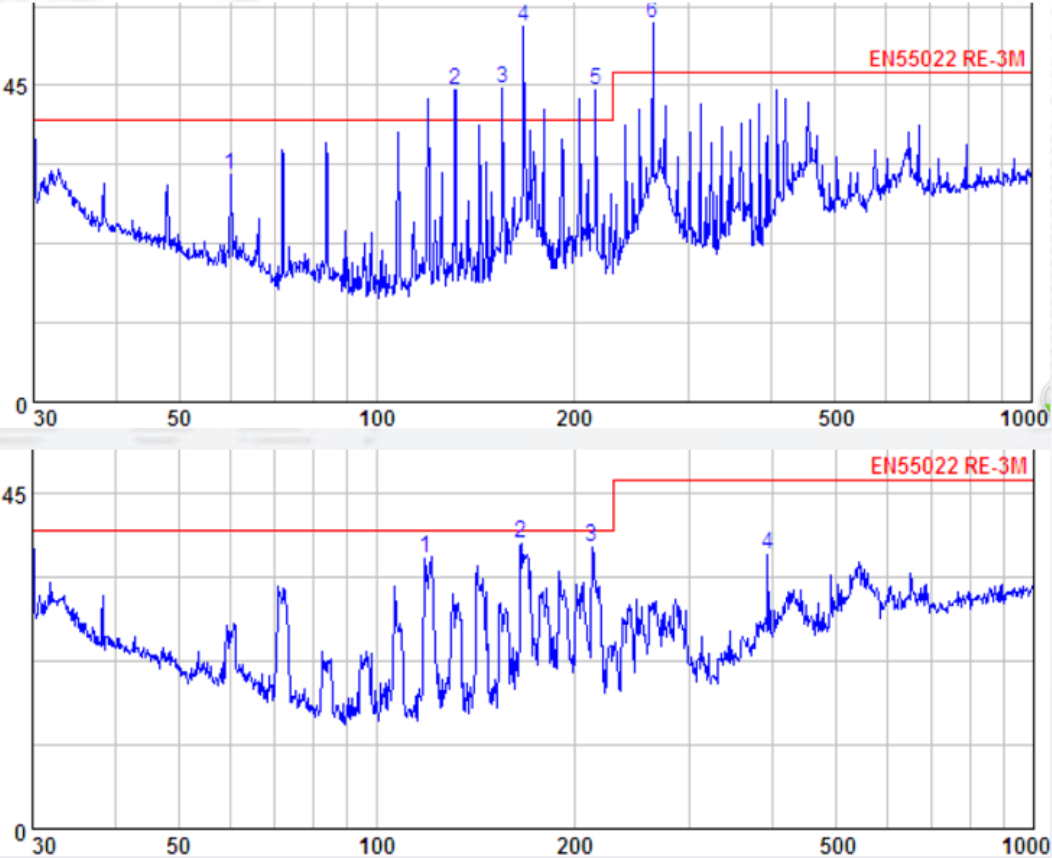

7.因为时钟滤波参数不能太大,所以很多时钟我们即使知道问题出在哪也无能为力。这个时候就可以考虑在晶体(⑩)上加展频IC,可以有效降低辐射。下图是增加展频前后的测试数据。

四结语

时钟辐射问题可以通过分析测试数据找到时钟源头,但是有时候未必能有效解决问题,因为超标的原因很多,我们不能一直盯着时钟走线疯狂滤波。这个时候就需要我们耐心分析,剥丝抽茧,拨开云雾见天明。

原文标题:EMC小结之时钟辐射问题

文章出处:【微信公众号:韬略科技EMC】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

电磁兼容

+关注

关注

54文章

2116浏览量

100480 -

emc

+关注

关注

177文章

4458浏览量

192327

原文标题:EMC小结之时钟辐射问题

文章出处:【微信号:TLTECH,微信公众号:韬略科技EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高频交直流探头在EMC预兼容测试与噪声分析中的实战应用

改善EMC的PCB设计原理

高压起弧试验机测试数据的深度解读:从电弧痕迹到材料失效分析

电线耐干湿电弧试验机的测试数据精准采集与分析方法

普迪飞 Exensio®数据分析平台 | Test Operations解锁半导体测试新纪元

如何分析EMC测试数据并且改善辐射?

如何分析EMC测试数据并且改善辐射?

评论