CMOS的重要性自然不再需要小编再多论及,在往期CMOS文章中,小编对CMOS故障、CMOS和CCD的区别等内容有所介绍。为增进大家对CMOS的了解程度,本文将基于两点对CMOS予以阐述:1.CMOS集成电路特点,2.CMOS和TTL的优缺点介绍。如果你对CMOS具有兴趣,不妨继续往下阅读哦。

一、CMOS集成电路的特点

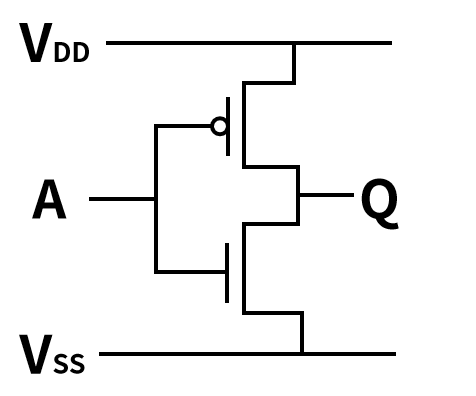

1.CMOS集成电路功耗低

CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。

2.CMOS集成电路工作电压范围宽

CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。国产CC4000系列的集成电路,可在3~18V电压下正常工作。

3.CMOS集成电路逻辑摆幅大

CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

4.CMOS集成电路抗干扰能力强

CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。随着电源电压的增加,噪声容限电压的绝对值将成比例增加。对于VDD=15V的供电电压(当VSS=0V时),电路将有7V左右的噪声容限。

5.CMOS集成电路输入阻抗高

CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

6.CMOS集成电路温度稳定性能好

由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。一般陶瓷金属封装的电路,工作温度为-55~+125℃;塑料封装的电路工作温度范围为-45~+85℃。

7.CMOS集成电路扇出能力强

扇出能力是用电路输出端所能带动的输入端数来表示的。由于CMOS集成电路的输入阻抗极高,因此电路的输出能力受输入电容的限制,但是,当CMOS集成电路用来驱动同类型,如不考虑速度,一般可以驱动50个以上的输入端。

8.CMOS集成电路抗辐射能力强

CMOS集成电路中的基本器件是MOS晶体管,属于多数载流子导电器件。各种射线、辐射对其导电性能的影响都有限,因而特别适用于制作航天及核实验设备。

9.CMOS集成电路可控性好

CMOS集成电路输出波形的上升和下降时间可以控制,其输出的上升和下降时间的典型值为电路传输延迟时间的125%~140%。

10.CMOS集成电路接口方便

因为CMOS集成电路的输入阻抗高和输出摆幅大,所以易于被其他电路所驱动,也容易驱动其他类型的电路或器件。

二、TTL与CMOS的优缺点

第一个也是最常被谈论的是功耗-TTL比CMOS消耗更多的电能。

这在某种意义上是正确的,TTL输入只是双极晶体管的基础,双极晶体管需要一些电流来打开它,输入电流的大小取决于内部的电路。当许多TTL输入连接到一个TTL输出时,这就成了一个问题,而TTL输出通常只是一个上拉电阻或一个驱动性能较差的高压侧晶体管。

另一方面,CMOS晶体管是场效应的,换句话说,栅极处的电场足以影响半导体通道的传导。理论上,除了栅极的小漏电流(通常为皮卡或毫安量级)外,不会产生电流。然而,这并不是说即使在更高的速度下,同样的低电流消耗也是正确的。CMOS芯片的输入具有一定的电容,因此上升时间有限。为了确保在高频下上升时间很快,需要一个大电流,在MHz或GHz频率下可以达到几安培。这种电流只在输入必须改变状态时才被消耗,而TTL的偏置电流必须与信号一起存在。

在输出方面,CMOS和TTL各有优缺点。TTL输出要么是图腾柱,要么是上拉。有了图腾杆,输出只能在轨道0.5V范围内摆动。然而,其输出电流远高于CMOS芯片。同时,CMOS输出可以与电压控制电阻器相比较,根据负载情况,可以在电源轨的毫伏范围内输出。然而,两个led的输出电流往往很有限。

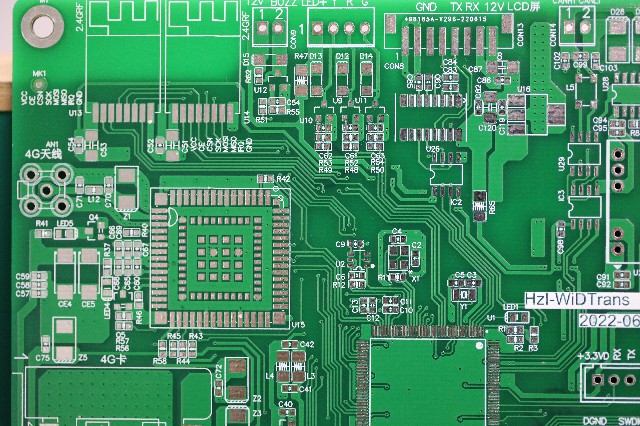

由于其较小的电流要求,CMOS逻辑非常适合小型化,数百万个晶体管可以封装到一个小区域,而不需要过高的电流。

与CMOS相比,TTL的另一个重要优势是其耐用性。场效应晶体管依赖于栅极和沟道之间的薄氧化硅层来提供它们之间的隔离。这种氧化层厚度为纳米,击穿电压很小,即使在高功率fet中也很少超过20V。这使得CMOS对静电放电和过电压非常敏感。如果输入是浮动的,它们会慢慢积累电荷并引起输出状态的假变化,这就是为什么CMOS输入通常被上拉、下拉或接地。TTL在很大程度上不受这个问题的影响,因为输入端是一个晶体管基极,它的作用更像一个二极管,由于它的阻抗较低,对噪声不太敏感。

责任编辑人:CC

-

CMOS

+关注

关注

58文章

6236浏览量

243438 -

TTL

+关注

关注

7文章

557浏览量

75063 -

CMOS集成电路

+关注

关注

4文章

41浏览量

14693

发布评论请先 登录

AD7524:8位CMOS缓冲乘法DAC的深度解析

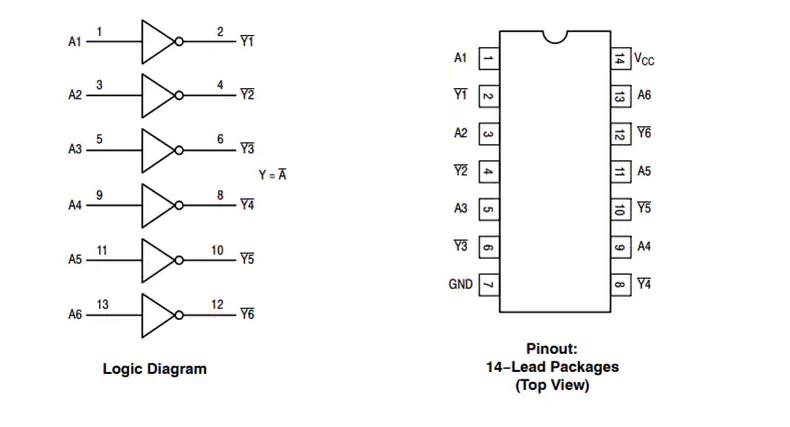

深入解析ON Semiconductor MC74VHC04与MC74VHCT04A CMOS六路反相器数据手册

2.4 GHz CMOS WLAN 射频前端集成电路,带 PA、带旁路的 LNA 以及用于 WLAN 和蓝牙®信号功能的 SP3T 开关 skyworksinc

CMOS集成电路中闩锁效应的产生与防护

双通道采用SOIC-8封装的15MBd CMOS光耦合器-ICPL-075L

CMOS图像传感器的制造步骤

VirtualLab:CMOS传感器仿真

一款双通道采用SOIC-8封装的25MBd CMOS光耦合器-ICPL-074L

CMOS工艺流程简介

电路设计异常要考虑:电流倒灌、热插拔、过流保护、过压保护、上电电流

PCBA 表面处理:优缺点大揭秘,应用场景全解析

CMOS集成电路的特点,TTL与CMOS的优缺点

CMOS集成电路的特点,TTL与CMOS的优缺点

评论