点沙成金的半导体行业

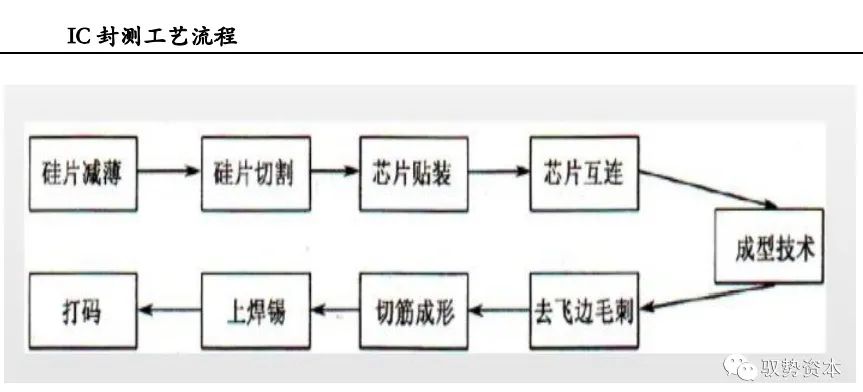

IC封装就是把Foundry生产出来的芯片裸片(die)封入一个密闭空间内,受外部环境、杂质和物理作用力的影响,同时引出相应的引脚,最后作为一个基本的元器件使用。IC测试就是运用各种方法,检测出在制造过程中,由于物理缺陷导致的不合格芯片样品,主要分为两个阶段:一是进入封装之前的晶圆测试;二是封装后的IC成品测试。

半导体封测主要流程包括贴膜、打磨、去膜再贴膜、切割、晶圆测试、芯片粘贴、烘焙、键合、检测、压膜、电镀、引脚切割、成型、成品测试等。封装的核心在于如何将芯片I/O接口电极连接到整个系统PCB板上,键合是关键环节即用导线将芯片上的焊接点连接到封装外壳的焊接点上,外壳上的焊接点与PCB内导线相连,继而与其他零件建立电气连接。

1、OSAT将成为封测行业的主导模式

集成电路封测属于IC产业链偏下游的行业,通常封装和测试都是一体的,即做完封装后直接进行产品的测试。随着人们对集成电路品质的重视,也有测试产业也逐步从封测产业独立出来,成为不可或缺的子行业。

IDM和OSAT(Outsourced Semiconductor Assembly&Test,半导体封装测试代工模式)是半导体封测产业的两种主要模式。Gartner数据显示,OSAT模 式一直呈增长态势,2013年以后OSAT模式的产业规模就超过了IDM模式,2018年OSAT和IDM模式市场占比分别为54%、46%,伴随着半导体行业垂直分工趋势,OSAT模式将成为封测行业的主导模式。

2、从传统封装技术到先进封装技术

集成电路封装技术的发展是伴随着集成电路芯片的发展而发展起来的,通常而言,“一代芯片需要一代封装”。封装的发展史也是芯片性能不断提高、系统不断小型化的历史。随着集成电路器件尺寸的缩小和运行速度的提高,对集成电路也提出新的更高要求。

回顾封装产业发展历程,我们按照封装技术进程,以 2000年为节点,将封装产业分为传统封装阶段和先进封装阶段。

传统封装:

传统封装技术发展又可细分为三阶段。其特点可总结如下,技术上:To-DIPLCC-QFP-BGA-CSP;引脚形状:长引线直插-短引线或无引线贴装-球状凸点焊接;装配方式:通孔封装-表面安装-直接安装;键合方式:引线连接-焊锡球连接。

阶段一(1980以前):通孔插装(Through Hole,TH)时代,其特点是插孔安装到PCB上,引脚数小于 64,节距固定,最大安装密度10引脚/cm2,以金属圆形封装(TO)和双列直插封装(DIP)为代表;

阶段二(1980-1990):表面贴装(Surface Mount,SMT)时代,其特点是引线代替针脚,引线为翼形或丁形,两边或四边引出,节距1.27-0.44mm,适合3-300条引线,安装密度10-50引脚/cm2,以小外形封装(SOP)和四边引脚扁平封装(QFP)为代表;

阶段三(1990-2000):面积阵列封装时代,在单一芯片工艺上,以焊球阵列封装(BGA)和芯片尺寸封装(CSP)为代表,采用“焊球”代替“引脚”,且芯片与系统之间连接距离大大缩短。在模式演变上,以多芯片组件(MCM)为代表,实现将多芯片在高密度多层互联基板上用表面贴装技术组装成多样电子组件、子系统。

先进封装:自20世纪90年代中期开始,基于系统产品不断多功能化的需求,同时也由于CSP封装、积层式多层基板技术的引进,集成电路封测产业迈入三维叠层封装(3D)时代。具体特征表现为:(1)封装元件概念演变为封装系统;(2)单芯片向多芯片发展;(3)平面封装(MCM)向立体封装(3D)发展(4)倒装连接、TSV 硅通孔连接成为主要键合方式。具体的先进封装囊括倒装、晶圆级封装以及POP/Sip/TSV等立体式封装技术,其特征分述如下:

3D封装技术:MCM技术集成多个集成电路芯片实现封装产品在面积上的集成,那么让芯片集成实现纵向上的集成则是3D封装技术的主要功效。3D封装可以通过两种方式实现:封装内的裸片堆叠和封装堆叠。封装堆叠又可分为封装内的封装堆叠和封装间的封装堆叠。3D封装会综合使用倒装、晶圆级封装以及POP/Sip/TSV等立体式封装技术,其发展共划分为三个阶段:第一阶段采用引线和倒装芯片键合技术堆叠芯片;第二阶段采用封装体堆叠(POP);第三阶段采用硅通孔技术实现芯片堆叠。

倒装芯片技术(Flip Chip,FC)不是特定的封装类型,而是一种管芯与封装载体的电路互联技术,是引线键合技术(Wire Bond,WB)和载带自动键合技术(Tape Automated Bonding,TAB)发展后的更高级连接技术。WB与TAB的芯片焊盘限制在芯片四周,而FC则将裸芯片面朝下,将整个芯片面积与基板直接连接,省掉了互联引线,具备更好的电气性能。

圆片级封装技术(Wafer Level Package,WLP)技术是在市场不断追求小型化下,倒装技术与SMT和BGA结合的产物,是一种经过改进和提高的CSP。圆片级封装与传统封装方式(先切割再封测,封装后面积至少>20%原芯片面积)有很大区别,WLP技术先在整片晶圆上同时对众多芯片进行封装、测试,最后切割成单个器件,并直接贴装到基板或PCB上,因此封装后的体积等于芯片原尺寸,生产成本也大幅降低。WLP又可称为标准WLP(fanin WLP),随后又演化出扩散式WLP(fan-out WLP),是基于晶圆重构技术,将芯片重新布置到一块人工晶圆上,然后按照与标准WLP工艺蕾丝步骤进行封装。

堆叠封装(Package on Package,PoP)属于封装外封装,是指纵向排列的逻辑和储存元器件的集成电路封装形式,它采用两个或两个以上的BGA堆叠,一般强抗下逻辑运算位于底部,储存元器件位于上部,用焊球将两个封装结合,主要用于制造高级便携式设备和智能手机使用的先进移动通讯平台。

硅通孔技术(TSV,Through-Silicon-Via)也是一种电路互联技术,它通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连。与以往的IC封装键合和使用凸点的叠加技术不同,TSV能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,并且大大改善芯片速度和低功耗的性能。TSV是2.5D和3D封装的关键技术。

系统级封装技术(System in a Package,SiP)是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。与系统级芯片(System On a Chip,SoC)相对应。不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而 SOC则是高度集成的芯片产品。

整体而言,封装技术经历了由传统封装(DIP、SOP、QFP、PGA等)向先进封装(BGA、CSP、FC、WLP、TSV、3D堆叠、SIP等)演进。目前全球集成电路主流封装技术为第三代封装技术,即BGA(球栅阵列封装)、CSP(芯片级封装)、FC(倒装芯片)。其中倒装芯片封装技术被认为是推进低成本、高密度便携式电子设备制造所必需的项工艺,已广泛应用于消费类电子领城。而第四代封装技术,WLP(晶圆级封装)、TSV(硅通孔技术)、SIP(系统级封装)等仍在小规模推广中,在技术升级下它们亦将会成为未来封装方式的主流。

3、国内封装产业率先突围

全球IC封测产业规模一直保持着个位数增长的态势(除2014年激增导致2015年数据略降外),2017年全球封测行业收入533亿美元,占半导体行业整体收入的13%,2018年全球封测行业收入预计560亿美元,保持4.5%的增速。根据前25名封测厂商所在区域统计,中国台湾以53%的销售额占据了封测行业的半壁江山,紧随其后的为中国大陆和美国,分别以21%和15%的份额排名第二、第三,马来西亚、韩国、新加坡、日本则分别占据4%、3%、2%、2%的份额。从市场占比来看,国内封装企业已经进驻全球第一梯队,具备一定的国际竞争力。

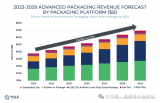

当前摩尔定律逐渐到头,IC成本不断上升,促使业界开始依靠IC封装来扩大在超越摩尔时代的获利。因此,得益于对更高集成度的广泛需求,以及下游5G、消费类、存储和计算、物联网、人工智能和高性能计算等大趋势的推动,先进封装将成为推进IC封装产业的主推动力。根据Yole数据,2018年先进封装与传统封装占比分别为42.1%和57.9%,同时预测,截止2024年行业整体复合增长率为5%,其中,先进封装占比将达到49.7%,符合增长率达8.2%,占据行业整体份额的一半;传统封装则保持2.4%的复合增长率,份额逐步缩小。

从先进封装技术平台细分来看,倒转技术应用最广,占据75%左右的市场份额,其次为Fan-in WLP和Fan-out WLP。从未来发展速度来看,Yole预测2018-2024年,2D/3D TSV技术、嵌入式封装技术Embedded Die(使用复合基板)、Fan-out WLP因未来广阔的市场空间而增速较快,分别将保持26%、49%、26%的复合增长率。其中Fan-out将主要用于移动互联、网络、汽车领域;2D/3D TSV技术将主要应用于人工智能(AI)/机器学习(ML)、高性能计算(HPC)、数据中心、图像传感器、微机电领域;Embedded Die技术则主要应用于汽车和医疗领域。

受益于下游消费电子产业的崛起以及半导体产业转移趋势,中国IC封测行业快速发展,自2015年以来,保持两位数增长趋势,远高于全球增速水平。据前瞻产业研究院发布的统计数据显示,2018年我国集成电路封装测试行业市场规模突破2000亿元,达到了2193.9亿元,同比增长16.1%。

中国先进封装占比低但成长迅速。虽然近年来国内领先企业在先进封装领域取得较大突破,先进封装的产业化能力基本形成,但在高密度集成等先进封装方面中国封装企业与国际先进水平仍有一定差距。目前我国IC封装市场中,还是DIP、QFP、QFN/DFN等传统封装技术占主体,据集邦咨询顾问统计,2018年中国先进封装营收约为526亿元,占中国IC封测总营收的25%,远低于全球42.1%的比例。国内先进封装的市场份额也仅占全球10%左右的市场份额。Yole数据显示,中国封测企业2018年在先进封装领域加速提高产能,增长率高达16%,是全球的2倍,其中长电科技在收购星科金鹏之后,其先进封装产品出货量全球占比7.8%(2017年),排名第三,仅次于英特尔和矽品。

收购兼并是国内封测企业起步的契机。国内封装企业以长电科技与通富微电为代表,2018年市场规模分别为233.36亿元和71.64,分别占国内市场份额的11%和3%。封装行业技术门槛低,需要通过不断加大投资来提高边际产出,因此行业公司往往追求产量规模的扩大。我国封测企业的快步发展有赖于开启对海内外的并购,不断扩大公司规模。如长电科技联合产业基金、芯电半导体收购新加坡封测厂星科金朋,华天科技收购美国FCI,通富微电联合大基金收购AMD苏州和槟城封测厂,晶方科技则购入英飞凌智瑞达部分资产。

半导体

半导体行业发展趋势

后摩尔定律时代

摩尔定律是由Gordon Moore在1965年提出的集成电路特征尺寸随时间按照指数规律缩小的法则,具体可归纳为:集成电路芯片上所集成的电路数目,每隔18个月就翻一番。在半导体行业发展的前50年,真实晶体管的密度发展规律基本遵循摩尔定律,人类社会飞速进入信息时代,同时在半导体工业界也诞生了一大批巨无霸企业,比如Intel和Qualcomm等等,摩尔定律成为指导半导体行业的发展蓝图。当前半导体制程已拓展至7nm,特征尺寸越来越接近宏观物理和量子物理的边界,导致高级工艺制程的研发越来越困难,研发成本也越来越高,摩尔定律逐渐到达极限。

2010年国际半导体技术发展路线图(ITRS)将晶体管密度预计修订为:到2013年低,每个集成电路上集成的晶体管数目增速将会放缓,变为每三年翻一番。此外,在摩尔定律面临来自物理极限、经济限制等多重压力的现实下,集成电路技术潮流分化为延伸摩尔(More Moore)、超越摩尔(More than Moore)和超越CMOS(Beyond CMOS)三个主要方向,系统集成、系统封装以及新材料新技术成为行业技术突破方向。

延伸摩尔:继续以等比缩小CMOS器件的工艺特征尺寸,集成各种存储器、微处理器、数字信号处理器和逻辑电路等,以信息处理数字电路为主发展系统芯片SoC技术。目前台积电、三星技术节点已达到7nm,并在继续部署5nm、3nm。当前延伸摩尔依旧是行业技术发展的主推动力。

超越摩尔:以系统级封装SiP实现数字和非数字功能、硅和非硅材料和器件、CMOS和非CMOS电路等光电、MEMS、生物芯片等集成在一个封装内,完成子系统或系统。

超越CMOS:探索新原理、新材料和器件与电路的新结构,向着纳米、亚纳米及多功能器件方向发展,发明和简化新的信息处理技术,以取代面料极限的CMOS器件。

芯片自主可控是中国半导体行业的唯一出路。对中国半导体行业的管制和封锁是中美贸易摩擦冲突主要表现。我们对比中兴和华为事件结果来看,在中兴事件中,因为没有自主可控的技术储备,中兴最终以缴纳10亿美元罚款,撤换董事会及高层管理人员和安排美方人员监督告终;而在华为事件中,由于华为有自主研发芯片、掌握5G核心技术、注重维护产业生态链而赢得与美国的搏击机会。由此我们可以看出,随着中国半导体行业的发展,面对高端技术竞争日益激烈,只有发展高端技术,实现芯片自主可控,才是中国半导体行业的唯一出路。

国产化替代成为我国半导体产业发展契机。以华为为例,2018年核心供应商共有92家,其中大陆厂商22家,台湾厂商10家,而国外厂商60家,其中33家来自美国,11家来自日本。受制于美国将华为与70家关联企业列入实体名单影响,使得华为转而注重国内市场的开发和产业生态的保护,从国内产业发展角度来看,国产化替代成为我国半导体产业发展契机。

我们通过回溯行业发展周期及产业链技术趋势,深入剖析当前半导体行业发展局势,聚焦半导体产业投资机遇。系统集成(SoC)、系统级封装(SiP)以及新材料新技术有望成为半导体产业技术突破关键。

原文标题:后摩尔时代下先进封装技术

文章出处:【微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

456文章

50945浏览量

424701 -

半导体

+关注

关注

334文章

27513浏览量

219756 -

封装

+关注

关注

127文章

7942浏览量

143095

原文标题:后摩尔时代下先进封装技术

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

解锁Chiplet潜力:封装技术是关键

先进封装成为AI时代的核心技术发展与创新

先进封装技术将成为突破半导体产业的关键

先进封装技术将成为突破半导体产业的关键

评论