今天查阅了一下晶圆良率的控制,晶圆的成本和能否量产最终还是要看良率。晶圆的良率十分关键,研发期间,我们关注芯片的性能,但是量产阶段就必须看良率,有时候为了良率也要减掉性能。

那么什么是晶圆的良率呢?

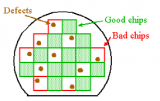

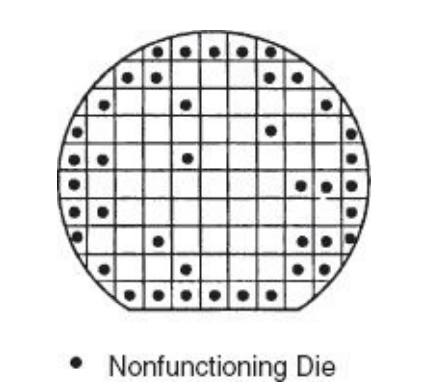

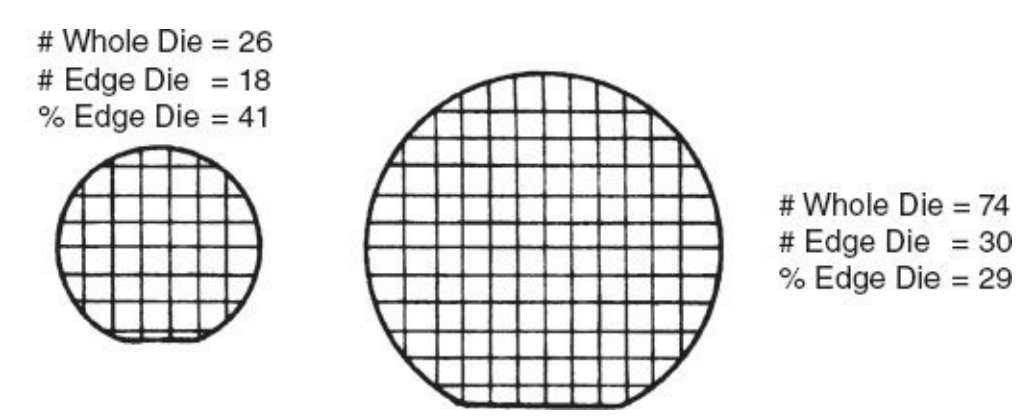

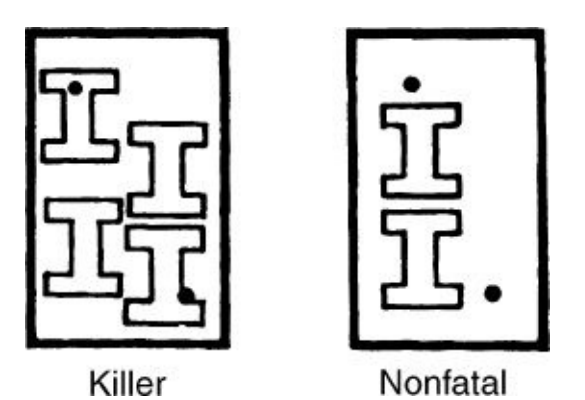

比如上图,一个晶圆,通过芯片最好测试,合格的芯片/总芯片数===就是该晶圆的良率。普通IC晶圆一般都可以完成在晶圆级的测试和分布mapping出来。

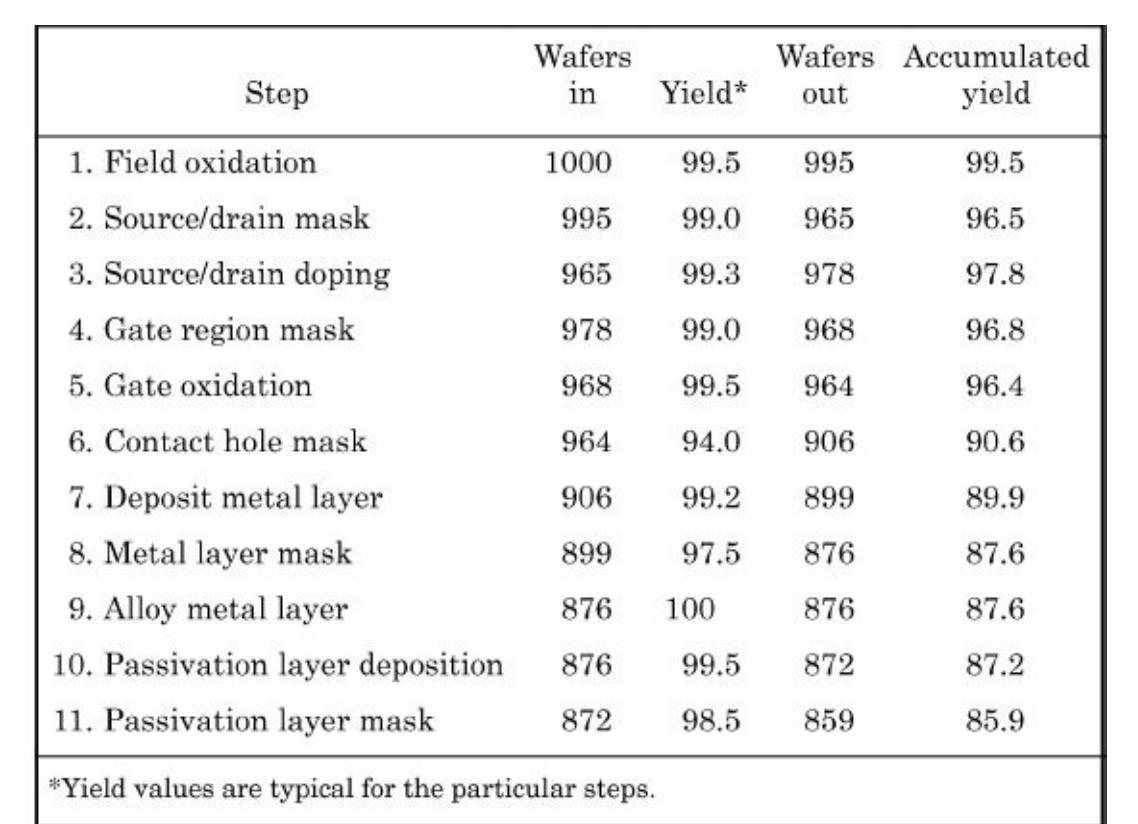

良率还需要细分为wafer良率、Die良率和封测良率,而总量率则是这三种良率的总乘积,总量率将决定一家晶圆厂到底是赔钱还是赚钱。

举个例子,如果某个晶圆厂的一条产线上每一道制程良率都高达99%,那么经过600道工序后整体良率是多少呢?答案是0.24%,几乎为0。

所以,晶圆代工企业都会视总良率为最高机密,对外公布的数据往往都不会是企业的真正总良率。

而晶圆的最终良率主要由每一步工艺的良率的积组成,从晶圆制造,中测,封装到成测,每一步都会对良率产生影响,其中晶圆制造因为工艺复杂,工艺步骤多步(300步左右)成为影响良率的主要因素。由此可见,晶圆良率越高,同一片晶圆上产出的好芯片数量就越多,如果晶圆价格是固定的,那好芯片数量就越多就意味着每片晶圆的产量越高,每颗芯片的成本越低,那么理所当然,利润也就越高。

晶圆的良率受工艺设备、原材料等影响很大,要想达到较高的晶圆良率,首先要稳定工艺设备,定期做工艺能力恢复等。另外环境因素对wafer良率、Die良率和封测良率这三种良率都会产生一定影响。常见的环境因素包括尘埃、湿度、温度和光照亮度,所以芯片制造和封测的过程中都需要在超净的工作环境中进行。最后,是技术成熟度问题。一般情况下,新工艺刚出来的时候良率会很低,随着生产的进行和导致低良率的因素被发现和改进,则良率就会不断地被提升。如今,新工艺或是工具,每个几个月或甚至几周就会被引进,因此提升良率就成了半导体公司的一个永不停息的过程。

如何把控晶圆良率

很多半导体公司都有工程师专门从事良率提高的工作,在晶圆厂(foundary)有专门的良率提高(YE)部门的良率工程师负责提高晶圆的良率,在无晶圆公司(Fabless)的运营部门有产品工程师(PE)要负责提高良率。由于领域有所不同,这些工程师所专注的重点也会有所区别。晶圆厂内的良率工程师对制造工艺十分精通,主要通过公司的良率管理系统(YMS)对工艺相关的一些数据进行良率分析,一般有以下几种方法:

1)产线中缺陷扫描数据(Inline Defect Scan)

2)工艺监控测试数据(WAT)

3)产线量测数据(Metrology)

4)设备共同性(Tool Commonality)

5)工艺规范性(Process Specifications)

6)失效分析(Failure Analysis)

无晶圆公司的产品工程师则对自己的产品非常熟悉,掌握一些设计数据和很多测试数据,所以产品工程师对良率分析会从一些几个方面开展[1]:

1)设计数据包括版图和电路图等(GDS,Schematic,etc)

2)电性测试数据(Wafer Probling,Final Test data)

3)Schmoo图

4)比特图(Bitmap)

5)系统级测试(System Level Test)

6)失效分析(Failure Analysis)

对于有实际生产线的晶圆制造,对每台制造设备的稳定性监控很重要,如上图,可以通过记录设备的关键工艺产生,积累出一个随生产时间改变的波段的曲线,形成工艺精度把控的参数点。

最后,晶圆被测试完毕之后,通过自动分拣机,可以剔除不良芯片,而且对性能良莠不齐的芯片也可以分检,比如Intel的CPU晶圆,性能较好的芯片检出来做i7处理器芯片,差点的做i5芯片,其实都是一个娘生的,只不过一个长的好看点,一个长得难看点的区别。

还有就是不同尺寸的晶圆,同一条产线做出来良率也会不同,倒不一定小片的良率一定高于大片。这也和设备工艺的匹配度有关,一个晶圆一般边缘区域的不良die最多,因此很多产线追求大尺寸晶圆,这样相对而言边缘的不良die占比就低。

但是大尺寸的晶圆就面临许多应力、膜层生长等先天性问题。比如前几年半导体热衷上10寸,12寸的产线,导致8寸、6寸产线被遗弃,连半导体设备商都不做小尺寸晶圆的设备了,20年这两年8寸二手设备这个紧俏,一朋友公司闲置1年的6寸晶圆厂现在都接单接不过来,风水轮流转啊!可能是中美贸易战像一些汽车芯片、通信芯片很多公司都在找国产的替代品。

原文标题:晶圆芯片的良率

文章出处:【微信公众号:芯片工艺技术】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

458文章

51526浏览量

429496 -

晶圆

+关注

关注

52文章

5021浏览量

128609

原文标题:晶圆芯片的良率

文章出处:【微信号:dingg6602,微信公众号:芯片工艺技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶圆切割的定义和功能

晶圆划片为什么用UV胶带

晶圆/晶粒/芯片之间的区别和联系

碳化硅晶圆和硅晶圆的区别是什么

半导体工艺之生产力和工艺良率

如何把控晶圆芯片的良率?

如何把控晶圆芯片的良率?

评论