日本关西学院大学和丰田通商于3月1日宣布,他们已开发出“动态AGE-ing”技术,这是一种表面纳米控制工艺技术,可以消除使SiC衬底上的半导体性能变差的缺陷。

尽管期望将SiC用作下一代功率半导体,但是已知在晶圆的加工阶段和晶体生长阶段会发生晶体畸变。其中,已知基底平面错位(Basal Plane Dislocation,BPD)会降低器件的性能,并且制造抑制这种现象发生的高质量晶圆的成本高昂,难以降低器件的价格。

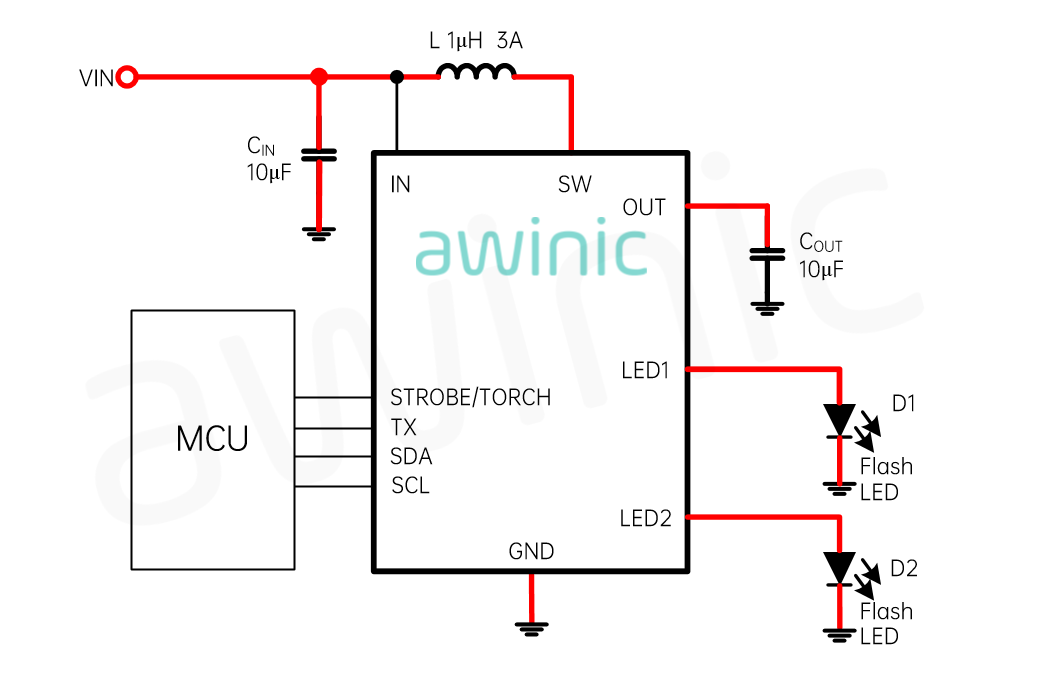

动态AGE-ing是一种通过结合热退火,晶体生长和热蚀刻技术将BPD缺陷转换为不影响器件性能的其他缺陷的技术。同一大学的科学与工程学院的Tadaaki Kaneko教授说:“尽管还有其他技术可以对高质量SiC晶圆中的缺陷进行“解毒”,但是Dynamic AGE-ing可以应用于具有许多缺陷和质量较差的晶圆。”,说明了该技术的优势。

具体而言,通过使用一个唯一的装置适当地选择并执行三个加工过程,可以自动布置晶圆表面上的原子排列,去除加工应变层,并通过刀片(TED)传送BPD。可以消除对设备的影响。

图:使用动态AGE-ing进行BPD排毒的验证示例。通过将该技术应用于市售的SiC晶圆,可以确认基板上的BPD数量为1个或更少(来源:关西学院大学的介绍材料)

在这项联合研究中,从单个零件的尺寸到150毫米(6英寸)晶圆,这是两年研究与开发中SiC的主流,无论基板的尺寸如何,在某些情况下,晶圆制造商无论,据说BPD可以免费使用。

丰田通商计划将其商业化,但目前正处于广泛招募对这项技术感兴趣的公司作为业务合作伙伴的阶段。另外,作为研究,预计在未来几年中将实际使用200 mm SiC晶圆,因此我们计划继续进行开发以将其应用于该技术。

责任编辑:YYX

-

晶圆

+关注

关注

52文章

5021浏览量

128607 -

SiC

+关注

关注

30文章

2974浏览量

63327

发布评论请先 登录

相关推荐

有效抑制SiC外延片掉落物缺陷生成的方法

碳化硅衬底的生产过程

室温下制造半导体材料的新工艺问世

碳化硅衬底的环吸方案相比其他吸附方案,对于测量碳化硅衬底 BOW/WARP 的影响

SiC单晶衬底加工技术的工艺流程

中国台湾与辽宁新增SiC衬底工厂,年产能合计达7.2万片

8英寸衬底+全SiC模块,罗姆助力SiC普及浪潮

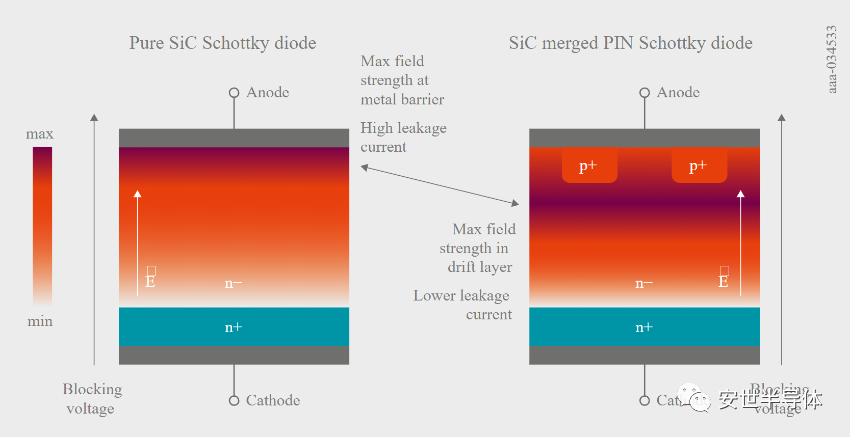

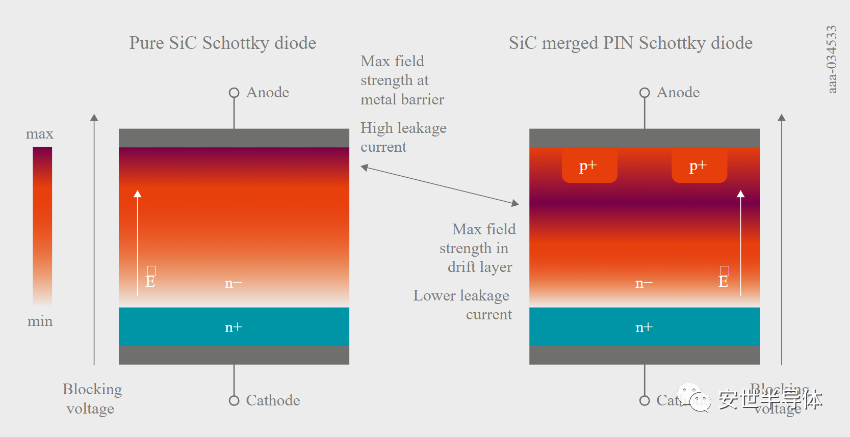

为什么SiC肖特基二极管不一样

国内外突破:三种新工艺方案引领8英寸SiC生产降本增效

新质生产力赋能高质量发展,青禾晶元突破8英寸SiC键合衬底制备!

为什么所有的SiC肖特基二极管都不一样

8英寸SiC衬底阵容加速发展 全球8英寸SiC晶圆厂将达11座

创新工艺可以消除SiC衬底中的缺陷

创新工艺可以消除SiC衬底中的缺陷

评论