逻辑芯片产业正朝着晶体管结构的根本性变革迈进。今天的晶体管,称为FinFET,将会让位于被称为纳米片晶体管、多桥沟道FET和栅极全能晶体管的器件。除了制造性能更好、体积更小的晶体管的动力之外,纳米片还为电路设计增加了FinFET所缺乏的自由度。本月早些时候,在IEEE国际固态电路会议上,三星的工程师们展示了这种额外的灵活性是如何使片上存储单元的写入电压降低数百毫伏,从而有可能在未来的芯片上节省电力。

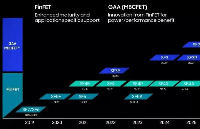

尽管中国台湾半导体制造公司(TSMC)计划在下一代工艺(3纳米节点)中继续使用FinFET,但三星还是选择了推出其版本的纳米片,即多桥沟道MOSFET(MBCFET)。在场效应晶体管(FinFET)中,沟道区(晶体管中电流流过的部分)是一个从周围硅中凸出的垂直fin。闸门覆盖在fin上,覆盖在fin的三个侧面,以控制流经通道的电流。纳米片用一堆水平的硅片代替了fin。

三星电子副总裁Taejoong Song在虚拟会议上告诉与会者:“我们已经使用FinFET晶体管大约10年了,但是在3纳米晶体管的周围我们使用的是栅极晶体管。”新的晶体管“提供高速、低功率和小面积”。

但是,正如早期的纳米片开发者在IEEE Spectrum上解释的那样,新的器件结构增加了finfet所缺乏的设计灵活性。这里的关键是晶体管通道的“有效宽度”,即Weff。一般来说,在给定的电压下,更宽的通道可以驱动更多的电流通过,从而有效地降低其电阻。因为你不能改变FinFET中fin的高度,用今天的晶体管提高Weff的唯一方法就是在每个晶体管上增加更多的fin。所以用FinFET,你可以使Weff增加两倍或三倍,但不能增加25%或减少20%。然而,你可以改变纳米薄片器件的宽度,这样使用它们的电路就可以由具有各种特性的晶体管组成。

“最近,设计师们在(实现最高设备频率)和低功耗方面面临许多挑战,”Song说。“由于这种设计灵活性,SRAM…可以得到更大的改进。”

宋和他的团队利用这种灵活性来提高下一代SRAM的性能。SRAM是一种六晶体管的存储单元,主要用作处理器上的高速缓存,它也是逻辑芯片中最密集的部件之一。三星测试了两种方案来改善SRAM的写裕度,即切换电池状态所需的最小电压。该值一直处于压力下,因为芯片互连已缩小,其电阻已因此增加。

SRAM的六个晶体管可分为三对:通栅、上拉和下拉。在FinFET设计中,这三种类型的Weff是相等的。但是对于纳米片设备,三星团队可以自由地进行修改。在其中一处,他们把隘口和斜坡加宽了。在另一个洞里,他们把隘口变宽了,拉下去的通道变窄了。

目的是降低写入SRAM单元所需的电压,而不使单元变得如此不稳定以至于读取时可能会意外地翻转一点。他们提出的两种方案利用了这些宽度调整——特别是拓宽通栅晶体管相对于上拉晶体管的宽度——来达到一个SRAM单元,其写入电压比正常情况下低230毫伏。

三星预计将在2022年使用3纳米制程的MBCFET。

责任编辑:tzh

-

芯片

+关注

关注

454文章

50480浏览量

422202 -

MOSFET

+关注

关注

146文章

7108浏览量

212816 -

晶体管

+关注

关注

77文章

9641浏览量

137908 -

FinFET

+关注

关注

12文章

247浏览量

90159

发布评论请先 登录

相关推荐

三星电子:18FDS将成为物联网和MCU领域的重要工艺

传2022年三星3纳米工艺将使用MBCFET技术

传2022年三星3纳米工艺将使用MBCFET技术

评论