2014 年,斯坦福大学教授 Mark Horowitz 发表了一篇题目为“计算的能源问题(以及我们该怎么办)”的论文。这篇具有深远意义的论文,讨论了当前半导体行业所面临的最热门的、与登纳德缩放比例定律 (Dennard Scaling )和摩尔定律 (Moore’s Law) 失效相关的挑战。

如果可以的话,我想借用并改编一下 Mark 的论文标题,这样我就可以就机器学习推断应用为什么应该考虑专用硬件,分享一下我的一些观点。

专用硬件加速实在必行

首先,让我们考虑一下问题的症结所在。大约在2005 年,处理器内核时钟频率的增长进入了瓶颈。缩小工艺尺寸和降低内核电压不再像以前一样能够为我们带来优势。其根本的问题,就是计算已经达到了功率密度(W/mm2)的极限。

如果我们在同一个裸片上放置更多的内核,我们就可以在相同的功耗预算下增加运算数量,但其前提是我们还还要在一定程度上降低时钟频率,以抵消额外内核所消耗的能量。AMD 和英特尔都是在 2005-2006 年期间发布了他们的首个双核处理器,这并不是巧合。然而,随着我们继续尝试增加内核的数量,我们必须考虑每个运算所消耗的能量和每个运算所需的芯片面积。此外,我们还需要确保我们能够通过 N 来有效地实现并行算法,其中 N 是内核的数量。对于所有的算法来说,这一问题的通用解决方案,或者说“计算饱和的灵丹妙药”仍然是一个难以捉摸的问题,现在最好的解决方法就是应用“自适应硬件”。

事实证明,无论您的处理器设计是使用多核 CPU、GPU 还是 SoC 实现的,在处理器级的总体功耗分布都将大致相同。

所以假若我们估算出以下的情况便较为接近真实情况:

内核 = 30%

内部存储器(L1、L2、L3)= 30%

外部存储器(DDR)= 40%

在上面的分析中,我们没有考虑的是还存在另外一个总体优化的方式,那就是专用硬件加速器优化的实现方式。我们可以对专用硬件进行优化以极高效地执行特定的功能。通常情况下,这种硬件是为了减少外部存储器访问而设计的,其同时减少了时延与功耗。我们可以对专用硬件进行优化,以便给定算法的数据运动部分使用本地化存储器 (BlockRAM、UltraRAM) 来进行中间结果的存储。

设计高效的加速器是多维度的设计问题:

我们如何实现硬件优化来处理我们的特定算法?(Mark 很好地回答了这一问题,即必须将算法从“所有算法的空间”移动到“受限空间”。)

我们如何保持携带数据的加速器,以确保我们的计算加速器在每个时钟周期都是饱和的?

我们如何最大限度地减少通信开销?

我们如何优化正在处理的运算符的动态范围?

我们如何最大限度地减少外部存储器,甚至是本地存储器的使用?

我们如何消除指令处理管道开销?

我们如何安排操作以确保数据重用,从而使存储器流量最小化,并且使存储器访问相关的运算数量最大化?

自适应硬件的战略优势这里,我们将讨论和评估赛灵思的自适应硬件及 DNNDK 如何应对上述这些尖锐的问题和挑战,特别是当它涉及到机器学习推断时。在进行下一次设计之前,我建议您回顾一下 Mark 有关这个主题的精彩演讲,然后再考虑如何在您的下一次设计中使用自适应硬件来实现您的战略优势。

在这篇文章的第 2 部分中,我们将讨论和评估赛灵思的自适应硬件及 DNNDK (现在已经发布Vitis AI 统一软件平台) 如何应对这些挑战,特别是当它涉及到机器学习推断时。

原文标题:人工智能引发能源问题,我们该怎么办?(一)

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

AI

+关注

关注

87文章

30315浏览量

268570 -

人工智能

+关注

关注

1791文章

46927浏览量

237783

原文标题:人工智能引发能源问题,我们该怎么办?(一)

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是机器学习?通过机器学习方法能解决哪些问题?

NPU与机器学习算法的关系

钳位能力与电流和负载具体是什么关系,应该怎么考虑?

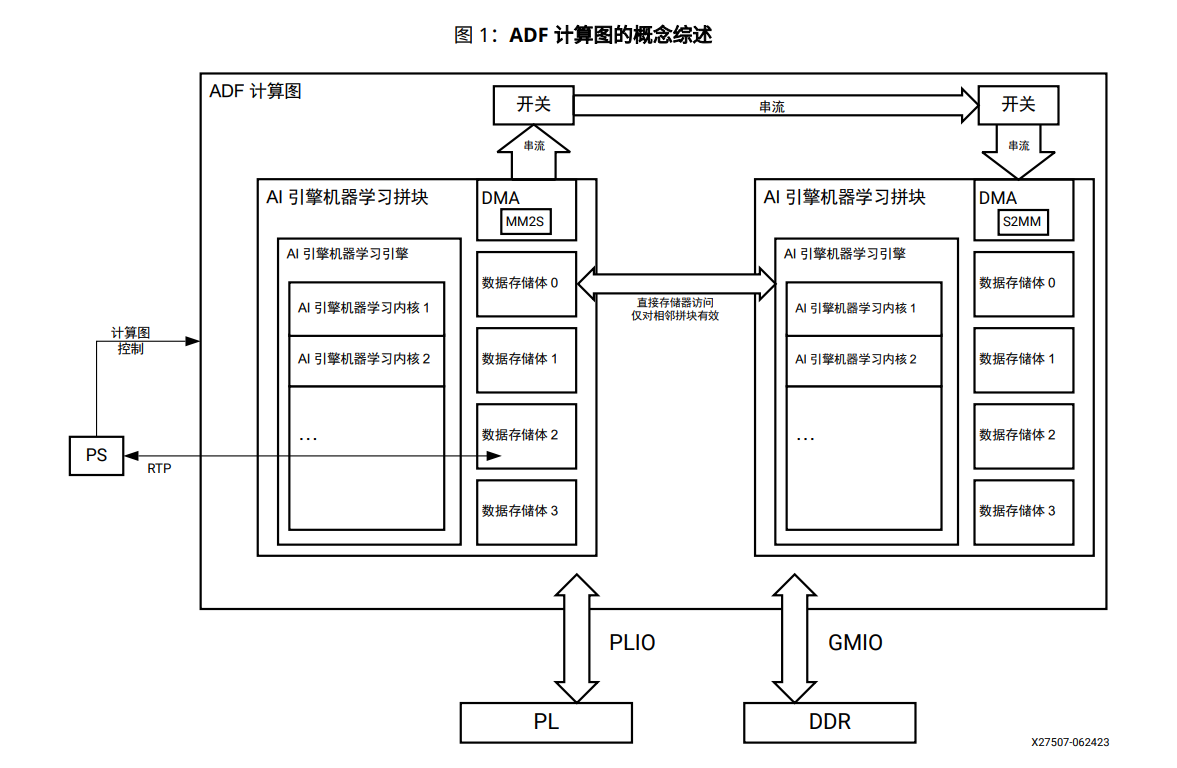

AI引擎机器学习阵列指南

【《时间序列与机器学习》阅读体验】+ 了解时间序列

神经网络专用硬件实现的方法和技术

机器学习算法原理详解

深度学习与传统机器学习的对比

选择美国vps云主机时应该考虑哪些因素

人工智能和机器学习的顶级开发板有哪些?

电缆选型时应该考虑什么

机器学习推断应用为什么应该考虑专用硬件?

机器学习推断应用为什么应该考虑专用硬件?

评论