一:fifo是什么

FIFO的完整英文拼写为FirstIn First Out,即先进先出。FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个存储器,常被用于数据的缓存或者高速异步数据的交互。

二:FIFO有几种结构

FIFO从大的情况来分,有两类结构:单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO),其中双时钟FIFO又可以分为普通双时钟(DCFIFO)和混合宽度双时钟FIFO (DCFIFO_MIXED_WIDTHS)。三种FIFO结构的英文含义如下所示:

•SCFIFO: 单时钟FIFO

•DCFIFO:双时钟 FIFO

•DCFIFO_MIXED_WIDTHS: 混合宽度双时钟

在没有特别指明的情况下,混合宽度双时钟FIFO和双时钟FIFO统称为双时钟FIFO。

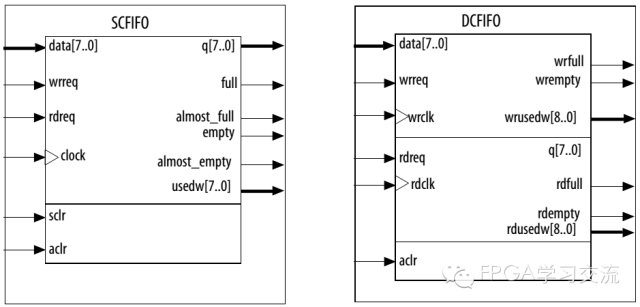

下图为分别为单时钟FIFO和双时钟FIFO的符号图:

从图中我们可以看到,单时钟FIFO具有一个独立的时钟端口clock,当Clock上升沿到达时,且wrreq有效时,将data[7..0]中的数据写入FIFO;当Clock上升沿到达时,且rdreq有效时,将q[7..0]中的数据输出FIFO;full是满标志位,当FIFO写满时有效,almost_full是将满标志,当快写满时有效,almost_full数值可以配置;同理empty与almost_empty是空标志和将要空标志,自己也可以配置almost_empty。usedw[7..0]是当前FIFO可以使用的数据。sclr是同步清零,当有效时且Clocks上升沿到达时清楚FIFO的数据;aclr是异步清零,当有效时清除FIFO的数据。

双时钟FIFO和单时钟FIFO基本一样,就是读写分别采用不同的时钟信号。wrfull为写满标志,wrempty为写空标志,当我们想在只有FIFO空的时候才能写入时就用wrempty来判断,wrusedw[8..0]写入多少数据,rdusedw[8..0]能读出多少数据。这里将写入的数据和刻度的数据分开计数的原因是,当我们写入数据长度和读数据长度不同时,比如写的数据长度是16位,读的数据长度是8位,当写入一个数据wrusedw[8..0]=1,而rdusedw[8..0]=2。rdfull是读满标志,当我们要想要只有写满时才可读可根据这个标志判断(读数据包)。rdempty读空标志,当FIFO没有可读数据时有效。aclr异步请零。双时钟FIFO只有异步清零。

三:不同结构的FIFO各有什么作用

单时钟FIFO:

单时钟FIFO常用于片内数据交互,例如,在FPGA的控制下从外部传感器读取到的一连串传感器数据,首先被写入FIFO中,然后再以UART串口的数据发送速率将数据依次发送出去。由于传感器的单次读取数据可能很快,但并不是时刻都需要采集数据,例如某传感器使用SPI接口的协议,FPGA以2M的SPI数据速率从该传感器中读取20个数据,然后以9600的波特率通过串口发送出去。此过程每秒钟执行一次。因为2M的数据速率远高于串口9600的波特率,因此需要将从传感器中采集到的数据首先用FIFO缓存起来,然后再以串口的数据速率缓慢发送出去。这里,由于传感器数据的读取和串口数据的发送都是可以同步于同一个时钟的,因此可以使用单时钟结构的FIFO来实现此功能。

双时钟FIFO:

双时钟FIFO的一个典型应用就是异步数据的收发。

所谓异步数据是指数据的发送端和接收端分别同步与不同的时钟域,使用双时钟FIFO的独立的读写时钟结构,能够将不同时钟域中的数据同步到所需的时钟域系统中。例如,在一个视频图像采集系统中,实现将摄像头采集的数据通过VGA在显示器上显示。摄像头输入的数据长度和速度与输出到VGA显示的数据长度和速度都不相同,这种情况下使用双时钟FIFO。

四:如何在Altera FPGA中使用FIFO实现功能设计

在Altera FPGA中使用FIFO实现用户功能设计主要有三种实现方式,第一种为用户根据需求自己编写FIFO逻辑,当用户对于FIFO的功能有特殊需求时,可以使用此种方式实现,但此种方式要求用户有较高的RTL设计能力。第二种方式为使用第三方提供的开源IP核,此种IP核以源码的形式提供,能够快速的应用到用户系统中,当用户对FIFO功能有特殊需求时,可以在此源码的基础上进行修改,以适应自己的系统需求。第三种方式为使用Quartus II软件提供的免费FIFO IP核,此种方式下,Quartus II软件为用户提供了友好的图形化界面方便用户对FIFO的各种参数和结构进行配置,生成的FIFO IP核针对Altera不同系列的器件,还可以实现结构上的优化。

原文标题:一起来了解一下FIFO!

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1628文章

21722浏览量

602875 -

fifo

+关注

关注

3文章

387浏览量

43635

原文标题:一起来了解一下FIFO!

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FIFO Generator的Xilinx官方手册

如何在FPGA中实现状态机

请问cmakelists中的变量如何在程序中使用?

芯海应用笔记:CSU3AF10 IAP功能设计指南_V1.0

如何在labview FPGA端实现二维插值的功能?

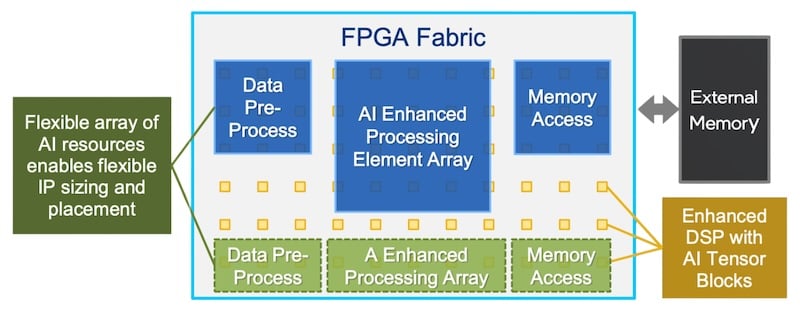

Altera将AI注入新的中端FPGA

英特尔旗下FPGA公司Altera正式亮相

英特尔成立全新独立运营的FPGA公司Altera

英特尔宣布成立全新独立运营的FPGA公司——Altera

如何在Altera FPGA中使用FIFO实现功能设计?

如何在Altera FPGA中使用FIFO实现功能设计?

评论