引言

功率转换开关频率一直在不断提高,以便最大限度地提升功率密度,软开关技术如零电压开关(zero voltage switching,ZVS)成为通用的技术以进一步提高开关频率。随着开关频率的增大 ,功率MOSFET的寄生特性不再可忽略不计。对于采用ZVS拓扑的功率转换器设计,输出电容是所有寄生成分中至关重要的寄生参数。它决定了需要多少电感 量来提供ZVS的工作条件。传统上,许多设计人员使用粗略的假设来为公式[1-2]提供输出电容的固定值。然而常用的等效输出电容值在实际应用中却没有很 大的帮助,因为它是根据漏-源电压变化的,并且在开关管导通/关断转变期间不能提供准确的储能信息。在功率转换器工作电压下,根据输出电容存储能量新定义 的等效输出电容,能够实现更优化的功率转换器设计。

ZVS转换器中的输出电容

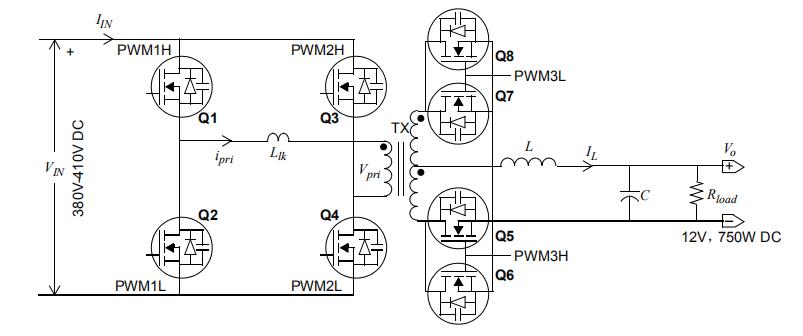

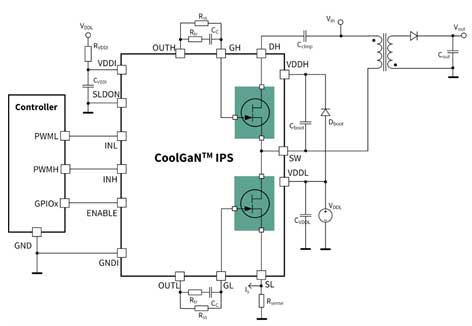

在软开关拓扑中,通过使用电感中的储能来达到零电压导通,漏电感和串联电感或变压器中的磁化电感,通过谐振方式使开关管中的输出电容放电。因此,电感必须精确设计,以防止硬开关引起额外的功率损耗。下面的公式是零电压开关的基本要求。

![]() (1)

(1)

其中,Ceq是开关等效输出电容,CTR是变压器寄生电容

(2)

其中,CS是开关等效输出电容

公式(1)用于移相全桥拓扑[2],公式(2)用于LLC谐振半桥拓扑[3]。在两个公式中输出电容都起着重要作用。如果在公式(1)中假设输出电容过 大,公式会给出较大的电感。然后,此大电感将降低初级di/dt,并且减低功率转换器的有效占空比。相反,太小的输出电容将导致较小的电感和有害的硬开 关。另外,公式(2)中太大的输出电容将限制磁化电感并引起循环电流的增加。因此,对于优化软开关转换器设计,获取准确的开关输出电容值是非常关键的。通 常,针对等效输出电容的常见假设倾向于使用较大的数值。所以,根据公式(1)或(2)选择电感后,设计人员必须调整其功率转换器参数,并且要经过数次反复 设计,因为每个参数都是相互关联的,例如,匝数比、漏电感、以及有效占空比。而且,功率MOSFET的输出电容是根据漏-源电压变化的。在功率转换器工作 电压下,根据储能来等效出的输出电容值是这些应用的最佳替代选择。

从输出电容中获得储能

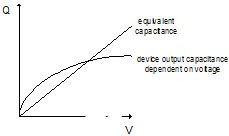

在电压-电荷关系图上,电容呈斜直线,电容中的储能为该直线下包含的区域。虽然功率MOSFET的输出电容却是非线性的,并且依据漏源电压的变化而变化, 但是,输出电容中的储能仍为非线性电容线下所包含的区域。因此,如果我们能够找出一条直线,由该直线给出的区域与图1中显示的变化的输出电容曲线所包含的 区域相同,则直线的斜率恰好是产生相同的储能的等效输出电容。

图1. 等效输出电容的概念

对于某些老式平面技术MOSFET,设计人员可能会用曲线拟合来找出等效输出电容,其基于通常指定的25V漏源电压下的数据表中的输出电容值。

![]() (3)

(3)

于是,储能可由简单积分公式获得。

![]() (4)

(4)

最后,有效输出电容即为

(5)

图2显示了输出电容的测量值以及由公式(3)得出的拟合曲线。相对于图2(a)的老式技术MOSFET,它的效果不错。然而,对于使用新技术如超级结技 术,输出电容有更多非线性特性的MOSFET,则简单的指数曲线拟合有时不够好。图2(b)显示了最新技术MOSFET的输出电容测量值以及用公式(3) 得出的拟合曲线。对于等效输出电容值,两者之间在高电压区的间隙会导致巨大的差异,因为在积分公式中电压对于电容是相乘的。图2(b)中的估计将产生大得 多的等效电容,这会误导转换器的初始设计。

图2. 输出电容估值,(a)老式MOSFET,(b)新MOSFET

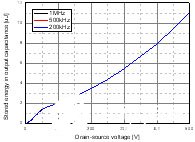

如果输出电容值依据漏源电压而变化,输出电容中的储能可以使用公式(4)来求得。虽然电容曲线显示在数据表中,但从图表中精确地读出电容值并不容易。因 此,依据漏源电压,输出电容中的储能由最新功率MOSFET数据表中的图表给出。通过图3显示的曲线,使用公式(5),可以得到在期望的直流(DC)总线 电压下的等效输出电容。

图3. 输出电容中的储能

关于输出电容的常见问题

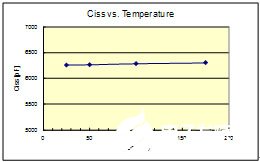

在许多情况下,开关电源设计人员会有关于MOSFET电容温度系数的疑问,因为功率MOSFET通常工作在高温下。总之,MOSFET电容值对于温度可以 被认为是恒定的。MOSFET电容由耗竭长度(depletion length)、掺杂浓度、沟道宽度和硅介电常数所决定,但所有这些因素不会由温度而产生较大的变化。而且MOSFET开关特性如开关损耗或开/关转换速 度也不会因温度而产生较大的变化,因为MOSFET是多数载流子器件,因而开关特性主要是由其电容来决定。当温度上升时,等效串联栅极电阻会有少量增加。 这会使MOSFET在高温下的开关速度少许降低。图4显示了依据温度变化的电容。温度变化超过150度时,电容值的变化也不超过1%。

图4. MOSFET电容对比温度的变化

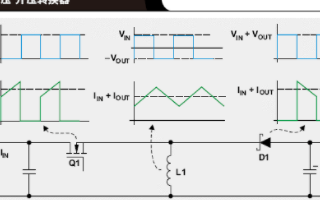

另一个设计人员感兴趣的地方是MOSFET电容的测试条件。大多数情况下,输出电容在1MHz频率和Vgs为0V的条件下测得。事实上存在着栅极对漏极电容、栅极对源极电容,以及漏极对源极电容。实践中,单独测量每一种电容是不可能的。因此,栅极对漏极电容和漏极对源极电容总称为输出电容,通过并联两个电容来测量。为使它们并联,栅极和源极短接在一起,即Vgs=0V。 在开关应用中,当MOSFET在栅极加偏置电压而导通时,输出电容通过MOSFET内部沟道而短路。仅当MOSFET关断时,输出电容值才值得考虑。关于 频率,如图5所示,在低压下输出电容在低频下增加少许。低频时,因为测试设备的限制,有时无法测量低漏源电压下的电容。图5中,当漏源电压小于4V 时,100kHz处的电容是无法测得的。虽然输出电容仅有微小改变,但等效输出电容几乎是恒定的,因为低电压下输出电容的微小改变不会对储能产生如图3显 示那么大影响。

图5. MOSFET电容对比频率

结论

输出电容是软开关转换器设计的重要部分。必须慎重考虑等效电容值,而不是固定漏源电压下的单一数值,本文也提供了有关输出电容测试条件和温度系数的讨论。

责任编辑:gt

-

开关

+关注

关注

19文章

3137浏览量

93628 -

转换器

+关注

关注

27文章

8703浏览量

147166 -

功率

+关注

关注

14文章

2068浏览量

69879

发布评论请先 登录

相关推荐

非反向降压-升压转换器的拓扑结构和如何实现应用设计

MOSFET器件用于相移ZVS转换器中可能存在的隐患分析

产品推荐:Cool-Power® ZVS 稳压器 功能强大,突破界限

多芯片集成在隔离型DC-DC转换器的实现

eGaN场效应晶体管在高频谐振总线转换器和48 V降压转换器中的应用介绍

STEVAL-ISA118V1,演示板采用Viper16离线功率转换器,采用反激式拓扑结构,抖动固定频率

借助高能效GaN转换器,提高充电器和适配器设计的功率密度

借助高能效GaN转换器,提高充电器和适配器设计的功率密度

如何使用SiC功率模块改进DC/DC转换器设计?

采用数字斜率补偿的峰值电流控制ZVS全桥转换器

采用ZVS拓扑实现更优化的功率转换器设计

采用ZVS拓扑实现更优化的功率转换器设计

评论