何为信号完整性?

信号完整性(SignalIntegrity)就是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传输到接收端,我们就称该信号是完整的。

从广义上讲,信号完整性指的是在高速电路设计中由互连线所引起的所有信号问题,包括噪声、串扰、反射、地弹、时序和阻抗等。

信号具备信号完整性,是指接收端能够收到符合逻辑电平要求、时序要求和相位要求的信号。在系统互连的设计中,需要研究互连线、传输的信号、过孔、连接器以及器件之间的互相影响。

对信号完整性的研究,可以归纳为以下四类:

单一网络的信号完整性问题;

两个或者多个网络间的串扰;

电源和地分配网络中的轨道塌陷;

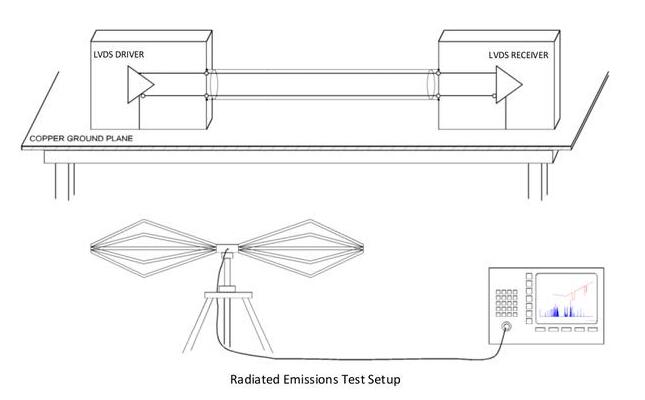

来自整个系统的电磁干扰和辐射。

2、信号完整性产生原因

从信号完整性的根源上考虑,可以将产生信号完整性的原因分为以下几个:

1)信号上升时间变短。信号的上升时间变短,从频域的角度看,信号的带宽变宽,信号所对应的最高截止频率就变高,过高的信号频率在信号传输过程中主要变现为振铃、反射、串扰、地弹和电磁辐射等。从能量守恒的角度来看,高频部分的能量过多的消耗在信号传输路径上,从而导致接收端接收到的能量达不到阈值,不能达到datasheet要求的正确逻辑电平,从而就会导致逻辑电平的传输错误。

2)芯片的工作电压变低,噪声容限变小。随着半导体和封装技术的迅速发展,芯片的速度和低功耗要求更高,使得芯片的供电电压正在变得越来越低,从而导致其噪声容限变得越来越小,噪声容限变小,使得信号在遇到信号完整性的问题时,更容易出现电平值的错误翻转。

3)PCB器件布局及布线密度越来越高,寄生效应增强,串扰加大。随着现在集成电路的集成度越来越高,功能越来越复杂,相应地要求集成电路封装密度也越来越大,引线数越来越多,而体积越来越小,就导致PCB布局和布线的密度就不断加大。因为互连和器件的封装所带来的容性和感性的寄生效应越来越严重,加大了信号彼此之间的干扰,不仅同平面的信号和器件之间相互影响,相邻层面的信号之间的影响也越来越严重。

4)电源和地噪声所带来的信号高低电平阈值范围的缩小。在高频PCB板中,较重要的一类干扰便是电源噪声,电源和地平面的噪声来源主要有VRM、CoreIO跳变带来的噪声、平面谐振噪声、临近电源耦合的噪声和其他耦合的噪声等。所以应该尽可能减小电源的阻抗,最好有专门的电源层和接地层,这样回路总可以沿着阻抗最小的路径走,这样可以最小化信号回路,从而减小噪声。

信号的传输需要一个参考平面,当参考平面上有波动的噪声时,走线所参考的电动势也相应会发生变化,即信号所呈现的电平值是一个波动的范围。因为参考平面上噪声的存在,所以高低电平的阈值范围就会减小,甚至发生错误的翻转。又因为电源噪声的影响,使信号的噪声容限和时序容限变小,并带来一定的EMI干扰。

3、结语:

对信号完整性问题的研究,总的来说就是需要保证信号传输波形的完整和信号时序的完整。更进一步,如果对阻抗有更深入的理解,把器件之间互连线的物理设计和互连线的阻抗联系起来,就可以在PCB设计的过程中,从根本上对信号完整性问题进行量化分析,就能够消除很多潜在的信号完整性问题。

对于四类信号完整性问题,为了保证信号传输的质量,工程师在设计PCB走线时需要注意以下几点要求:

PCB走线时使信号在整个互连线平面的阻抗相同,PCB走线中要尽量避免直角和锐角走线,防止由于阻抗不连续造成信号的反射,产生EMI;

为减少网络之间的串扰,应尽量加大走线之间的距离(差分线除外),并使走线与其非理想的返回路径之间的互感最小,可以有效的抑制串扰;

设计层叠时,在满足阻抗要求的条件下,应尽量使信号层靠近参考面,使得传输线可以紧密的与参考面进行耦合,从而减少相邻信号线间的串扰;

在布线空间允许的条件下,在串扰比较严重的两条信号线之间插入一条地线,可以减少两条信号线间的耦合,从而减小串扰;

为了减少轨道塌陷的幅度,需要使电源/地路径的阻抗尽量减小,必要时电源与地平面之间可添加符合谐振特性的去耦电容,减小EMI噪声;

为减小电磁干扰,应尽量减小传输信号的带宽,并尽量使地阻抗达到最小。

在进行PCB设计时考虑到PCB设计的实际操作,在操作中需要考虑的因素主要有PCB的叠层架构、阻抗、器件互连的拓扑结构、延迟、串扰、反射、地弹、时序、电源完整性和电磁干扰分析(EMC和EMI)等。

责任编辑人:CC

-

信号完整性

+关注

关注

68文章

1411浏览量

95529

发布评论请先 登录

相关推荐

信号完整性为什么写电源完整性?

听懂什么是信号完整性

信号完整性产生的原因是什么

信号完整性产生的原因是什么

评论