作者:陈道杰,Michael,Frisch,Erno,Temesi

寄生电感一直以来都是电力电子器件应用中需要克服的主要难题,尤其是对于高频和大功率应用场合。模块内部的寄生电感会造成关断过程中的过电压,寄生参数会造成模块开关过程中的波形震荡,从而增加了电磁干扰和关断损耗。功率模块厂家做了很多研究试验去努力降低它,现在比较流行的方法是把叠层直流母线引入到模块内部,但相对来说机械结构比较复杂,而且成本较高,体积也较大。本文阐述了一种新的基于现有标准模块封装,通过为瞬时电流提供一条额外的超低寄生电感回路,真正实现了功率模块的低寄生电感设计,为大功率高频应用的实现提供了可能性。

1. 模块内部寄生电感的影响

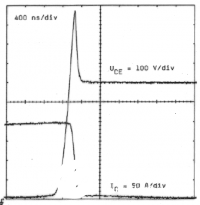

在关断IGBT过程中,IGBT电流急剧变化,由于有寄生电感的存在,会在IGBT上产生电压尖峰 Vce(peak) = Vce + L * di/dt,如图1所示。

图1: 关断尖峰电压

电压尖峰增加了IGBT过电压的风险,在某些应用场合,尤其是对于大功率应用,高开关速度情况下,需要使用更大电压等级的IGBT,这无疑会增加器件的静态损耗和器件成本;另外电压尖峰及其导致的波形震荡还会带来额外的关断损耗,这都会导致系统效率的下降和成本的增加。

在

一个可接受的效率状况下,可以说寄生电感的存在限制了开关频率的进一步提高,限制了高频化的应用;另外关断过程中的电压尖峰不仅和寄生电感大小成正比,它

还和开关电流的变化率成正比。这就意味着对于大功率模块,由于开关电流比较大,它就需要更加低电感的设计。例如对于100A/700V(1200V

IGBT)的应用,回路中寄生电感10nH是可以接受的,那么对于较大功率的应用,例如500A/700V (1200V

IGBT),为了取得同样的开关效果,回路中的寄生电感必须降到2nH。但是现实情况正好相反,对于大功率模块,为了降低回路中的等效电阻,需要使用更大

面积的直流母排和螺栓端子,而这又进一步增加了回路中的寄生电感。因此,对于大功率模块的应用,现在更多的设计是通过降低模块的关断速度(如使用更大的驱

动电阻或者使用较慢开关速度的芯片)从而降低di/dt,来达到控制关断电压尖峰的目的。但这无疑增加了模块的开关损耗,这也是为什么现在大功率电力电子

装置中,开关频率普遍提高不上去的原因。

2. 新型大功率模块低寄生电感设计方法

如前文所述,大功率模块回路需要流过大电流,为了保持回路中的低等效电阻,必须使用面积较宽的走线,而这就会增加回路中的寄生电感,这个矛盾是客观存在的。为了解决这个矛盾,必须设法把两个回路解耦。对应的策略就是在保持大电流低电阻回路的基础上,额外为IGBT开关过程增加一个低寄生电感回路,如图2所示。实线回路为稳态大电流回路,由于走线很宽,等效电阻很小,但是由于环路面积很大,等效寄生电感较大。而虚线回路为瞬态大电流回路,只有在开关过程中,也就是di/dt比较大的时候,电流才会从这个回路走,时间一般只有几百纳秒,线路不会有很大的热量,所以这个回路可以设计得非常小,从而实现低等效寄生电感。

图2: 功率模块双回路设计理念

2.1 设计目标

现在的设计目标就是在现有标准功率模块的基础上,在保持低电阻回路前提下,设计出额外的低寄生电感回路。方向有两个:

? 利用叠层走线降低寄生电感,例如PCB双层走线,使用薄膜电容等;

? 多个电感回路并联使用,从而降低寄生电感。最佳的布线就是直流母线正负端子交替排列并互相靠近。

2.2 设计思路

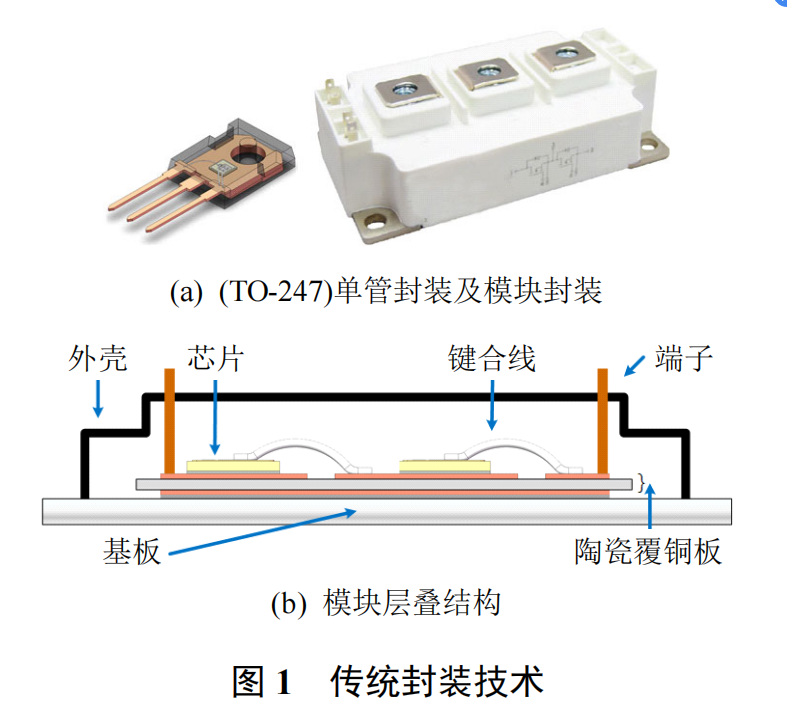

如下图3和4,flowSCREW为大功率标准模块。

图3:基于标准模块flowSCREW的低寄生电感回路

图4: 模块内部的PCB桥

图中绿色的PCB桥就是为瞬时电流提供的低寄生电感回路。它位于两个DCB之间。PCB上的直流母线是叠层设计的,也就是说每层直流母线正端都会在PCB隔层设计为直流母线负端。模块内部的PCB桥通过PCB引脚和模块外部的主PCB连接。不过为了保持间隙距离和爬电距离,DC+和DC-引脚需要保持足够的距离。如果不采取措施,这两个引脚之间也会产生等效寄生电感。由于模块外部引脚电流是从不同的引脚间流过,所以没办法通过工作电流来补偿寄生电感。但是在PCB引脚内部,通过布置相反极性的电压,例如在直流母线正端引脚内部布置了直流母线负端走线,这也能显著抑制了寄生电感的产生。低寄生电感回路通过外部的主PCB和1.2uF的薄膜电容相连。

3. 测试与验证

图5为低寄生电感模块样品。

图5: 测试样品 (三个半桥模块通过低寄生电感回路连接到滤波电容上)

接下来会对其进行寄生电感和关断电压尖峰测试来验证设计的效果。测试包括三个步骤:

? 标准模块寄生电感测试

? 具有低寄生电感回路,但主PCB上没有滤波电容的测试

? 具有低寄生电感回路,有薄膜电容电路测试

3.1 标准模块寄生电感测试

首先对600V 400A的标准模块flowSCREW2进行了测试,如图6。其中横坐标为时间,众坐标为以百分比标示的各个电气参数。蓝色线为集电极发射极之间的电压,100%对应350V;粉红色线对应集电极电流,100%对应700A;黄色线对应门极驱动电压,100%对应15V。

图6: 标准模块关断波形测试(没有低寄生电感回路)

从图中可以看到,在尖峰电流为700A (25C)时,关断电压尖峰达到了370V。即使直流母线电压降到300V,670V的电压尖峰也已经超过IGBT允许的最大电压。通过计算,可以得到标准模块直流回路的寄生电感大约为22nH。

3.2具有低寄生电感回路,但主PCB上没有滤波电容的测试

同样是600V 400A的模块,但是配置了低寄生电感回路,如图7。

图7: 模块关断波形测试(有低寄生电感回路,但没有滤波电容)

模块工作条件为直流母线电压为350V,开关尖峰电流为720A(25C)。从图中可以看到电压尖峰为250V,通过计算可以得到模块的寄生电感大约为16nH,下降了大约27%,说明低寄生电感回路的确起作用了。

3.3具有低寄生电感回路,有滤波电容电路测试

测试条件同上,从图8所示,可以看到此时电压尖峰进一步下降到190V,通过计算,等效寄生电感为7nH。相对于标准模块下降了68%。这就使得功率器件开关速度可以提高68%,这将会大大降低半导体器件的开关损耗,提高系统效率。这也为大功率模块高频化的实现提供了途径。

图8: 模块关断波形测试(有低寄生电感回路,有滤波电容)

4. 下一步的研究重点

下一步的研究方向主要是通过低寄生电感回路的并联,来进一步降低模块内部的寄生电感。通过这种方法,每个IGBT芯片将共用低寄生电感回路。也就是说对每个芯片而言,回路寄生参数是类似的。芯片之间的动态均流效果将会非常好,这也从一定程度上降低了芯片并联需要降额的要求。图9为根据这个理念做的模块,新模块设计目标是相对于flowSCREW封装,在电流等级提高一倍的基础上,把寄生电感进一步下降到5nH以下。

图9 新型大功率模块封装图

5. 低寄生电感模块的应用

低寄生电感大功率模块的实现为高频高效大功率应用以及新的拓扑结构提供了可能:

a. 高频大功率应用

低寄生电感模块有效的降低了开关损耗,提高了开关频率。开关频率的提高可以有效降低大功率设备的体积和重量。

b. 大功率NPC逆变器

对于中心点钳位三电平拓扑结构(NPC),相对于三相全桥电路,它的优点就是有效降低了开关损耗,适合于高频应用。但是NPC拓扑直流母线有三个电压端子(DC+, GND, DC-),要想在三个端子之间都保证低寄生电感很困难。高寄生电感又会削弱这个拓扑结构的优势。新型的低寄生电感模块有效地解决了这个问题,为NPC拓扑结构应用到大功率装置,如UPS,光伏逆变器,有源电力滤波器(APF)等铺平了道路。

c. 矩阵逆变器

在大多数电力电子装置应用中,保证直流母线环路低寄生电感就可以有效解决关断过电压的问题。但是对于比较复杂的拓扑结构,如矩阵逆变器,由于系统中没有直流母线,就必须保证开关回路包括开关器件,输入端子和输出端子回路的低寄生电感。

6. 结论

对于大功率电力电子设备,如何进一步降低功率模块内的寄生电感一直是个难题。过高的寄生电感增加了开关损耗,限制了开关频率的提高。关断过程中的过电压也给系统稳定性造成伤害。通过实验验证,可以看到本文阐述的理念 – 利用现有标准大功率模块,给模块提供两条回路,一个为螺栓连接的低电阻回路,另一个为通过PCB连接的低寄生电感回路可以有效降低大功率模块内的寄生电感,为大功率电力电子应用开辟了一条新的路径。

责任编辑:gt

-

开关

+关注

关注

19文章

3234浏览量

94134 -

封装

+关注

关注

127文章

8128浏览量

143825 -

电感

+关注

关注

54文章

6161浏览量

102983

发布评论请先 登录

相关推荐

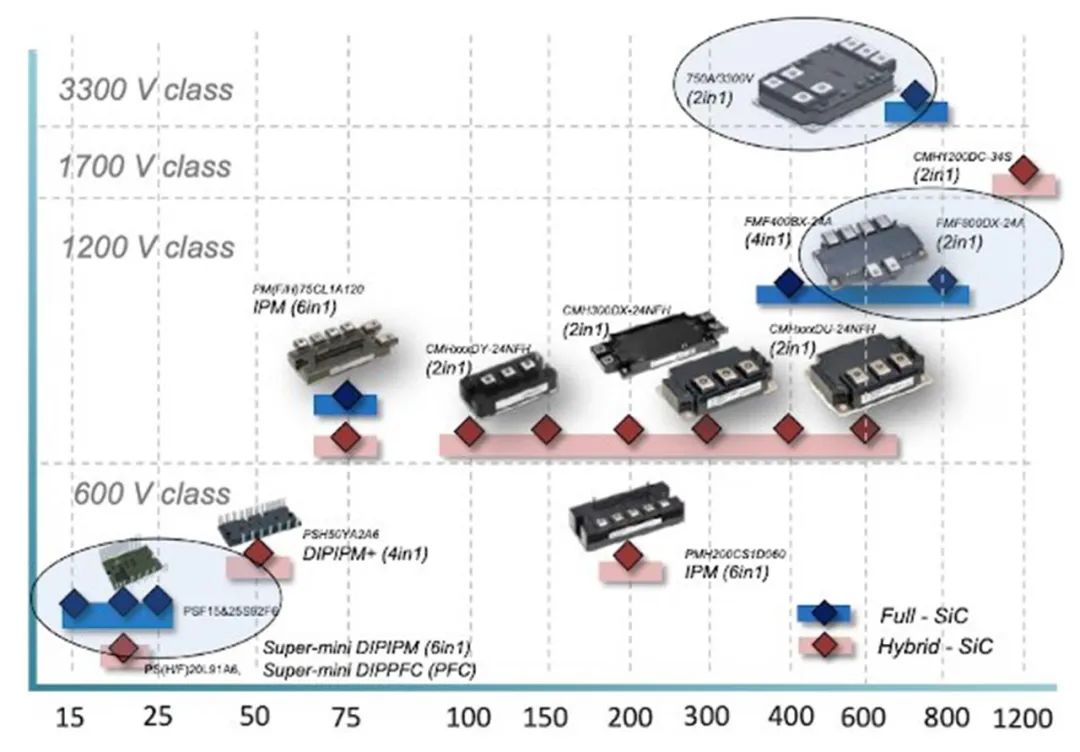

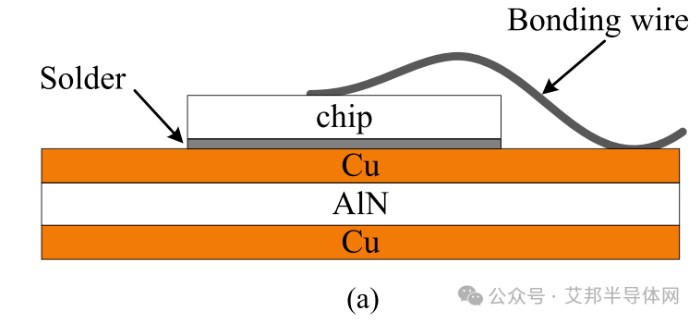

SiC功率模块封装技术及展望

碳化硅功率器件封装技术解析

封装寄生电感对MOSFET性能的影响

用于汽车应用的碳化硅MOSFET功率模块

归纳碳化硅功率器件封装的关键技术

碳化硅功率模块封装中4个关键问题的分析与研究

基于NX封装的低杂感SiC MOSFET模块设计

基于现有标准模块封装实现功率模块的低寄生电感设计

基于现有标准模块封装实现功率模块的低寄生电感设计

评论