作者:盛翠霞,张涛,陈俊江,姚清华,袁红艳

由于高帧频、大面阵CCD数字相机的图像数据量非常巨大,存储流量超过50MBps。而且图像输出速率也比较高,所以高速图像数据的实时记录是一个不易解决的问题。高帧频、大面阵CCD相机的数字视频存储的一般方案是基于高性能计算机体系结构,把PCI总线的视频采集卡与高性能IDE硬盘系统或基于PCI-SCSI桥的SCSI存储硬盘系统结合起来完成任务。这种方案实现起来比较容易,但存在总线瓶颈问题,一次存储占用两次PCI总线,而且还受到操作系统和文件系统的限制,因而在实际应用中存储速度很难突破40MBps。针对这一问题,本文设计出脱离计算机平台的图像数据存储方式,采用FPGA芯片控制时序,运用VHDL语言编程实现微处理器和DMA控制功能,从而协调SCSI协议处理器实现数据的传输。FPGA的运用比单独使用DMA控制器减少了电路板的体积,降低了成本,提高了存储的速率。

1 系统的硬件结构设计

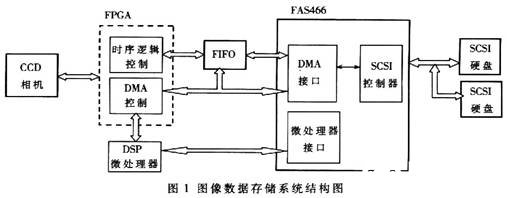

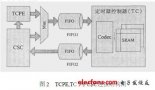

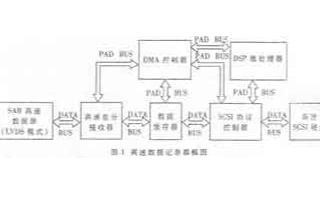

实现SCSI协议和硬盘存储,通常需要有微处理器、DMA控制器、SCSI协议控制器、数据缓存器等硬件支持和相应的软件控制模块。而本系统。DMA控制通过对FPGA编程来实现。图像数据存储系统结构图如图l所示。

1.1微处理器

微处理器负责对各个模块进行协调和控制。本系统所设计的专用高速硬盘存储设备实现数据的持续高速存储,要求处理数据的速度高,因此采用DSP微处理器。微处理器主要功能如下:

(1)完成与外接数据的传输起始、结束控制。

(2)对FPGA进行复位、开始操作。

(3)对FAS466的初始化操作,对传输的异常情况进行中断处理。

(4)对协议控制芯片内部寄存器的读写控制,从而控制SCSI总线的命令传输和状态监控。

对SCSI的命令信息进行解释、执行、管理;对来自SCSI总线的信息状态进行翻译、执行、管理。

1.2 DMA控制器

DMA控制器控制数据发送或接收源的数据缓冲器与SCSI协议控制器内部缓冲器之间的数据传送,这样通过与协议控制器的DMA接口相协调以控制数据源与SCSI总线间的数据传送。本设计采用FPGA器件,利用VHDL语言编程实现DMA控制器功能.而不采用专用的DMA控制器,主要考虑以下一些因素:本设计的数据传输速率达到50MBps,而一般的专用DMA控制器难以胜任;专用的DMA控制器与SCSI协议控制芯片之间的连接需要大量的逻辑转换电路和外围连线,使设计难度加大;使用FPGA器件,除了完成DMA控制功能之外,还可以把电路中的逻辑转换、系统复位等模块设计进去,减小了设备的体积,方便了以后对系统的升级和改进。

1.3 SCSI协议处理器(FAS466)

SCSI协议处理器是SCSI总线操作的执行部件,各公司都有专门的SCSI集成电路芯片作为协议控制器,如Qlogic公司的FAS368M、FAS466等。FAS466(Fast Architecture SCSI Processor)处理器是Qloglc公司1999年上市的一种高性能SCSI引擎,它源于Qlogic公司的TEC450/452三重嵌入式控制的铝系列,可提供Fast40的同步传输速率,它的同步数据宽总线传输速率可达80MBps;支持先进的SCSI自动配置模式的1层和2层协议;内部嵌有微控制器,能够通过编程方式灵活地协调SCSI作业队列.可以工作在启动或目标模式并支持单端或低电压差分模式的SCSI连接。

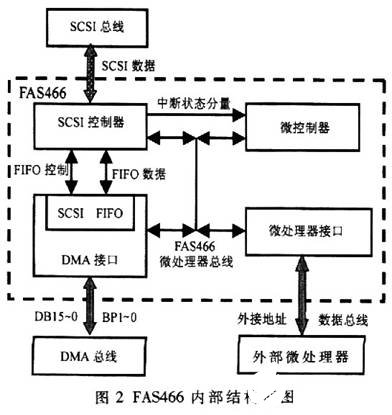

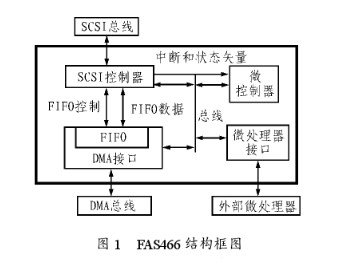

FAS466区别于其他SCSI协议处理器的最大特点是:它采用微处理器和DMA接口结构,而常见的SCSI协议控制器采用PCI接口总线结构。这是本设计采用FAS466的一个主要原因。采用微处理器和DMA接口结构,可以通过DSP对传输进行控制,脱离微机平台,减少传输带宽限制,使数据存储系统具有非常好的灵活性和可移植性。FAS466由SCSI控制器、微控制器、DMA接口和微处理器接口四个模块组成。外部微处理器通过微处理器接口对FAS466进行控制,协议控制器接受微处理器的操作指令,如总裁、选择、失连、复位总线等。SCSI控制器提供灵活、有效的底层SCSI协议控制,微控制器则负责控制数据从DMA接口到SCSI硬盘的传输以及各个模块之间的协调。FAS466的内部结构如图2所示。

1.4 数据缓存器

在设备的输入接口部分,需要有数据缓存单元。数据缓存的目的是为SCSI的高速DMA传输做好准备,使两边数据传输速度匹配。数据的流向一般是一个口进,一个口出,不对信号进行任何处理。普通的存储器在写入的同时不能读取,双口随机存储器RAM虽然也可完成这个任务,但是由于它需要复杂的地址译码电路,所以不采用。采用FIFO芯片,可以去掉复杂的缓存器译码电路,大大简化了系统设计。缓存单元在结构上相当于先进先出(First In First Out,FIFO)队列,即先到的数据先被存储。本设计中FIFO选用IDT公司的IDT72V2113芯片。

2系统的软件设计

软件设计是本系统设计的重点和难点,它负责对相关硬件的控制和协调,最终实现SCSI协议、硬盘的控制和DMA传输等。软件设计分为SCSI控制软件和DMA控制器的FPGA实现两部分。下面分别进行讨论。

2.1 SCSI控制软件

一般来说,要完成一次数据交换必须完成SCSI总线的仲裁、选择、消息、命令、数据和状态等阶段。这些阶段,微处理器通过对FAS466寄存器的读写控制来实现。

FAS466的寄存器主要有:

(1)命令寄存器:DSP通过向命令寄存器写入相应指令,控制FAS466完成初始化、复位、总线分配与复位以及SCSI总线各个阶段的转变等功能。

(2)FIFO寄存器:这是一个128字节的双端口RAM,SCSI硬盘和FAS466之间的数据交换都通过该FIF016字(深)的FIFO寄存器来完成。

(3)传输计数寄存器:是一个减法计数器,用于保存一次DMA数据传输的字节数。

(4)中断寄存器:DSP通过FAS466中断寄存器了解SCSI命令的执行情况,从而决定程序的执行流向。

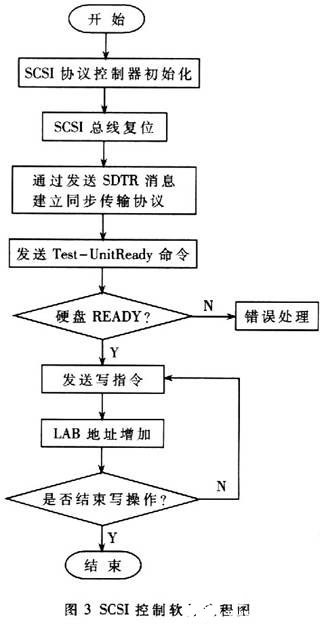

SCSI控制软件流程如图3所示。首先初始化SCSI控制器,然后SCSI控制器与SCSl硬盘建立同步传输协议,在硬盘准备好的情况下才可以发送各种SCSI命令,如读、写等,同时处理好各种意外情况的发生。

2.2 DMA控制器的FPGA实现设计

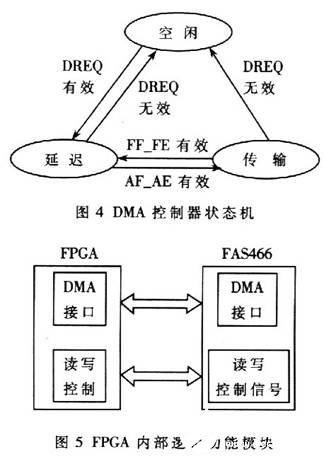

FAS466外部DMA控制器由FPGA实现。FAS466通过DREQ信号有效请求数据传输,当DMA控制器检测到DREQ有效并且外部FIF0非空时,使DACK有效并通知FAS466开始DMA传输。DMA控制器的状态机如图4所示。

FPGA除了实现FAS466的外部DMA控制器之外,还实现FAS466与外部微处理器的部分逻辑和其他逻辑控制。FPGA内部逻辑功能模块如图5所示。

本文在FAST-40 SCSI协议基础上,对实时高速数字视频SCSI存储系统的软硬件进行了设计。利用FAS466作为SCSI控制器宴现启动器功能,控制两块SCSI硬盘实现直接存储,充分利用SCSI总线的带宽,从而大幅度提高了系统的效率。初步建立了较完善实用的直接存储的结构体系,实现存储流量达70MBps。为解决大面阵、高帧频CCD数据实时存储奠定了良好的基础。该项技术的解决,将会大力促进在科学研究、军事技术、尤其在航天、航空侦察及高速数据记录领域的应用发展。

责任编辑:gt

-

控制器

+关注

关注

112文章

16376浏览量

178166 -

微处理器

+关注

关注

11文章

2263浏览量

82473 -

缓存器

+关注

关注

0文章

63浏览量

11665

发布评论请先 登录

相关推荐

符合Ultra2的高性能SCSI处理器FAS466

基于DSP的第三代无线通信协议处理器设计

TCPIP协议处理器的多连接管理设计

基于FPGA并以Flash为存储介质的高速图像数据存储系统设计

基于FAS466存储系统的DMA控制器设计

基于FAS466的CCD相机数字视频实时存储系统设计

SCSI控制器进入复位状态时的注意事项

基于SCSI协议处理器FAS466实现图像数据存储系统的设计

基于SCSI协议处理器FAS466实现图像数据存储系统的设计

评论