从硬件结构、曝光策略和模拟结果入手,在传统滚筒式曝光基础上,通过对用户设定区域像素饱和值的统计和曝光时间选择算法,提出了一种CMOS图像传感器大动态范围自适应曝光的设计。曝光时间可从1μs至65ms,探测光强范围达到10-1~106lux,设计将充分发挥现有像素性能,实现快速实时的自适应曝光需求。

1 引言

CMOS图像传感器(CIS)具有集成度高、制做工艺通用、体积小、功耗低、无光晕等特点,在非接触无损测量及目标监控等方面,与较为成熟的CCD系统一样,发挥着越来越重要的作用。但由于CIS普遍采用光电二极管线性有源像素,动态响应范围较小。当前,提高其动态范围和自适应曝光调节成为关键问题。为提高CIS的动态范围和高分辨率,多采用对数像素、多次曝光、多次采样重构、像素自调节多次曝光等技术。

鉴于片上反馈系统对自适应调节快速实时等特点,针对实际视觉和工控测量应用等要求,本文从CMOS图传感器像素阵列的数字控制和预处理电路出发,以现有滚筒式曝光为背景,提出了一套通过自适应调节曝光和用户预设方式曝光的CMOS图像传感器系统,曝光时间可从1μs至65ms,在光电响应效率为1.0V/lux·s、可调增益为1和8bit模数转换器(ADC)情况下,探测光强范围可达到10-1~106lux,大幅提高现有CMOS图像传感器线性自适应响应能力。

2 自适应曝光判决算法

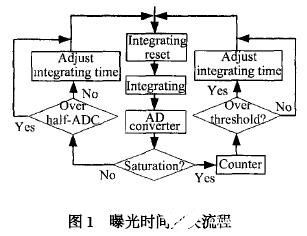

采用帧间的自适应曝光调节方式,即每帧内的像素点曝光时间一致,光照响应为线性曲线。根据帧内最大非饱和像素电压,以最小曝光时间T的倍数关系调节下一帧曝光时间,来适应环境照度及最大分辨率。每帧的曝光时间将通过接口实时传输给测量分析电路。具体判决算法为:

CMOS图像传感器以T或用户设定时间开始曝光。当第1帧有效图像采集结束开始输出时,曝光控制系统将统计帧内指定区域的像素饱和数,并记录帧内最大非饱和像素电压,即当前曝光条件下图像传感器的最大分辨率。当帧内像素饱和数超过统计阈值,表明曝光过长,将缩短下一帧曝光时间;相反,判断最大非饱和像素电压是超出ADC输出量程1/2。当未超过时,表明曝光不够,由曝光调节表(表1)改变下帧曝光时间;否则按原有曝光时间继续曝光,曝光判决流程如图1所示。ADC输出与光照关系为

V=As(λ)Et (1)

其中:E为当前光照度;S(λ)为像系相对光谱响应率;t当前曝光时间;A为可调放大器增益。

从表1可看出,当光照度骤升或骤降时,只要ADC输出仍在1/2LSB~255内,CMOS图像传感器可以在下一帧就调节到合适的曝光时间使输出值达到ADC半量程之上,实现28E至E光照度变化的快速跟踪自适应。而在1/2LSB~1/256LSB内,自适应系统将可在2frame内达到跟踪。

当光照度骤升到达像素饱和时,因无法判断曝光时间缩减程度,自适应系统将重新搜索从当前曝光时间至最小曝光时间内的最佳曝光时间,方案设计了3种搜索方式:曝光缩短为当前曝光时间t的1/256;曝光缩短为t的t1/2取整;曝光缩短为t的1/2。当调节曝光后的图像仍不满足要求时,将按照上述方式之一或曝光表1继续调整曝光时间。以曝光时间224T至23T变化为例(100~106lux),介绍3种方式的搜索速度,方式1需4frame时间,方式2需3frame时间,方式3需21frame时间。由此可知,照度变化不大时,方式1较好;相反,方式2较好。因此针对不同应用情况,曝光系统将根据不同方式进行搜索。

3 自适应曝光电路设计

自适应曝光CMOS图像传感器系统在传统三管有源像素结构、滚筒式曝光和输出模式背景下,根据帧内最大非饱和像素电压,动态调节帧间曝光时间,避免了像素自适应曝光所需与像素阵列相当的RAM存储空间及多次曝光造成的响应曲线压缩,芯片控制复杂度和面积得到大幅降低。此外,该电路允许用户对图像曝光时间及饱和统计范围进行直接调整及控制。系统共包括6部分:像素阵列、8bitADC等模拟电路、饱和像素统计单元、像素扫描单元、曝光调节及时序控制单元,如图2示。

3.1像素饱和统计单元

像素值超过255称为饱和(数据采集为8bitADC),该部分主要完成对像素阵列内指定区域饱和像素值的统计。由于在特定场合(如夜间监视系统),零星灯光或反射光将造成图像部分像素出现饱和,如图3(a)区域a示。如果按照此饱和值调节曝光,将降低图像整体分辨率。因此,设计采用允许用户在图像任意位置设定任意大小的饱和统计区域及阈值的方法来避免上述干扰,如图3(a)中b为用户统计区域,即关注区域。

该单元主要由寄存器组、饱和侦测及统计电路组成。寄存器组记录用户指定区域的大小、位置以及统计阈值,未指定时使用默认值。饱和侦测电路采用模拟比较器结构,降低采用数字比较器时的大面积电路和计算延时,也避免了因反相器侦测饱和时的低精度。电路在每行像素数据输出时判断进入统计区域的像素电压,比较结果直接作为饱和统计计数器使能端驱动。当统计计数超过阈值时,表明被测图像光强已不满足用户要求,需缩短曝光时间。此时该统计单元将向曝光调整电路发出flag信号,开始曝光选择,电路结构见图3(b)示。

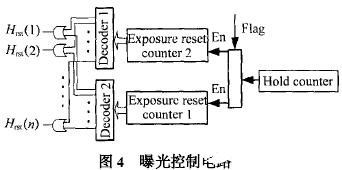

3.2 像素扫描单元

由8bit输出寄存器、临时寄存器、比较器及暂存控制逻辑组成。主要完成1frame图像中最大非饱和像素电压的寻找及存储。每行像素数据输出时,扫描单元在scanphase阶段实时完成像素点扫描判断工作(见图4示)。当完成1frame图像传输后,临时寄存器中存储的最大非饱和像素值将作为下一帧曝光时间选择的参考值。

3.3 曝光选择单元

由8bit最小曝光寄存器、24bit曝光倍数寄存器、掩码电路和曝光判决电路组成,主要完成下一帧曝光时间的提取及选择。最小曝光寄存器存储CMOS图像传感器最小曝光时间,当系统时钟为20M时,最小曝光时间为1μs,寄存器值为14H;曝光倍数寄存器存储当前曝光时间与最小曝光时间的倍数值。在每帧Re2selectphase阶段(见图5),掩码电路将先完成对扫描单元临时寄存器值的分析及曝光时间提取工作,即根据非饱和电压值最高位产生下一帧曝光时间与最小曝光时间的倍数值(见表1第2列),该值将存储至曝光倍数寄存器中。随后,曝光判决电路将根据饱和统计单元的flag信号决定是否更改下一帧曝光时间。由上可知,曝光时间实际为最小曝光时间的2次幂,虽然这将造成图像分辨率的一定下降,但可避免为每个电压值设置曝光时间所需的128×8bit空间,从而降低电路复杂度。

4 像素复位曝光控制逻辑设计及分析

由于图像传感器系统为数模混合系统,而模拟信号抗噪声能力较弱,高速交变的数字信号将给模拟电路引入不必要的噪声,直接影响图像传感器的采集精度,导致图像质量下降。所以设计在像素曝光、采集逻辑以及数模电路工作时序上做了一些改进:1)电路采用格雷编码,两相邻状态只有1bit不同,这将降低状态转换时信号跳变次数,减少数字噪声的引入。2)数字电路的工作时钟(workcycle)分为idle和work2个阶段,在像素采集阶段不翻转,保证模拟、数字电路分时工作,如图5所示。

4.1 像素曝光复位分析

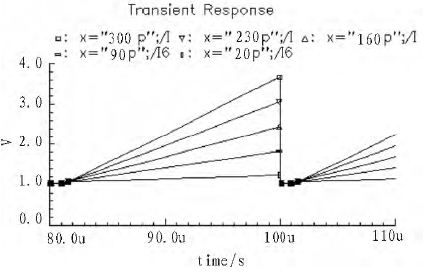

曝光(积分)时间为相邻复位信号与采样信号的时间差。由于滚筒式曝光时序以行为单位,对像素阵列进行信号采样、处理和输出。1行内所有像素曝光处理为并行的,各行间像素曝光处理为串行的。因此,处理1行像素所需时间=曝光时间+数据处理时间+像素输出时间。复位曝光逻辑如图5所示,Vout为帧同步信号;Hout为行同步信号;Hrst为曝光复位信号;H(n)为第n行的行有效信号;Hrst(n)为第n行的曝光复位信号out为输出像素时钟;P(n)为第n个像素有效信号。由图可知,曝光复位信号Hrst为行同步信号Hout相关信号,延迟时间=帧时间-曝光时间,即图5(a)中hold1或hold2部分。所以改变曝光时间是通过调节hold宽度来完成的,曝光寄存器实际存储着与曝光时间相应的hold值,1frame时间=曝光延迟时间(hold)+曝光时间(integrating)。

曝光自适应时序图5(b)所示,第1行像素在完成第N+1帧曝光时间后(intergating1),将根据当前曝光选择单元的结果开始第N+2帧复位和新曝光长度(intergating2)的曝光,同时ADC将处理和输出第1行的第N+1帧的数据。因此,在第N帧光强变化的图像在第N+3帧才被记录下。造成该延迟主要有两种原因:1)曝光固有延时,曝光到采集数据最长需要1frame时间;2)帧间自适应调节固有延时,由于采用搜索整帧图像后确定曝光时间,当图像第n行采样电压时,第1行数据实际已按照原曝光时间开始采样,需要再等1frame时间,第1行才能采用新曝光时间。所以当t1时刻光强发生变化时,曝光电路在t2时刻才能选定新曝光时间,而以新曝光时间采集的图像在t3时刻才能被记录,即该系统将存在最大3frame时间的固有延迟。但随着输出帧频的提高,该固有延时时间将能够相应减小。

4.2 像素复位曝光设计

上述曝光切换时序可看出,当2frame曝光时间改变较大时,不同曝光时间将存在叠交。如图5(b),第N+2帧第1行曝光复位发生在第N+1帧第n行曝光复位前(overlap段)。如利用1组复位曝光逻辑将引起控制混乱,因此设计采用2组曝光复位控制时序。当曝光时间不变时,复位计数器1将在延迟行同步信号的hold1时间被使能,开始从第1行至第n行的曝光复位,当完成1frame后,复位计数器1将停止工作,等待hold1时间后再次使能。当曝光时间调节时,如复位计数器1还未计满将继续工作,直至计满整帧。而此时hold寄存器将等待hold2时间后,开始使能复位计数器2。由于2组复位计数器不对同一行复位,因此前后2frame可在不同曝光时间下正常运行。如图4示,曝光调节信号(flag)将更新延迟值并使能另一组闲置曝光复位寄存器。

5 模拟仿真结果

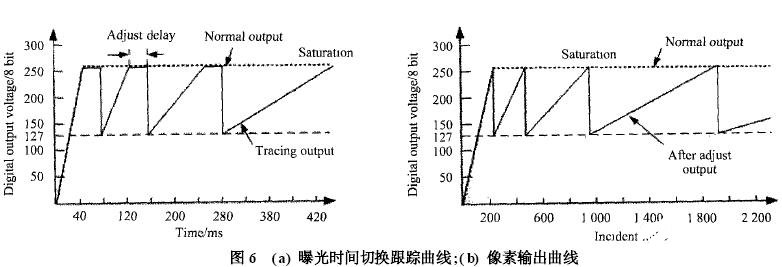

根据上述原理,利用XILINX公司的ISE及Modelsim软件,对曝光选择控制电路进行了数字电路设计及模拟。结合光电二极管光电响应实际测试结果,进行模数混合信号仿真,如图6(a)所示,在帧频为100frame/s时随光强变化,CMOS图像传感器调节曝光时间及输出信号值,其中调节延时约为3frame时间。图6(b)为光强与输出的相关曲线。像素电压值随着光强增加,曝光时间从65ms(216T)调节至4ms(212T),多帧响应组合后输出接近指数曲线。

6 结论

设计通过用户预设和帧间自适应曝光调节方式,实现了CMOS图像传感器大动态范围自适应能力。相比传统滚筒式积分复位逻辑,该控制结构将能更充分发挥像素响应特性,并达到光强自适应曝光调节。由于该结构逻辑简单,不改变像素阵列,因而随着像素阵列不断增大,仍能在保证速度的前提下,对光强自适应调节,在对多帧图像进行数字重构后处理时,也可进一步提高成像质量,具有很高可靠性和兼容性。

责任编辑:gt

-

CMOS

+关注

关注

58文章

5675浏览量

235106 -

图像传感器

+关注

关注

68文章

1882浏览量

129437 -

模数转换器

+关注

关注

26文章

3123浏览量

126733

发布评论请先 登录

相关推荐

微光CMOS图像传感器读出电路设计

CMOS图像传感器电路设计

基于CMOS图像传感器实现快速实时的自适应曝光电路设计

基于CMOS图像传感器实现快速实时的自适应曝光电路设计

评论