MPEG-4SP ( Simple Profile)编码器以其出众的压缩效率和图像质量受到了广泛关注,并随之诞生了很多基于PC平台的编解码器(如Divx、Xvid等) ,在远程教育和高清晰度电影等方面得到了广泛应用。而2001年发布的MPEG-4标准V2. 0 中包含的ASP编码器,则在SP的基础上增加了一些新的工具,进一步提高了压缩效率,因此更适合在无线视频通信和数码摄像机等嵌入式系统中应用。

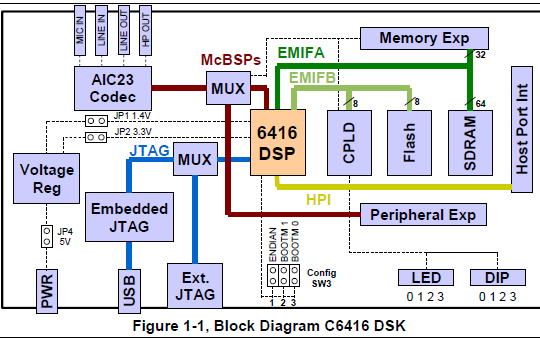

1 硬件平台TMS320C6416介绍

选用的实验硬件平台是TMS320C6416 DSK(DSP Starter Kit) 。其核心处理器为美国TI公司的高性能定点32位DSP C6416,基于第2代高性能Ve2lociTI. 2 VLIW结构,带有64个32位字长的寄存器,8个高度独立的功能单元( 2个乘法单元, 6个算术逻辑单元) ,工作时钟频率为600MHz,峰值处理速度可达4800Mbit/s。C6416 DSP具有1MB 的片上存储空间,采用两级缓存结构。其中同CPU直接相连的L1P和L1D能以CPU相同的速度运行, 而L2CACHE有5 种配置模式,可根据实际需要来设定L2CACHE的大小。同时C6416还具有64个独立的EDMA通道,可在CPU 后台进行大量的数据搬移,并集成了16MB的SDRAM,可配置为高速缓存 ,提高访问效率。

2 MPEG-4ASP视频编码

运动图像专家组MPEG于2001年在其新发布的V2. 0版本中增加了一些新的工具和框架,其中包括了ASP 。ASP 在SP的基础上增加了对B-VOP、1/4像素精度的运动矢量、可选量化器 、全局运动补偿GMC等的支持,进一步提高了压缩效率。

(1)B-VOP使用双向预测来提高运动补偿的效率,也即每个block块或者macroblock宏块都可由前向和后向预测加权得到。

(2) 1/4像素运动矢量 : 在进行运动估计和补偿之前, 参考VOP先在1/2像素位置处,进而在1/4处进行插值,尽管这样增加了运动估计、运动补偿和图像重建的复杂度,但编码效率相比SP编码器得到了提高。

(3)可选量化器:在ASP中提供了一种可选的反量化方式。在这种方式中,量化系数FQ ( u, v)按照下面的方式进行反量化来生成系数F (u, v) : if (FQ = 0) F = 0; elseF = [ (2 ×Fc( u, v) + k) ×WW ( u, v) ×QP ] /16。其中WW 是8 ×8的加权因子矩阵,这种反量化方式使得编码器可根据量化系数在块中的位置,使用WW 改变步长。

(4)全局运动补偿(GMC) :同一视频对象(VO)中的宏块可能经历相似的运动,如摄像机镜头的缩放和旋转等造成的线性移动,其中的一些宏块可能向同一方向运动。带GMC的编码器只需发送少量的运动参数就能为整个VOP描述这个“全局”运动。因此,当VOP中相当数量的宏块拥有相同运动特性时, GMC就可以显著的提高压缩效率。

3 软件移植及优化

由于DSP不同于普通的PC环境,因此简单的将代码放到DSP上去编译,运行效率低甚至不能运行,必须进行适合DSP特点的代码移植、改写和优化工作,才能达到实时性要求。

3. 1 软件移植

为使代码适合在DSP平台上运行,首先删除程序代码中大量的printf等调试信息,对必要的信息输出改用puts,以减少函数开销;对double类型数据改用long类型定义;删除不必要的浮点运算(如PSNR的计算) ,必要的浮点运算通过定标来实现。

3. 2 存储器优化

C6416DSP有1MB 的片上存储空间,最大能以CPU时钟频率进行访问。在DSK上集成了16Mb/s的SDRAM,可通过EM IFA以100MHz的频率进行访问。访问速度上存在的差异以及CPU寻址外部存储空间将导致流水线停止数个周期,因此,如何合理利用C6416的片上存储空间和二级缓存结构成了非常关键的因素。将1MB的存储空间分为256k的L2CACHE和768 k的L2SRAM,代码段、全局数据等放在片内存储器L2SRAM 上, 外部SDRAM 设定为可高速缓存(Cacheable)以提高访问效率。这些设置可以通过调用CSL (Chip Support Library)库函数来完成:

#include

#include

CSL_init ( ) ;

CSL_enableCaching(CACHE_EM IFA_CE00) ;

CACHE_setL2Mode (CACHE_256 k CACHE) 。

3. 3 项目级优化

TI为其集成编译环境CCS提供了一系列的编译优化参数,可根据代码性能要求进行选取。因此可以通过不断对各个参数( - mw, - pm, - o3, - mt等)进行组合、优选,这可以通过CCS 2. 20的PBC选项来完成。同时在代码链接过程中,对代码段链接顺序进行一定的安排,可以减少程序执行时代码调用带来的缓存缺失,提高程序的执行效率。

3. 4 代码优化

代码优化是MPEG-4 ASP视频编码器软件开发中的一个重要环节,未经过优化的代码在DSK平台上的执行效率很低,平均约25s才进行一帧编码,而实时性的指标为每秒25帧以上。

(1)使用TI库函数

TI提供了图像处理函数库IMGL IB,可以调用其中的函数进行FDCT和IDCT变换。

(2)对C代码进行改写

首先对程序中的循环操作进行分解展开,对不能展开的循环则合理安排循环内外层,以更大程度地提高流水效率。C6000的编译器还提供了许多内联函数( intrinsics) ,这些内联函数能直接映射到对应的汇编指令,提高程序的效率。同时可利用编译指示伪语句( Pragma Directive)向编译器提供一些先验知识,以提高编译效率。如用#p ragma (minimum value, maximumvalue, factor)向编译器指出循环执行的信息,这样便于编译器利用数据打包等技术进行优化。以计算宏块中像素同均值偏差的dev16函数为例,采用了以上方法改写后,函数执行周期数由277 个cycles变为130个cycles (同在o3条件下) ,性能提升超过50%。

(3)进行线性汇编改写

线性汇编是针对C6000 的结构特点优化设计的介于C和汇编语言之间的一种编程语言,其编译效率能达到汇编代码的90%以上。同时C64x系列DSP针对图像和视频应用增加了许多特有的指令,使得这些应用的代码编写效率得到了提高。如在ASP视频编码器中,半像素插值使用的avgu4、shrmb、unpklu4 和unpkhu4指令,计算SAD 时用到的dotpu4、subabs4 指令,图像重建时用到的SPACK2指令等等。也方便了代码的编写,如ME (Motion Estimation运动估计)时在参考图像帧中进行像素值读取的LDNDW 指令,解决了参考图像中数据不满足双字对齐的问题。下面给出了将函数transfer_16 to8copy( )通过线性汇编改写后的代码,同在o3选项下,线性汇编代码只需C代码15. 8%的指令周期。表1给出了部分代码改写前后的性能对比(同在o3优化选项下) 。

。 global _transfer_16 to8copy

_transfer_16 to8copy: 。 cp roc dst, src, stride

。 reg pdst, p src, count

。 reg ahi: alo, bhi: blo, chi: clo

mvk 8, count

mv dst, pdst

mv src, p src

loop: 。 trip 8, 8

lddw 3 *psrc, ahi: alo

spacku4 ahi, alo, blo; keep the value

in the range 0 - 255

lddw 3 *+psrc (8) , chi: clo

spacku4 chi, clo, bhi

stdw bhi: blo, 3 pdst

add pdst, stride, pdst

add p src, 16, p src

[count ] sub count, 1, count

[ count ] b loop

。 endp roc

3. 5 数据搬移优化

由于片上存储空间有限,因此只能将参考图像及重建图像等数据放在外部SDRAM中,但也导致了访问外部存储器时带来的巨大开销。而C64x具有的EDMA和QDMA只需花费数个时钟周期进行参数初始化后,就可以在CPU 后台进行高速的数据搬移操作,提高了程序执行效率。针对简单的数据搬移,可以利用CSL库提供的DAT函数进行。以一段简单的2D数据搬移为例,给出利用QDMA后的实现代码:

unsigned int transferID = DAT_open (DAT_CHAA-NY,DAT_PR I_LOW,DAT_OPEN_2D) ;

DAT_copy2d (DAT_2D2D, con, ref, 16, 16,width) ;

DAT_wait ( transferID) 。

对复杂的数据搬移,可以采用多通道的EDMA来实现。EDMA提供了linking和chaining的机制,在部分数据搬移完成后,自动对EDMA链路或通道参数进行更新载入,无需CPU干预,特别适合进行大量的数据搬移。然而需要注意,由于SDRAM中的待搬移数据在L2CACHE中存在副本,因此在进行数据搬移前,需对L2CACHE和SDRAM中的待搬移数据进行一致性操作(Coherence Operations) ,否则将得不到正确的结果。

4 实验结果与分析

通过上面提到的软件优化方法,在C6416 DSK上对MPEG - 4视频编码器进行了仿真。为了得到编码信息,如峰值信噪比( PSNR) ,在代码中临时加入了calc_p snr ( )函数,以便于对ASP编码器和SP编码器进行性能比较。以352 ×288大小的CIF格式foreman视频序列为例,在编码码率为256 K时,对分别支持GMC、QPEL和B - VOP以及同时支持上述3 个工具的ASP编码器和SP编码器进行了性能对比( SP编码形式为“IPPPP.”, ASP使用B - VOP时为“ IBBPBB-

PBBP.”) 。

表2给出了得到的编码文件长度,可以看出ASP编码器相比SP编码器其存储空间要求更小,而图像质量变化不大,因此更适合于数码摄像等嵌入式场合的应用。

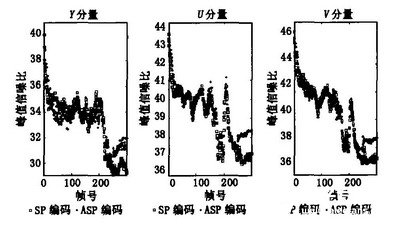

图1 对ASP编码器(支持B -VOP、GMC 及QPEL) 与SP 编码器进行了比较, 可以看出前者在PSNR性能上较后者平坦,均方差较小,图像质量更为稳定。

图1 foreman序列ASP和SP视频编码器PSNR性能比较

虽然压缩效率提升,但导致计算量上升,并且由于编码时采用了B-VOP增加了后向预测,编码时延增大,图像帧速率有所降低。

5 结束语

由于ASP视频编码器具有更高的压缩效率,虽然在编码速度上有所降低,时延增大,但仍能在DSP上进行实时编码,因此适合在存储容量受限的场合(如数码摄像、视频监控网络等领域)应用。

责任编辑:gt

-

处理器

+关注

关注

68文章

19155浏览量

229044 -

芯片

+关注

关注

453文章

50360浏览量

421638 -

编码器

+关注

关注

45文章

3584浏览量

134107

发布评论请先 登录

相关推荐

急需TMS320C6416的板级支持包bsp/bsl,求助

请问有TMS320C6416和TMS320C6747的对比表吗?原来用的TMS320C6416,现在想换TMS320C6747 或TMS320C6747

TMS320C6416 pdf datasheet

TMS320C6416 的软件编程优化

MPEG-4 ASP视频编码器的软件优化设计

基于DSP TMS320C6416的实时图像处理系统

基于DSP TMS320C6416的数字下变频技术

基于TMS320C6416的语音净化系统

TMS320C6416 DSK技术参考详细资料免费下载

TMS320C6414/TMS320C6415/TMS320C6416定点数字信号处理器数据表

使用TMS320C6416协处理器:Turbo协处理器(TCP)

基于TMS320C6416芯片实现ASP视频编码器的设计及应用

基于TMS320C6416芯片实现ASP视频编码器的设计及应用

评论