本世纪以来,随着以TI公司的TMS320C6000系列、Philips公司的Trimedia、Equator公司的BSP-15等为代表的高性能DSP的出现,由嵌入式处理器来实时高速完成大数据量的数字视频/音频编解码处理成为可能,结合网络通信技术,集可编程图像/声音编解码、网络传输、和自动化技术为一体的嵌入式数字视频监控系统应运而生。以DSP为核心的嵌入式数字视频监控系统,配合嵌入式实时操作系统,可以根据应用对功能、可靠性、稳定性、成本、体积等的综合要求,对软/硬件进行裁剪,以满足视频监控发展的数字化和网络化的两大需要。

本文以TMS320C6000系列DSP中的一款TMS320DM642多媒体芯片为例,来具体说明如何设计嵌入式DSP数字视频监控系统的硬件电路。

视频监控系统必需的硬件配置

1.一体化模拟前端

视频监控系统的模拟前端是来自摄像机和麦克风的模拟视频和模拟音频信号,为了降低整个系统的成本,一般会有多路视频和音频信号输入。而摄像机一般安装在平台上,摄像机和平台的控制命令一般通过异步串口提供。另外,对于一个完整的视频监控系统来说,还需要对环境进行监控,如门禁控制、报警、停车管理等,这些功能一般用数字I/O实现。

由此可见,视频监控系统一体化模拟前端,除了需要提供多路的模拟视频/音频的输入端口外,还需要为平台控制提供标准的RS232/RS422/RS485异步串行接口,及环境监控的数字I/O。

2. 数字化

为了用微处理器实时地对输入的视频/音频信号进行数字化的编/解码处理,必须将输入的模拟视频/音频信号进行数字化,这部分工作由视频解码器和音频解码器完成。每个模拟视频输入对应一路视频解码器,每个模拟音频输入同样对应一路音频解码器。

实时处理数字视频/音频数据

模拟视频/音频信号数字化后,为了能够对高速、实时产生的大量数据进行传输、存储、回放、和分析等功能,首要的工作必须实时地完成大数据量、大计算量的数字视频/音频的压缩编码处理。数字视频压缩编码算法有:MPGE 2、MPEG 4、H.263、H.264等,数字音频压缩算法有:G.711、G.722、G.723、G.728、G.729等。

实时完成这样的算法需要高速的处理器来实现,高性能DSP的出现正好满足了这一需求。另外还需要高速、大容量的存储器作缓存。DSP与高速、大容量存储器构成数字视频监控系统的核心。

数据的存储和传输

不同的视频监控应用,对压缩后的数字视频/音频数据的处理各不相同。对于记录型应用,需要对压缩后的数据进行长时间存储,以便回溯。而对于远程监视型应用,则需要将压缩后的数据通过网络进行传输。在数字视频监控系统对视频/音频信息进行实时监视、记录、回溯处理的同时,还需要记录相关的时间信息,所以需要提供硬件实时时钟。另外,为了保护数字视频监控系统软/硬件开发者,尤其是软件开发者的知识产权,还必须提供安全、可靠的硬件加密措施。

TMS320DM642视频监控系统的电路设计

TMS320DM642是TI公司在其最高性能的TMS320C64x系列DSP基础上专门为多媒体应用而设计/开发的DSP。TMS320DM642采用TI第2代超长指令集结构(VelociTI.2)的TMS320C64x DSP内核:

·2级Cache(2×16K字节1级程序和数据Cache,256K字节2级Cache)

·支持8个8位和4个16位并行MAC运算,有利于图像处理

·64通道EDMA,方便高效数据传输

·主频600MHz,4800MIPS峰值处理能力,可实时处理4路CIF或1路D1

·64位、133MHz外部存储器接口(EMIF)

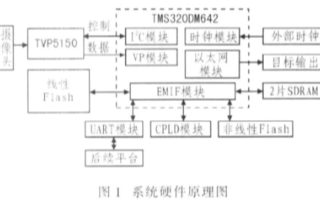

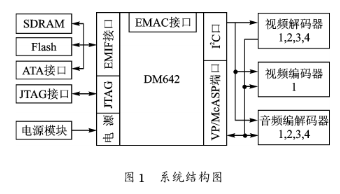

图1 TMS320D642视频监控模板的构成

1. TMS320DM642基本系统

TMS320DM642基本系统由TMS320DM642 + 外扩的存储器和外设组成,而外扩的存储器和外设均通过TMS320DM642的外部存储器接口(EMIF)进行扩展。其次, TMS320DM642基本系统所必须的外扩资源:

Flash:4M×8位,存放固化程序,以便进行ROM 引导

UART:2×8×8位,扩展2个异步串口(RS232/RS422/RS485)

板上寄存器: n×8位,若干个8位状态/控制寄存器

ATA硬盘接口: 2×8×16位,本地大容量存储接口

2. 视频接口

视频接口涉及标准模拟视频输入/输出、模拟视频信号数字化(解码器)、数字视频信号转换为模拟视频信号(编码器)、以及视频编码器/解码器如何与TMS320DM642的接口。

视频接口的总体设计要求:

模拟视频输入: 4路标准PAL/NTSC复合视频CVBS或分量视频Y/C模拟视频输入。

模拟视频输出:1路标准PAL/NTSC复合视频CVBS或分量视频Y/C模拟视频输出,用于本地预览或特性测试。

据此,选择视频解码器和编码器:

视频解码器:选用TI公司的TVP5150A,其输入为标准的PAL/NTSC复合视频CVBS或分量视频Y/C模拟视频,输出为标准的8位BT.656数字视频数据流。

视频编码器:选用Philips公司的SAA7121,其输入为标准的8位BT.656数字视频数据流输入,输出为标准的PAL/NTSC复合视频CVBS或分量视频Y/C模拟视频。

TVP5150A和SAA7121均有2个外部接口,数据口:用于输入/输出数字视频数据流,其中包含8/10位数据线,时钟SCLK行/场同步控制信号HSYNC/VSYNC、FID等接口信号。控制口:用于设置视频编/解码器工作参数和反馈状态信息,用I2C总线实现。

TMS320DM642的每个视频口可配置为上(B)、下(A)2个通道,但2个通道必须同时为视频输入口或输出口。VP0的A通道与McBSP0复用,VP1的A通道与McBSP1复用,VP0和VP1的B通道与McASP复用。

TMS320DM642视频口与视频编、解码器的接口如图2所示。

作为视频输出口时,视频口必须要为视频编码器SAA7121提供视频时钟和行/场同步信号。视频编、解码器的参数配置则通过I2C总线进行,由于TVP5150A的I2C从地址只有2种选择,所以DM642的一个I2C总线接口4片TVP5150A时,需要通过2选1开关SN74CBT3257来切换控制。

3. 音频接口

TMS320DM642音频接口涉及标准模拟音频的输入/输出、音频编解码器Codec的连接问题。

音频接口的总体设计要求:

模拟音频输入:4路标准麦克风输入或立体声模拟音频输入(2V有效值)。

模拟音频输出:1路标准立体声模拟音频输出(2V有效值)。

采样同步:音频采样必须与视频采样同步。

据此,音频编解码器,选用TI公司的TLV320AIC23 B,麦克风/立体声模拟输入/输出,数字音频数据流输出/输入。

TLV320AIC23B有2个外部接口,数据口:用于输入/输出数字音频数据流,其中包含DIN、DOUT数字音频数据流,BCLK串行位-时钟,LRCIN、LRCOUT左右通道时钟。控制口:用于设置音频编解码器工作参数和反馈状态信息,用I2C总线实现。

还有TMS320DM642的多通道音频接口(McASP)具有8个串行收/发引脚AXR[7:0],所有接收引脚公用接收帧同步AFSR和时钟ACLKR、AHCLKR信号,所有发送引脚公用发送帧同步AFSX和时钟ACLKX、AHCLKX信号。

McASP接口与音频Codec的连接如图3所示。

4. 外部接口:

经TMS320DM642压缩处理的数字视频数据,需通过一定的外部接口进行传输。DM642提供3种外部接口,但它们复用引脚,每次只能配置为一种外部接口。DM642通过复位时某些特殊引脚电平的配置,可分别提供下列3种接口:

* 32-位PCI接口

* 32-位HPI接口

* HPI16 + 以太网接口

为了简化设计,HPI-32和HPI-16均借用PCI连接器与外部主机接口,并用PCI总线上的B3(GND)和B10(保留)作为3种接口的自动检测和自动接口配置。另外,以太网接口信号与PCI或HPI-32信号在板上并存,所以这些信号需要用2选1开关SN74CBT3257来切换。还需要注意的是,DM642的PCI接口只支持+3.3V环境,为了适应+5V PCI总线环境,PCI总线与DM642之间用SN74CBTD16210和SN74CBT3245A进行电平转换。

总结

TMS320DM642作为一款高性能/价格比、专用于多媒体应用的DSP,已被国内、外视频应用从业者广泛接受和采用。目前国内已有多家单位在‘DM642上成功地开发了MPEG4、H.264等视频编码算法,单片’DM642可同时完成4路CIF格式的MPEG4或H.264,可以相信还会不断涌现更多的算法和应用。

责任编辑:gt

-

嵌入式

+关注

关注

5212文章

20746浏览量

338441 -

视频监控

+关注

关注

17文章

1740浏览量

68016 -

操作系统

+关注

关注

37文章

7452浏览量

129700

发布评论请先 登录

基于DSP芯片TMS320DM642的嵌入式无线视频监控系统

基于TMS320DM642的CCD图像采集系统设计

基于TMS320DM642 DSP芯片实现多功能视频处理系统的设计

TMS320DM642视频图像处理双路应用主板

怎么实现基于TMS320DM642视频采集驱动开发?

怎么实现基于TMS320 DM642的多路视频处理系统设计?

TMS320DM642 pdf datasheet

基于TI TMS320DM642平台的H.324可视电话设计

基于TMS320DM642的视频采集卡设计

基于TMS320DM642的网络摄像机的设计

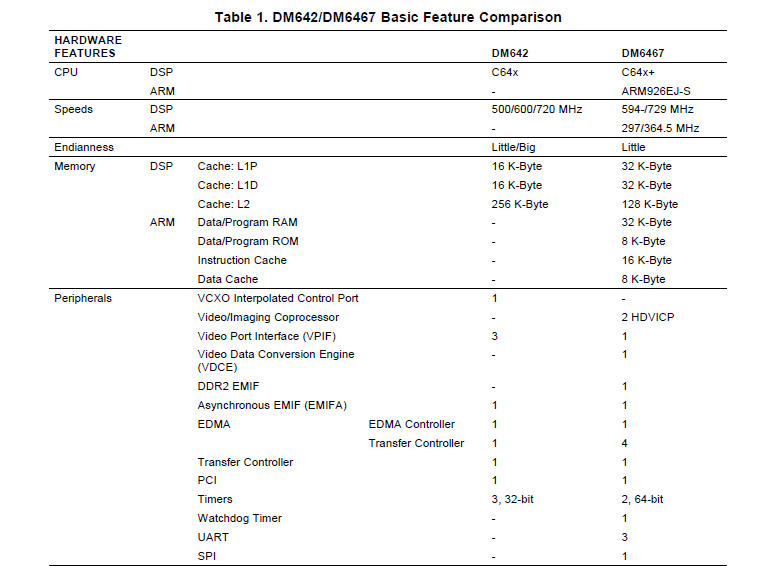

如何从进行TMS320DM642到TMS320DM6467的迁移

基于TMS320DM642视频采集驱动开发

基于TMS320DM642的多路视频采集处理板卡的硬件设计与实现

从TMS320DM642迁移至TMS320DM648/DM6437

基于TMS320DM642多媒体芯片实现视频监控系统的应用方案

基于TMS320DM642多媒体芯片实现视频监控系统的应用方案

评论