从智能电视、平板电脑、蓝光光盘播放器到数码摄像机,如今几乎每一种消费电子设备中都已经嵌入了各种音频处理功能。这些设备必须能够支持许多不同的多通道、高清晰的音频格式,以用于接收广播、文件播放、网络流媒体以及录音功能。为这些应用开发系统级芯片(SoC)的工程师,需要依此来搭建其系统架构,以便使音频处理以最高效的方式实现。

卸载到高效的音频处理器

目前,将音频处理从系统中的主处理器上卸载到更高效的音频处理器已经是很常见的做法。像音频编码、解码与后处理这样的任务,可以用专门为此而设计的处理器更高效地来处理。当音频功能从主处理器上被卸载下来后,我们通常可以看到功耗降低了80%。例如将MPEG-2 Audio Layer III或MP3解码功能,从一个电源优化的、带有NEON 扩展(3.13mW/10MHz)的ARM Cortex-A9双核处理器卸载到一个DesignWare ARC AS211SFX处理器(0.27mW/7MHz)上时,结果是功率消耗降低了约3mW。更精确地说,在一个使用了TSMC 40G工艺的ARM Cortex-A9和NEON上进行MP3解码,每个核将消耗0.3125mW/MHz,然而ARC AS211SFX却仅消耗0.0735mW/MHz。

然而,在诸如数字电视、机顶盒和蓝光光盘播放器等绝大多数消费电子设备中,多种音频解码与编码任务必须同时进行。其它的任务还包括在平板电脑及其它便携设备上用于虚拟环绕声效的音频强化(后处理)软件。这意味着,对于需要多通道的多音频流及高清音频的应用场景,MP3解码的总处理器负载不再仅仅是10MHz,而是可能要高达250MHz甚至更多,因而全部的总功耗降低可高达250×(0.3125-0.0735)mW/MHz=60mW!

图1:通过将音频任务卸载到一个高效率的音频处理器来优化设计。

内存延迟对音频处理器的性能影响

通常,音频处理器拥有为音频处理而定制的硬件架构,它不但降低了功耗,而且还减少了整体的芯片成本。Synopsys的32位DesignWare ARC音频处理器甚至为更好的SoC性能做了进一步优化。在当今的SoC中,DDR系统存储器是一种共享的资源,例如用于音频、视频、图形及程序代码。因此,为了确保留有足够的带宽可用,增加了存储器延迟。虽然这些延迟过去通常是顺序延迟50-100个周期,而在许多新设计中我们现在可看到延迟将高达200-300个周期。于是,任何处理器都将需要更多的“周期”(MHz)来执行某项任务;但是ARC音频处理器凭借其XY存储器架构,与业界其它处理器相比,存储器延迟对其性能有较小的影响。该ARC XY存储器架构使实现了大型音频数据单元的并行获取和处理。由于ARC音频处理器知道数据在存储器中所处的精确位置,因此它与基于缓存的设计相比,可以更高效地处理数据,例如,当数据单元“X0Y0”还在被处理时,“X1Y1”数据单元已经在从存储器中被转移的过程中了。这种XY架构的优势早在存储器延迟超出50个周期时就已经得以见到。

一个典型的实例就是经常被引用的蓝光光盘DTS音频使用案例。表1显示了100个周期的存储延迟对各家领先供应商的处理器性能的影响。显然,存储器延迟对ARC处理器的影响相比于其它处理器的影响较小。尽管这个例子显示了100个周期存储延迟对性能的影响,但ARC音频处理器在更大的系统延迟(200-300个周期)情况下,将同样展示比其它处理器更多的优势:抑或是能够应用更低的时钟频率(可带来更低的功耗和更小的片芯占用面积),或者是可留出更多的处理周期(为其它任务留出更多“动态余量”)。

表1:Synopsys ARC音频处理器的存储器延迟容忍。

MPEG-4 AAC-LC和MPEG-4 HE-AAC音频标准

许多消费电子设备中所用的一种音频压缩方案是先进的音频编码(Advanced Audio Coding,简称为AAC),它是一种有“损失”的压缩与编码方案。低复杂度的AAC或称为AAC-LC被用于低码率的应用,如互联网流媒体;它在1997年被放入MPEG-2标准成为其音频子集(MPEG-2 AAC-LC)。在1999年被定义的MPEG-4 AAC-LC还包括了知觉噪声代替(Perceptual Noise Substitution,PNS)。由Coding Technologies公司创造的谱带复制(Spectral Band Replication,SBR)在2003年被加入MPEG-4标准中。现在被称为HE-AAC v1,也称aacPlus v1、eAAC+、AAC++或者加强型AAC+。在2004年,一种参数立体声(PS)编码工具被加入该标准中,从那时起开始称之为MPEG-4 HE-AAC v2(或aacPlus v2)。

我们通常看到AAC-LC和aacPlus v2(HE-AAC v2)被用于诸如数字无线电、广播、互联网流媒体、高品质音频录音等应用中,被用在诸如数字电视、机顶盒、数码摄像机、平板电脑及媒体播放器等消费电子设备中。因此,音频处理器需要为这些标准提供顶级解决方案。

Synopsys提供最优化的实现方案

Synopsys的DesignWare ARC MPEG-4 AAC-LC和aacPlus v2编码器拥有多通道编码功能,可为环绕声应用提供多达7.1(8个)音频通道。

ARC音频软件编解码器中所提供的、效率提升的可选编码方法包括混合立体声编码(Joint Stereo Encoding)、随机噪声代替(TNS)、PNS、增强立体声(IS)、SBR和PS,可支持音频数据交换格式(ADIF)、音频数据传输流(ADTS),同时还提供低开销音频流(LOAS)容器组件。

Synopsys的音频软件工程团队为按照所需周期(MHz)数量来计的最低处理器负载设计了音频算法的实现。Synopsys还针对尽可能小的存储器占用片芯面积进行了优化(表2)。ROM用来存储程序代码,RAM用来存储程序执行过程中的音频数据。更小的ROM和RAM面积为SoC集成工程师带来了更低的芯片面积成本。

表2:Synopsys提供了最优的AAC-LC编码解决方案

SoundWave音频子系统内置软件栈

Synopsys的DesignWare SoundWave音频子系统为SoC设计师提供了一套完整的、经预先验证的音频子系统,包括可集成到SoC设计中的硬件、软件和原型。已经SoC就绪的音频解决方案减少了SoC设计与集成工作量,缩短了产品上市时间。

除了单核或双核音频处理器,可配置的SoundWave硬件还包括数字的I2S和S/PDIF、以及可选的模拟音频接口。然而,由于大多数的SoC设计工作量都耗费在了软件集成上,SoundWave音频子系统还包含了一个媒体流框架(MSF)。MSF可以使开发者容易地在其应用集成和结合所有的音频软件功能,包括数据交换、解码/编码以及后处理单元。

系统集成商使用SoundWave GStreamer插件可以容易地将一切可提供的音频功能嵌入到他们的应用软件中。此软件插件是一个应用程序界面(API),包含了在音频子系统中所有可提供的功能。该插件处理了在子系统和主处理器之间的所有通讯,提供了一种将所有音频功能集成到主处理器上运行的应用软件的即插即用地集成。

图2:媒体流框架能够被快速地集成到应用软件中

小结

软件在支撑SoC设计团队为消费性音频产品提供高品质音频解决方案时,扮演着越来越重要的角色。无论是从软件的角度还是从硬件的角度来看,音频处理IP供应商需要提供优化的解决方案。

Synopsys已经投入巨资来为消费电子SoC市场创造一种差异化的音频处理器IP解决方案。一个可提供AAC-LC和aacPlus v2编解码器的、丰富的优化音频软件产品组合,使设计师可实现降低音频应用的功耗及缩小芯片面积。通过将软件IP打包作为完整的硬件与软件解决方案的一部分,我们使设计团队能够以更低的风险和更高的生产效率,将各种先进的音频功能集成到他们的SoC当中,应用在诸如数字电视、机顶盒、平板电脑和数码摄像机等产品中。

责任编辑:gt

-

处理器

+关注

关注

68文章

19295浏览量

230001 -

摄像机

+关注

关注

3文章

1603浏览量

60089 -

平板电脑

+关注

关注

4文章

2016浏览量

77807

发布评论请先 登录

相关推荐

新思猛攻高阶嵌入式应用 ARC处理器新IP发功

ARC处理器:嵌入式新利器 性能功耗完美体

新思科技全新ARC处理器可加速符合ISO 26262标准软件开发

新思科技重磅发布全新RISC-V处理器系列,进一步扩大ARC处理器IP组合

Synopsys公司为下一代嵌入式数据和信号处理系统推出DesignWare ARC HS处理器

Synopsys扩展了安全关键型汽车应用的ARC处理器资产组合,增加了DSP和缓存支持

ARC EM处理器加快工业物联网超低功耗无线模块的实现

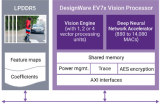

新思科技推出全新ARC EV7x嵌入式视觉处理器系列

新思科技推出全新ARC处理器,采用超标量ARCv3指令集架构

新思科技DSP增强型ARC EM和HS处理器支持谷歌软件应用

基于新思科技IP的DSP增强型DesignWare ARC EM处理器实现差异化功能

新思科技业内首个符合ISO 26262的ASIL D级处理器IP核面世

新思ARC功能安全处理器

新思科技DesignWare ARC EV系列处理器IP实现超分辨率

DesignWare ARC AS211SFX处理器提供最优化的实现方案

DesignWare ARC AS211SFX处理器提供最优化的实现方案

评论