继年前介绍的时序逻辑电路之时钟分频后,今天我们来介绍第7讲:流水灯。

流水灯,有时候也叫跑马灯,是一个简单、有趣又经典的实验,基本所有单片机的玩家们在初期学习的阶段都做过。本次我们也来介绍一下如何通过小脚丫FPGA实现一个流水灯。

流水灯就是让一连串的灯在一定时间内先后点亮并循环往复,所以其中的关键要领就在于控制每两个相邻LED亮灭的时间差,以及所有LED灯完成一组亮灭动作后的循环。很久都没有用过小脚丫的朋友可以再回顾一下,这上面有8个LED灯,且低电平点亮。

实现流水灯的方法绝不止一种,在这里我们采用模块化的设计思路,因为模块化设计对于之后构建大型电路系统非常有帮助,并且我们还可以借机温习一下以前学过的内容。

现在我们的目标是每过1秒后点亮下一个LED灯并且熄灭当前灯,且在第8个灯熄灭之后循环整个流程,该如何设计整个模块?我们先上图后解释。

毫无疑问,第一步需要做的就是通过分频来生成一个周期为1秒的时钟信号,不了解时钟分频童鞋可以读一下本系列的第6篇内容。

有了一个1秒钟嘀嗒一次的时钟后,我们还要考虑到循环问题,因为在第8个LED灯熄灭之后还需要再返回到第1个。那么这个时候我们就需要一个计数器,它的作用就是数羊,一只,两只…。..数到第八只后重头再来。数8只羊需要一个3位宽的变量(23=8)。

最后,由于我们是要依次点亮,也就是说8位的输出中每次只有1位是低电平,其余均为高电平(小脚丫LED灯为低电平点亮)。这个特性正好对应了我们之前学过的3-8译码器。

现在我们再来捋一遍。首先,通过分频在小脚丫上生成一个周期为1秒的慢速时钟信号,这个时钟信号传送到计数器之中;这个计数器是3位宽的,因此最多可以计八次慢速时钟的嘀嗒,并且计数每增加1时,都对应着3-8译码器的下一种输出,也就对应着流水灯的下一个状态。

现在我们上代码:

module runningled (clk,led); input clk,rst; output[7:0] led; reg [2:0] cnt ; //定义了一个3位的计数器,输出可以作为3-8译码器的输入 wire clk1hz; //定义一个中间变量,表示分频得到的时钟,用作计数器的触发 //例化分频模块,产生一个1Hz时钟信号 divide #(.WIDTH(24),.N(12000000)) u2 ( //除数为12,000,000,因此频率为1Hz .clk(clk), .rst_n(rst), .clkout(clk1hz) ); //生成计数器,上沿触发并循环计数 always@(posedge clk1hz) cnt 《=《 span=“”》 cnt +1; // 达到位宽上限后可自动溢出清零 //例化3-8译码器模块 decode38 u1 ( .X(cnt), //例化的输入端口连接到cnt,输出端口连接到led .D(led) );endmodule

在第四篇讲译码器的文章里,我们介绍过,如果需要调用/例化子模块时,需要将各子模块与大模块放入同一个工程文件下进行编译。最后我们再来对小脚丫进行管脚配置并烧录就可以了。

对应变量小脚丫管脚FPGA管脚

clkClockJ5

led [0]LED1N15

led [1]LED2N14

led [2]LED3M14

led [3]LED4M12

led [4]LED5L12

led [5]LED6K12

led [6]LED7L11

led [7]LED8K11

如果大家成功地在小脚丫上实现了流水灯的程序,还可以自己玩一个有意思的实验:比如,你可以通过修改程序来提高流水灯的刷新频率,然后看看LED灯的刷新率为多少时你的肉眼无法分别。同时再打开手机的摄像头,也以同样的方法试验一番。结合到你观察的现象,可以自己琢磨并思考一下,说不定能挖掘出更多的知识。

备注一些大伙都知道的常识:我国交流电工频为50Hz,电脑常用显示器的刷新率有60,75和144赫兹。华为Mate30刷新频率为90赫兹,苹果6-12的刷新频率为60赫兹。

编辑:lyn

-

FPGA

+关注

关注

1664文章

22502浏览量

639087 -

单片机

+关注

关注

6078文章

45576浏览量

673497 -

代码

+关注

关注

30文章

4976浏览量

74373

原文标题:基于FPGA的数字电路实验7:流水灯的实现

文章出处:【微信号:xiaojiaoyafpga,微信公众号:电子森林】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用FPGA控制上千颗RGB LED流水灯

FPGA在音频产品上的应用案例

嵌入式与FPGA的区别

蜂鸟E203在黑金XC7A200T型FPGA上点亮LED并实现流水灯

掌握数字设计基础:迈向芯片设计的第一步

高速数字电路设计与安装技巧

【沁恒CH585开发板免费试用体验】GPIO 流水灯

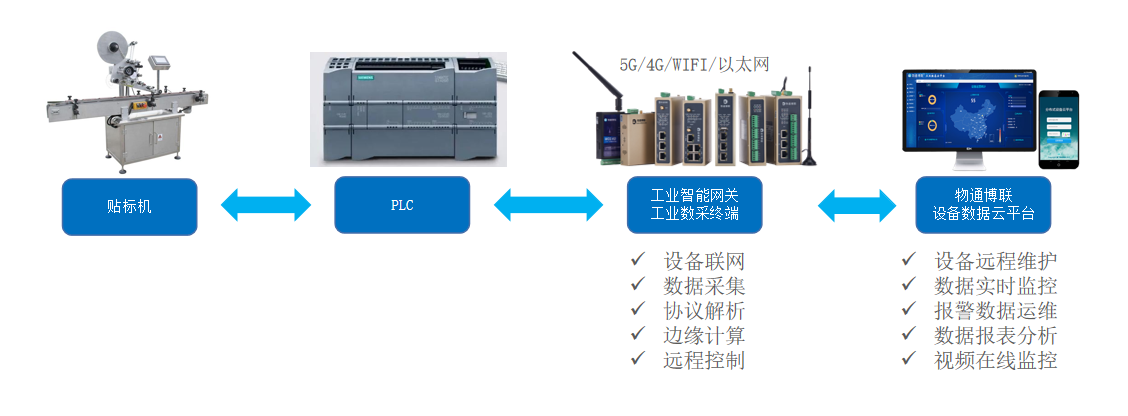

自动化开装封码流水线数据采集解决方案

详解基于FPGA的数字电路对流水灯的实验

详解基于FPGA的数字电路对流水灯的实验

评论