对毫米波雷达回波信号的处理一般可以分为数字采样和信号处理两部分,其中数字采样的精度和性能将直接影响到信号处理得输出结果,因此,越来越多的雷达系统需要高带宽、高量化精度的A/D转换,毫米波雷达也不例外,ADC是对雷达回波进行数字化处理得前端,是信号处理与外界信息相连的桥梁,其性能也是影响和制约雷达整体性能的关键因素之一。

由于雷达信号频带宽,动态范围大,数据处理实时性要求高,所以必须选择高速A/D变换器,而AD9481频带宽,噪声低,转换速度快,尤其是差分信号动态性能突出,同时采用A、B两路输出的结构,提供有2个彼此反相的时钟(DCO+和DCO-),以便后续设备锁存数据。因此,其数据输出速率降低了一倍,从而降低了对存储器的读写速度要求,由此可见,选用此芯片进行采样系统的设计有着重要的现实意义。

系统结构和工作原理

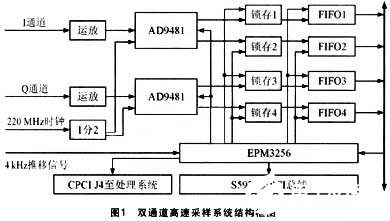

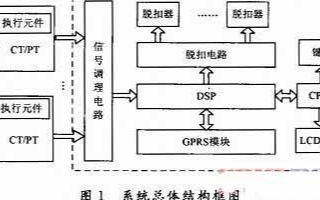

本系统是基于某毫米波测量雷达,该雷达接收机可输出正交的I、Q双通道零中频、200MHz带宽的模拟信号,以及220MHz采样时钟信号和推移信号。整个数字采样系统由AD9481芯片、CPLD和CPCI总线构成,其中多路数据的传输采用FIFO缓存,双通道高速采样的难度在于要在较高采样频率基础上,应保持I、 Q两个通道的同步,当两个通道的数据采样不同步时,数据采样系统将严重影响后端雷达信号的处理精度,甚至影响雷达信号处理得正确性,综合以上要求,本采样系统主要依靠CPLD来控制采样时序,这样可以方便硬件系统的调试,图1给出了双通道雷达回波信号采样系统的结构框图。

雷达I、Q通道回波信号输入采样系统后,先经过运放AD8138变为采样芯片AD9481需要的差分输入信号,220MHz的采样时钟经过2分频后分别输入两个AD9481,AD9481对输入信号进行AD变换后,即以110MHz时钟分两路输出相反的时钟信号,并在CPLD控制下经过锁存写入两路 FIFO。由于每路输出数据是8bit,因此,对于I、Q通道的采样数据在其从FIFO输出后应经过CPLD将两路数据合并成16bit,然后再通过 CPCI总线的J4接口输入到雷达信号处理系统,同时通过S5933输入到PCI总线,其中向PCI总线的传输主要是为了调试过程中的数据控制。

双通道高速采样同步时序控制设计

图2 所示是AD9481的工作时序,从图中可以看出,其DCO时钟是互相反相的,DCO-时钟对应的数据输出通道是A通道,DCO+时钟对应的通道是B通道,对于采集时钟信号来说,B通道的数据要比A通道的数据晚一个周期,而对于输出的DCO时钟来说,B通道的数据要比A通道晚半个周期。由于数据是交叉式输出的,其顺序不会改变,因此,对于双通道数字采样的同步问题,可以由后端不同通道的FIFO缓存来实现数据的排序。

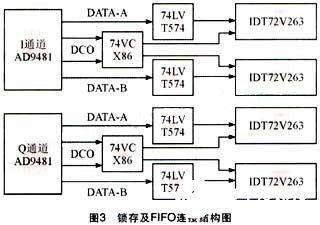

本系统中的两个AD9481分4个通道输出数据,为了配合CPLD控制FIFO来实现输出数据的同步,输出的8bit数据应先经过锁存器 74LVT574,然后进入各自通道的FIFO来实现存储,AD9481的输出时钟DCO可经过异或门74VCX86加到各自通道的FIFO上,其连接结构如图3所示。

对于每一路采样系统,将DCO-和CPLD输出的锁存有效信号相异或,便可得到输出A通道锁存74LVT574的输入时钟,而将DCO+和CPLD 输出的锁存有效信号相异或,就可以得到输出B通道锁存74LVT574的输入时钟,将DCO-和CPLD输出的FIFO有效信号相异或,即可得到输出A通道FIFO的写入时钟,DCO+和CPLD输出的FIFO有效信号相异或,就会得到输出B通道FIFO的写入时钟,采用这样的设计,只需更改CPLD输出的有效信号就可以控制每一路时钟和数据的传输状态,并可充分利用CPLD便于更改程序的优势来控制两路采集的同步,从而方便设计过程中的调试。

整个双通道数字采样的逻辑控制可由一片Altera公司生产的MAX3000系列CPLD完成,其型号为EPM3256-10,速度为10ns。

事实上,系统的逻辑控制主要用于完成以下功能:

◆ 完成S5933的启动及配置;

◆ 通过控制AD9481的DS信号,来实现对采集过程的控制;

◆ 通过控制4个通道中的锁存和异或门,来实现对采集过程中单通道内部和双通道数据之间的同步控制;

◆ 通过控制FIFO的写使能和写时钟,实现对FIFO状态及传输数据的控制;

◆ 在4个FIFO的输出端完成双通道中8bit数据合成16bit数据的工作;

◆ 在4个FIFO的输出端,通过对FIFO读时钟和读使能的控制,来在I、Q各自通道内完成A、B端口FIFO数据的交叉读取,并保证输出数据的正确顺序;

◆ 完成合成16bit数据向J4接口或CPCI总线的传输;

◆ 由雷达接收机发出4KHz的推移信号,按期对AD9481进行使能并清空4个FIFO;

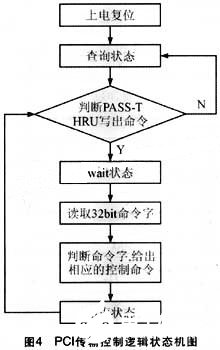

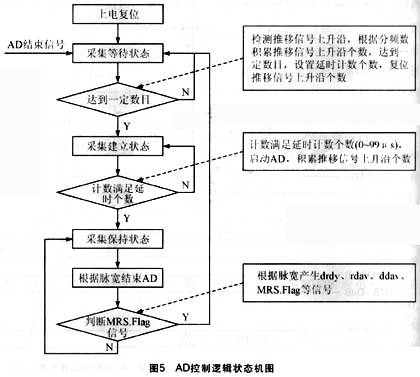

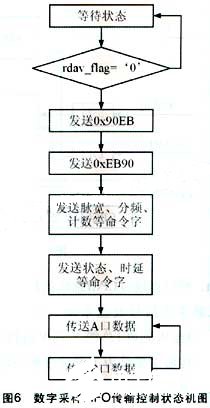

CPLD的控制逻辑可由状态机实现,其逻辑结构如图4、图5和图6所示。

在AD控制的逻辑状态机中,rday、ddav通过使能可产生rclk和dclk信号,rclk和dclk两个信号均为20MHz,相差为360 度,且通过使能产生的FIFO使能信号,为低电平有效,保持时间为50ns五,也就是频率为20MHz的信号,A口FIFO与B口FIFO的读使能信号完全反相,但读时钟相同,实际上,dclk比rclk晚一个周期。

在数字采样的FIFO传输时,为了后端信号处理得方便,可在每帧数据上附加帧头:“0x90EB EB90”,这样可以明确表明帧的起始位置,防止错误数据影响后端信号的处理流程,这些信号的脉宽、分频、计数命令和状态、时延命令都是16bit的,均可在两个时钟周期内传输完毕,并可用于表明数据传输和雷达工作的状态。

结束语

在系统设计完成后,可首先采用正弦曲线拟合法对ADC的动态性能进行测试,测试结果和理想的正弦曲线相比,其误差在较大点数的采样后趋于平稳,误差为10 -4V级别,可以认为,采集系统的精度是很高的。此后,又采用FFT方法对ADC系统的频域性能进行了测试,测试结果表明,双通道数字采样系统具有较好的信噪比和有效位数,此外,在双通道数字采样的测试中笔者还对雷达的发射波形进行了采样,雷达发射波频率从100MHz逐渐降低到0MHz,然后从 0MHz再上升到100MHz,采样结果表明,本系统的数字采样具有良好的采样性能。

责任编辑:gt

-

芯片

+关注

关注

456文章

50984浏览量

425110 -

cpld

+关注

关注

32文章

1248浏览量

169462 -

毫米波

+关注

关注

21文章

1925浏览量

64899

发布评论请先 登录

相关推荐

基于DSP和CPLD EPM3128芯片实现智能控制器的电路设计

使用两片AD2S1210能否实现双通道感应同步器的位置采样转换?

AIC3256采用I2S模式时,6通道音频采集的传输时序将是怎么样的呢?

请教CPLD下载

请问使用两片AD2S1210能否实现双通道感应同步器采样?

keysight E4419B EPM 系列双通道功率计产品优势

如何利用FET5718核心板控制超高速双通道ADC进行数据采集?

基于EPM7128SLC84实现的AD574A采样控制器

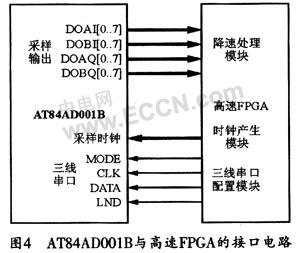

高速双通道采样芯片AT84AD001B及其应用

解读ADC采样芯片(EV10AQ190A)的采样(工作)模式(双通道模式)

ADS981x 18位2MSPS/通道双通道同步采样ADC数据表

基于EPM3256-10 CPLD芯片实现双通道高速采样同步时序控制设计

基于EPM3256-10 CPLD芯片实现双通道高速采样同步时序控制设计

评论