引言:本文我们介绍区域时钟资源。区域时钟网络是独立于全局时钟的时钟网络。不像全局时钟,一个区域时钟信号(BUFR)的跨度被限制在一个时钟区域,一个I/O时钟信号驱动一个单一的Bank。这些网络对于源同步接口设计特别有用。7系列器件中的I/O Bank与时钟区域的大小相同。为了理解区域时钟是如何工作的,理解区域时钟信号的信号路径是很重要的。7系列设备中的区域时钟资源和网络由以下路径和组件组成:

时钟输入I/O

I/O时钟缓冲器:BUFIO

区域时钟缓冲器:BUFR

区域时钟网络

多区域时钟缓冲器:BUFMR/BUFMRCE

水平时钟缓冲器:BUFH/BUFHCE

高性能时钟

1.时钟输入I/O

每个时钟区域在每个I/O Bank有四个专用时钟I/O输入管脚。当用作时钟输入时,可以驱动BUFIO、BUFMR和BUFR。每个I/O列都支持区域时钟缓冲区(BUFR)。每个器件中有两个I/O列。当时钟管脚不用作时钟输入时,可以作为普通I/O使用。

当用作单端时钟引脚时,则如全局时钟缓冲器中所述,必须使用引脚对的P侧,因为时钟直接连接仅存在于该引脚上。

2.I/O时钟缓冲器:BUFIO

BUFIO在I/O Bank中驱动一个专用的时钟网络,独立于全局时钟资源。因此,BUFIOs非常适合于源同步数据捕获(发送/接收器时钟分布)。BUFIO由位于同一组的具有时钟功能的I/O、来自MMCM的HPC或相同和相邻区域的BUFMR驱动。在一个时钟区域中,每个Bank有四个BUFIO。每个BUFIO可以驱动同一区域/Bank中的单个I/O时钟网络。BUFIOs不能驱动逻辑资源(CLB、块RAM、DSP等),因为I/O时钟网络只到达同一个Bank/时钟区域中的I/O列。

2.1 BUFIO原句

BUFIO原句示意图如图1所示。输入和输出存在相位延迟。

图1、BUFIO原句

2.2 BUFIO使用模式

BUFIO使用时钟输入I/O驱动I/O逻辑,如图2所示。这种实现在源同步应用中经常使用,在这些应用中,前向时钟用于捕获传入数据。

图2、BUFIO驱动I/O逻辑

图2中,可以看到BUFIO只能驱动I/O逻辑资源,不能驱动FPGA逻辑资源。

3.区域时钟缓冲器BUFR

BUFRs将时钟信号驱动到时钟区域内的专用时钟网络,独立于全局时钟树。每个BUFR可以驱动它所在区域的四个区域时钟网络。与BUFIOs不同,BUFRs可以驱动I/O逻辑和逻辑资源(CLB、块RAM等)。BUFRs可以由具有时钟功能的管脚、本地互连和MMCMs HPC(CLKOUT0到CLKOUT3)或相同和相邻区域中的BUFMR驱动。此外,BUFR能够产生分频时钟输出。分频值是1到8之间的整数。BUFRs是理想的源同步应用需要跨时钟域或串并转换。

每个I/O列都支持区域时钟缓冲区。BUFRs还可以直接驱动MMCM时钟输入和BUFG。

3.1 BUFR原句

BUFR原句如图3所示。

图3、BUFR原句示意图BUFR是时钟输入或输出缓冲器,且可以对输入时钟频率分频。7系列FPGA BUFRs可以直接驱动MMCM时钟输入和BUFGs。

在图3中可以,看到,BUFR原句附加使能信号CE和清零CLR信号,该控制信号为异步控制信号。当全局复位信号(GSR)为高时,BUFR无论CE处于何逻辑,BUFR均处于复位,直到GSR复位信号为低电平。

3.2 BUFR使用模式

BUFR分频功能通过其属性进行设置。

图4、BUFR Verilog原句BUFRs是需要跨时钟域或串并转换的源同步应用的理想选择。与BUFIOs不同,BUFRs能够对除IOB之外的FPGA中的逻辑资源进行时钟驱动。图5是BUFR设计示例。

图5、BUFR设计示例

4.区域时钟网络

除全局时钟树和网络外,7系列器件还包含区域时钟树和网络。区域时钟树也设计用于低偏斜和低功耗操作。未使用分支断开。当使用所有逻辑资源时,区域时钟树还管理加载/扇出。

区域时钟网络不会在整个7系列设备中传输。相反,它们仅限于一个时钟区域。一个时钟区域包含四个独立的区域时钟网络。要访问区域时钟网络,必须实例化BUFRs

5.多区域时钟缓冲器:BUFMR/BUFMRCE

BUFMR取代了以前Virtex架构中对BUFR和BUFIO的多区域/Bank支持。每个Bank中有两个BUFMR,每个缓冲区可以由同一个Bank中的一个特定MRCC驱动。MRCC管脚在管脚对的P管脚和N管脚的管脚名称中都用MRCC标记(IO_L12P_T1_MRCC_12 or IO_L12N_T1_MRCC_12)。BUFMR驱动同一地区的BUFIO和/或BUFRs/Bank和地区/以上和以下Bank。BUFR和BUFIO原语必须单独实例化。当使用BUFR分频(不在旁路中)时,必须通过插入CE引脚的来禁用BUFMR,必须重置BUFR(通过插入CLR来清除),然后使能CE信号。此顺序确保所有BUFR输出时钟相位对齐。如果不使用BUFRs中的分频功能,那么电路拓扑只需要使用BUFMR。BUFMR输入包括:

MRCC管脚

同一时钟区域的GT收发器时钟

5.1 BUFMR/BUFMRCE原句

BUFMR/BUFMRCE原句如图6所示。

图6、BUFMR/BUFMRCE原句

图7、BUFMR例化语句

图8、BUFMRCE例化语句要将BUFMR或BUFMRCE与BUFIOs一起使用,接口引脚必须在三个匹配Bank范围内。同样,如果与BUFRs一起使用,则逻辑必须最多适合三个区域(如果使用三个BUFRs)。如果内存接口放在BUFRs/BUFIOs所在的同一个Bank或区域中,那么从BUFMR到该Bank或区域中的那些BUFHs/BUFIOs的连接可能会受到限制。图9显示了BUFMRCE的拓扑结构。

CE_TYPE属性应始终设置为SYNC,以确保时钟输出无故障。如果BUFMRCE的时钟输出停止(例如,通过取消CE),则必须在再次启用BUFMRCE后重置BUFR(CLR)。BUFMRCE上的CE的主要目的是为BUFRs和BUFIOs提供同步的、相位对齐的时钟。

6.水平时钟缓冲器:BUFH/BUFHCE

水平时钟缓冲器(BUFH)在单个区域驱动水平全局时钟骨干(图2-26)。每个地区有12个BUFH可用。每个BUFH都有一个时钟启用引脚(CE),允许动态关闭时钟。BUFHs可通过以下方式驱动:

相同区域MMCM/PLL输出

BUFG输出

相同或者水平相邻时钟GT输出时钟

本地内部互联

来自相同水平相邻的区域或者Bank的左侧或者右侧I/O Bank的时钟输入

图10、BUFH和BUFHCE原句

图11、BUFHCE例化语句如图12所示,要使用BUFH,逻辑必须适合水平相邻的两个区域(左和右)。时钟使能引脚可以完全关闭时钟,从而实现潜在的节能。与驱动两个相邻区域的BUFG相比,BUFH的功耗和抖动更低。

图12、水平时钟缓冲示例

7.高性能时钟

7系列FPGA每个I/O Bank包含四个HPC。这些时钟与I/O中的BUFIOs和BUFRs直接短差分连接。因此,这些时钟表现出非常低的抖动和最小的占空比失真。在I/O列中,HPC连接到BUFIO/BUFRs并驱动I/O逻辑。由于CMT列位于I/O列旁边,HPC直接驱动器进入I/O列旁边的I/O Bank CMT.HPCs由MMCM的CLKOUT[3:0]驱动(仅限)。

7.1时钟门控节能

7系列FPGA时钟体系结构提供了一种实现时钟选通的简单方法,用于关闭部分设计。大多数设计包含几个未使用的BUFGCE或BUFHCE资源。时钟可以驱动BUFGCE或BUFHCE输入,BUFGCE输出可以驱动不同的逻辑区域,BUFHCE可以驱动单个区域。例如,如果所有需要始终运行的逻辑都被限制在几个时钟区域,那么BUFGCE输出可以驱动这些区域。或者,如果BUFHCE驱动单个区域中的接口,则该接口可能在非操作期间关闭。切换BUFGCE或BUFHCE的enable提供了一种简单的方法来停止可用于节能的逻辑区域中的所有动态功耗。

原文标题:Xilinx 7系列FPGA架构之时钟资源(四)

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1629文章

21735浏览量

603201 -

Xilinx

+关注

关注

71文章

2167浏览量

121368

原文标题:Xilinx 7系列FPGA架构之时钟资源(四)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

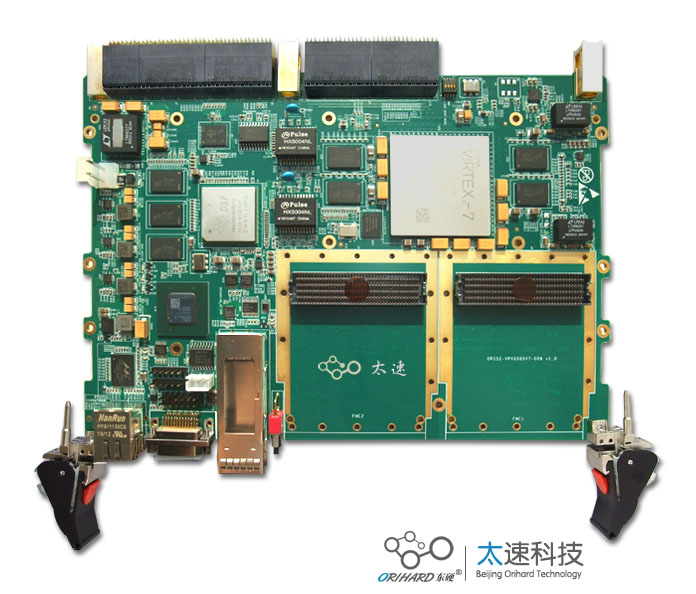

【米尔-Xilinx XC7A100T FPGA开发板试用】测试一

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信号处理卡

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

Xilinx 7系列FPGA PCB设计指导

FPGA | Xilinx ISE14.7 LVDS应用

FPGA核心板 Xilinx Artix-7系列XC7A100T开发平台,米尔FPGA工业开发板

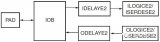

Xilinx SelectIO资源内部的IDELAYE2应用介绍

Xilinx fpga芯片系列有哪些

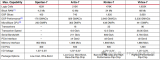

UltraScale系列与7系列FPGA的差异

AMD Xilinx 7系列FPGA的Multiboot多bit配置

Xilinx 7系列FPGA架构的区域时钟资源介绍

Xilinx 7系列FPGA架构的区域时钟资源介绍

评论