目前将摄像机拍摄的图像传送到计算机中进行播放、处理主要有两种方式:一是通过图像采集卡;二是利用摄像机自带的USB接口。第一种方式虽然可以保证图像采集的实时性,但不能脱离计算机单独工作,应用领域有局限性;后一种方式在图像传输实时性和图像播放质量上又不尽人意。随着网络技术的发展,使网络接入技术直接嵌入到摄像机中成为可能。本文介绍一种基于DSP芯片和嵌入式微控制器的网络数字摄像系统。该系统内部集成了图像传感芯片和数字图像处理芯片,不需要借助计算机,直接连接到互联网上(见图1),向互联网上的计算机传输高质量的实时视频图像,根据网络通信状况和计算机的命令改变传输图像的分辨率和帧率等指标。该系统硬件集成度高、图像传输实时性好、操作简单、控制灵活。

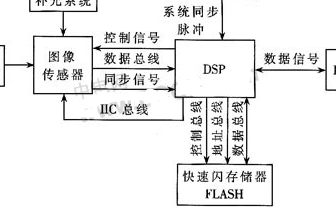

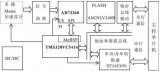

该系统包括两大部分:图像处理模块和NetMCU模块。系统框图见图2。由图像处理模块负责对图像进行采集和压缩,先将模拟图像信号转变成YUV格式的数字信号,然后由DSP芯片按照JPEG标准进行图像压缩编码。Ne tMCU模块将接收到的压缩图像数据按TCP/IP协议打包,发送至互联网的计算机上,并接收计算机传来的控制命令,对系统进行配置。以下分别介绍各个模块的工作原理和软件设计方法。

1 图像处理模块

1.1 芯片介绍

图像采集芯片采用OmniVision公司的CMOS彩色图像传感器OV6620。在它内部集成了一个356×292的彩色图像阵列。该图像传感器能对所拍摄的图像进行预处理,包括自动曝光控制、自动白平衡调节、gamma校正、自动图像增强;并可通过与DSP芯片相连的串行通信接口,对传感器内部的92个寄存器的参数进行设置。

图像压缩芯片采用TI公司的TMS320VC5416定点运算数字信号处理器(DSP),其内部采用一种改进型的哈佛总线结构(一条程序总线,三条数据总线),数据总线宽度为16bit。分开的数据和指令空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上其高度优化的指令集,使得该芯片具有很高的运算速度,最高可达160MIPS。

VC5416芯片的外部程序存储空间为8M×16bits,外部数据存储空间为64K×16bits。在芯片内部还集成了128K×16bits片上存储器。该芯片具有多种片上外部设备单元,包括一个16位计时器,一个6通道DMA传输控制器,三个带缓冲器的串行通信接口(McBSP)和一个8/16位的主机通信接口(HPI8/16)。

1.2 功能介绍

图像处理模块主要负责模拟图像的采集、数字化、压缩等工作。首先,在系统加电运行后,由NetMCU模块对VC5416芯片复位,然后VC5416芯片运行固化在芯片内的BootLoader程序,将存储在外部程序存储器上的应用程序复制到内部存储器中,并开始运行应用程序。应用程序的任务主要有以下三个方面:

(1)通过VC5416芯片的1号串行通信接口(McBSP1)对OV6620的内部寄存器进行参数配置。主要参数包括:将输出图像分辨率设置为352×288,将输出图像帧的速率设置为25帧/秒,将数字图像的输出格式设置为YUV分量4:2:2格式。

(2)将OV6620芯片输出的图像数据利用JPEG算法进行数字图像压缩。在本设计中采用一种改进的JPEG算法[4]。将二维DCT变换分解成两次一维快速DCT变换。对8×8象素块的DCT变换,共需176次乘法和464次加法,比标准DCT算法的1024次乘法和896次加法在运算速度上有极大提高。

(3)VC5416芯片通过与NetMCU模块相连的0号串行通信接口(Mc BAP0),接收改变传输图像的分辨率、帧速、曝光时间等参数的命令,并及时调整OV6620芯片的内部寄存器参数。

OV6620芯片和VC5416芯片之间存在大量的数据传输,因此在系统中采用一片ALTERA公司的FPGA(FLEX10K20)芯片作为数据传输接口,代替VC5416芯片管理外部数据存储区。在FPGA芯片中集成了一个512×16bits的FIFO和一个存储控制器。通过OV6620芯片输出的图像象素移位脉冲和图像的行、场同步脉冲的控制,将原始图像数据存入FIFO中。由于JPEG图像压缩以8×8象素块基本运算单位,需要存储控制器将FIFO中以行顺序输入的原始图像数据进行存储地址调整,变换成按8×8像素块顺序存入外部数据存储区。同时,由于受VC5416芯片的外部数据存储区容量的限制,存储控制器将一帧原始图像数据分成上下两个半区,各占用一个64KB地址空间。当VC5416芯片读数据时,存储控制器会自动在这两个半区之间切换,使得DSP芯片能够处理一帧图像。

2 NetMCU模块

2.1 芯片介绍

本系统采用三星公司的S3C4510B芯片作为主控制器。芯片内部结构见图3。S3C4510B芯片集成了ARM公司的32位精简指令集处理器ARM7TDMI核。ARM7TDMI核采用冯•诺依曼体系结构,使用单-32位总线传送指令和数据,使用三级流水线操作以提高处理器执行速度。ARM7TDMI核可以使用两种指令集:一种是32位ARM指令集;一种是16位Thumb指令集。Thumb指令集是ARM指令集的子集,但它能提供比16位体系结构更高的性能、比32位体系结构更高的代码密度。因此,Thumb指令集使ARM7TDMI核非常适合有存储器宽度和代码密度限制的嵌入式场合。 S3C4510B芯片的存储空间最大可达16M×32bits(包括程序存储区、数据存储区和I/O设备区),它内部集成了一个存储控制器,具有自动刷新存储区数据和自动插入可编程等待周期的功能,可以支持多种类型的存储芯片(包括ROM、SRAM、FLASH和DRAM)。在芯片内部还集成有8K×8bits的指令/数据Cache,采用pseudo-LRU(Least Recently Used)算法,大大提高了芯片的性能。

由于S3C4510B芯片面向网络应用,因此在芯片内部集成了一个以太网控制器。该控制器工作于MAC层,完全兼容IEEE802.3协议标准。它能运行于10Mbps/100Mbps模式。该控制器包括一个接收/发送单元、一个流控制器、一个用于存放网络地址的内容可寻址存储单元和一系列命令/状态寄存器。

2.2 功能介绍

S3C4510B芯片作为系统的主控制芯片,负责控制嵌入式网络数字摄像系统的正常工作,包括将压缩后的图像数据按照TCPIP协议发送到互联网中的计算机上并接收计算机的命令修改系统工作参数等。

系统加电后,S3C4510B芯片自动从地址0x00处运行系统程序。系统程序首先初始化异常向量表,之后初始化1K×32bits的系统堆栈区,用于存放出现异常情况(中断)时的寄存器值。然后,系统程序设置系统正常工作时的各个存储区起始地址及存储区容量,将地址0x00000~0x7FFFF共512K×32bits范围作为程序存储区(ROM),用于存放系统程序和用户程序;将地址0x1000000~0x10FFFFF共1M×32bits作为程序/数据存储区(RAM),又将该段存储区分为用户程序段、用户堆栈段和用户数据段;将片内存储区地址映射到0x3FE0000~0x3FEFFFF;将特殊寄存器区地址映射到0x3FF0000~0x3FFFFFF。最后系统程序设置片内寄存器的值,初始化S3C4510BS3C4510B芯片的各个外部接口,包括异步串行通信接口(UART)、计时器、可编程I/O口、以太网控制器等。在系统初始化结束后,自动进入用户模式,执行用户程序。

在用户模式下,摄像系统作为网络视频服务器。根据用户程序设置的MAC地址和IP地址,接收来自互联网中计算机发出的请求信号。当系统收到请求信号后,用户程序立即在本地与计算机建立TCP连接。将待传输的一帧压缩图像数据首先按TCP协议封装成TCP数据报,然后交付给IP层子程序封装成IP数据报,最后由S3C4510B芯片内的MAC控制器将其拆分封装成帧并发送到目的计算机上。当有多个计算机用户发出请求信号时,用户程序会在数据存储区中设置一个用户列表,自动根据各个计算机的IP地址和建立连接时的端口号分别发送图像数据。图4显示了用户程序与一台计算机发送和接收TCP/IP数据报的流程图。目的计算机将接收到的TCP/IP数据报解封,恢复成JPEG压缩图像帧,再解压缩,完成视频图像流的接收和播放。

用户程序在发送数据帧的同时,会根据图像数据发送的速度及网络的拥塞情况,自动通过异步串行通信接口(UART0)向VC5416VC5416芯片发送控制信号,及时改变图像采集和压缩的速率。本系统在发送视频数据的同时,还能够接收来自计算机的控制命令。根据不同的控制命令,系统也可以完成对图像分辨率、图像帧速率等指标的调节。

本文介绍的网络数字摄像系统目前运行于评估板平台上,下一步将继续进行系统的集成和优化并最终实现产品化。由于该设计方案采用高性能的32位微控制器和多个通用可编程器件(FPGA和DSP),因此该系统能够支持VxWorks嵌入式实时操作系统和更为复杂的应用程序。而且软件和硬件设计只需稍加改进就能实现无线联网,使得数字摄像系统能在移动中传输实时图像。该网络数字摄像系统具有硬件集成度高、图像传输实时性好、操作简单、维护方便等优点。可以用于电视会议、电讯基站、智能楼宇、银行的保安监控以及交通违章和流量管理等。

责任编辑:gt

-

dsp

+关注

关注

554文章

8060浏览量

350860 -

芯片

+关注

关注

457文章

51345浏览量

428244 -

计算机

+关注

关注

19文章

7553浏览量

88798

发布评论请先 登录

相关推荐

基于TMS320VC5416芯片和OV7620实现水表盘字轮号码读取系统的设计

μClinux在S3C4510B上的移植

求助:哪位高手基于TMS320VC5416的语音编码电路图

TMS320VC5416 pdf datasheet

基于S3C4510B的应用系统设计与调试

s3c4510b中文手册,s3c4510b用户手册

TMS320VC5416-160,pdf(Fixed-Poi

TMS320VC5416的多路加速采集系统设计方法

TMS320VC5416 数字信号处理器

基于TMS320VC5416和S3C4510B芯片实现网络数字摄像系统的设计

基于TMS320VC5416和S3C4510B芯片实现网络数字摄像系统的设计

评论