一、 IRIG-B格式码的格式与规范

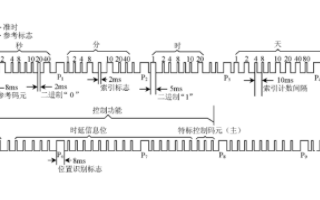

图1为B(DC)码示意图。它是每秒一帧的时间串码,每个码元宽度为10ms,一个时帧周期包括100个码元,为脉宽编码。码元的“准时”参考点是其脉冲前沿,时帧的参考标志由一个位置识别标志和相邻的参考码元组成,其宽度为8ms;每10个码元有一个位置识别标志:P1,P2,P3,…,P9,P0,它们均为8ms宽度;PR为帧参考点;二进制“1”和“0”的脉宽为5ms和2ms。

图1 B(DC)码示意图

一个时间格式帧从帧参考标志开始。因此连续两个8ms宽脉冲表明秒的开始,如果从第二个8ms开始对码元进行编码,分别为第0,1,2,…,99个码元。在B码时间格式中含有天、时、分、秒,时序为秒-分-时-天,所占信息位为秒7位、分7位、时6位、天10位,其位置在P0~P5之间。P6~P0包含其他控制信息。其中“秒”信息:第1,2,3,4,6,7,8码元;“分”信息:第10,11,12,13,15,16,17码元;“时”信息:第20,21,22,23,25,26,27码元;第5,14,24码元为索引标志,宽度为2ms。时、分、秒均用BCD码表示,低位在前,高位在后;个位在前,十位在后。

二、 B码解码接口卡设计方案

B码解码接口卡功能框图如图2所示。

图2 “B码解码接口卡”功能框图

对B码进行解码就是将B码中所包含的时、分、秒信息提取出来,转换成主计算机能够识别的形式,同时以秒的准时点为参考,生成毫秒信息,一同送入主计算机中。解码的关键在于检测B码中各个码元的高电平宽度,首先要检测连续两个8ms宽的码元出现的位置,然后再检测随后的30个码元脉冲宽度,以确定时、分、秒。这里不检测天的值,天可以直接在主计算机上设置。

图3 B码解码接口卡电路

检测高电平宽度:将B码送入单片机89C51的INT0端,在INT0引脚由低电平变为高电平时,启动单片机的内部定时器T0,开始计数;在INT0引脚由高变低时(即下降沿),触发INT0中断,读取计数器的值,脉冲宽度等于计数值乘以计数周期。

形成毫秒值:将1kHz信号接到单片机的INT1端,每毫秒产生一次中断。INT1中断处理程序完成毫秒计数,当计到1000ms时完成秒加1。

三、 电路设计

1 电路设计方案1

方案1中,输入输出模块由5片锁存器构成,接口控制简单,如图3所示。

来自时统设备的IRIG-B(DC)码,为RS422接口信号,经转换后变为TTL电平,送至单片机89C51的INT0端。单片机初始化设置中,定时器T0工作在模式1,采用内部时钟。当INT0引脚由低到高时,定时器T0开始计时;当INT0引脚由高变低时,触发INT0中断,执行中断服务程序,计算INT0引脚的高电平宽度。根据宽度对B码各脉冲进行解码,形成秒、分、时的BCD码,存入单片机的内部RAM中。同时,由频率源产生的12MHz的信号经分频器后,输出1kHz信号,送至单片机INT1引脚,使1ms产生一次INT1中断,执行INT1中断处理程序,对毫秒进行计数。毫秒计数到1000时,进行秒加1,毫秒初值在B码的准时点进行赋值。

单片机的P0口经锁存器Ⅰ输出地址线A0、A1,以控制两个并行接口芯片8255的输出端。单片机解码和计数输出的毫秒(2字节)、秒(1字节)、分(1字节)、时(1字节)BCD码,在单片机的写指令控制下,分五次送到两片8255的不同端口。各端口经锁存器Ⅱ“锁存器Ⅵ,将数据锁存。单片机送出一组时间码后,向主计算机发送中断。主计算机响应中断后,依次读取各锁存器的值,即为当前的时统时间。

图4 FIFO实现输入输出控制原理图

锁存器Ⅱ”Ⅵ的数据输出端直接挂在EISA(ISA)总线上,其片选信号CS1“CS5通过地址译码产生。

主计算机读时应能保证数据不处于变化中,因此,须将单片机的写信号WR经延时反向后,送到各锁存器的LE端,使数据被锁存。主计算机内设一存储单元,存放前一秒的数据。当前读取的数据如果比前一秒多1,则认为时间正确。

为避免板内程序死循环,在该板上设计了看门狗复位电路。在单片机板内程序中,每隔一定时间对P1.6口进行置1。计时器的最高位输出端接至单片机的Reset端。在正常情况下,P1.6口总能执行置1操作,不会对单片机复位;但若程序中有死循环,则P1.6口不被置1。当计时器计到最高位输出端为1时,就会对单片机复位。看门狗复位电路采用14位二进制计数器4060,并具备上电复位和手动复位的功能,其振荡周期由外接电阻、电容的大小决定。

2 电路设计方案2

方案2如图4所示。解码原理同方案1。该电路采用FIFO(IDT7201)加状态寄存器和缓冲器,实现单片机与主计算机之间的数据传输,无需8255和锁存器,器件较少,但相应地会增加软件控制的工作量。单片机解码后,在每帧数据前加上标志码,输出时、分、秒、毫秒信息,在写信号的控制下,经缓冲器送入FIFO中。主计算机查询状态寄存器,了解FIFO的状态(空、满、半满)后,读取FIFO中的数据。这里用FIFO的8位数据线。

IDT7201为先进先出双口存储器。内部RAM:512×9,设有空标志(EF)、满标志(FF)和半满标志(HF),以避免数据溢出和空读。读、写数据通过内部循环指针,无须地址信息存取数据。

IDT7201复位时,空标志(EF)置0;满标志(FF)和半满标志(HF)置1;读、写指针设到初始位置。当写信号()由高变低时,若满标志(FF)为1,则开始写循环,将数据写入RAM中,不受任何读操作的影响;当RAM半满时,HF置0;当写指针比读指针小1时,表明缓冲区已满,FF置0,禁止写操作。当读信号()由低到高时,如果EF为1,则开始读循环,数据以FIFO的方式读出;当所有数据均读出,读指针等于写指针,缓冲区已空,EF置0,禁止读操作。在缓冲区空或满时,、信号的外部变化,不影响FIFO。

四、 板内程序设计流程

在单片机内部RAM中,用可位寻址的21H、22H、23H、24H单元分别存放“秒”、“分”、“时”BCD码和帧标志等,如表1所列。

表1 时间码存放表

INT0、INTI中断处理程序如图5和图6所示。

图5 INT0中断处理程序流程图

图6 INT1中断处理程序流程图

责任编辑:gt

-

单片机

+关注

关注

6035文章

44554浏览量

634635 -

计算机

+关注

关注

19文章

7488浏览量

87849

发布评论请先 登录

相关推荐

两种典型的电池供电电路的设计方案

基于CAN总线的智能接口卡的设计

基于USB的接口卡

基于EZ-USB FX单片机的无线式数据通讯接口卡的设计

使用TDS3000B DPO测试网络接口卡

广域网接口卡/WIC

基于PCI局部总线的1553B总线接口卡设计

B码解码接口卡电路的两种设计方案的应用

B码解码接口卡电路的两种设计方案的应用

评论