数字滤波(idgital filter)是由数字乘法器、加法器和延时单元组成的一种计算方法。其功能是对输入离散信号的数字代码进行运算处理,以达到改变信号频谱的目的。数字滤波器根据频域特性可分为低通、高通、带通和带阻4个基本类型;根据时域特性可分为无限脉冲响应(infinite impulse response,IIR)滤波器和有限脉冲响应(finite impulse response,FIR)滤波器。FIR滤波器不存在稳定性和是否可实现的问题,容易做到线性相位,故在数据通信、图像处理等领域广泛应用。

目前,FIR滤波器的硬件实现有以下几种方式:一种是使用通用数字滤波器集成电路,这种电路使用简单,但是由于字长和阶数的规格较少,不易完全满足实际需要;虽然可采用多片扩展来满足要求,但会增加体积和功耗,因而在实际应用中受到限制。另一种是使用DSP芯片,DSP芯片有专用的数字信号处理函数可调用,实现FIR滤波器相对简单,但是由于程序顺序执行,速度受到限制。而且,就是同一公司不同系统的DSP芯片,其编程指令也会有所不同,开发周期较长。还有一种是使用可编程逻辑器件,如FPGA(field programmable gate array),即现场可编程门阵列,有着规整的内部逻辑块整列和丰富的连线资源,特别适合用于细粒度和高并行度结构的FIR滤波器实现,相对于串行运算主导的通用DSP芯片来说,并行性和可扩展性都更好。

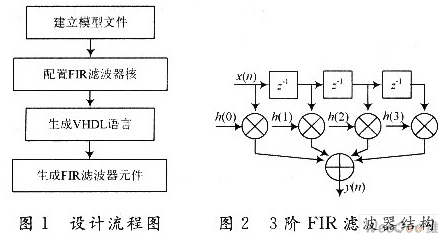

本文介绍一种基于SoPC的FIR滤波器设计方案,设计流程如图l所示。该设计方法程序简单,调试方便,得到的FIR滤波器精确度高。

1 FIR滤波器原理

FIR数字滤波器是一种非递归系统,其冲激响应总是有限长的,其系统函数可以记为:

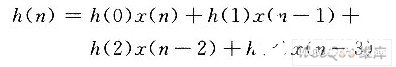

,最基本的FIR滤波器可用下式表示

输入采样序列;h(m)是滤波器系数;N是滤波器的阶数;y(n)表示滤波器的输出序列。也可以用卷积来表示输出序列y(n)与x(n),h(n)的关系:

y(n)=x(n)*h(n)

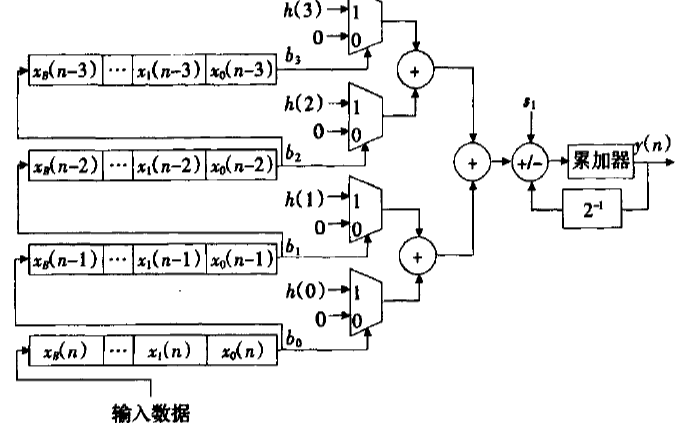

图2显示了一个典型的直接T型3阶FIR滤波器,其输出序列y(n)满足下列等式:

在该FIR滤波器中,总共存在3个延时结,4个乘法单元,1个4输入的加法器。如果采用普通的数字信号处理器(DSP)来实现,只能用串行的方式顺序地执行延时、乘加操作,不可能在1个DSP处理器指令周期内完成,必须用多个指令周期来完成。但如果采用FPGA来实现,就可以采用并行结构,在1个时钟周期内得到1个FIR滤波器的输出。不难发现,图2的电路结构是一种流水线结构,这种结构在硬件系统中有利于并行高速运行。

2 FIR滤波器的实现

Altera提供的FIR Complier是结合Altera FPGA器件的FIR Filter Core,DSP Builder与FIR Compiler可以紧密结合起来。DSP Builder提供了FIR Core的应用环境和仿真验证环境。

2.1 建立模型文件

为了调用FIR IP Core,在Simulink环境中新建模型文件,放置Sigtlal Compiler模块和FIR模块。启动Simulink的方法:打开Matlab,在主命令窗口直接键入Simulink,按回车即可。然后打开Altera DSP Builder模块,在MegaCore Functions调出fir_compiler_v7_0。

2.2 配置FIR滤波器核

双击模型中的FIR模块,在弹出来的选择窗口中有:关于这个核(about this core)、程序说明书(documentation)、显示元件(display symb01)、步骤1确定参数(Stepl:Parameterize)和步骤2生成(Step2:Generate)等4个不同的选项。点击stepl,便打开了FIR滤波器核的参数设置窗口,如图3所示。

由图3可见,滤波器的系数精度为32位,器件为CycloneⅢ,结构为并行滤波器,结构选择了1级流水线,滤波器由LC逻辑宏单元构成,系数数据存于FPGA的M9K模块中,1个输入通道,32位有符号并行输入,全精度数据输出。设定后会直接显示滤波器的频率响应(frequency res-ponse)或时域响应及系数值(timeresponse & coefficeient values)。由其频率响应图可以看出,此FIR滤波器为低通滤波器。如果不符合设计要求,则可以通过对Edit Coefficient Set选项,对滤波器进行重新配置。

2.3 生成VHDL语言

完成FIR滤波器核配置后,便可得到设计好的滤波器,加入输入/输出信号,形成如图4所示电路。点击SignalCompiler,再选择Anal-yze,选择Sigle step compilation中的Convert MDL to VHDL,就可以生成对应的VHDL语言。

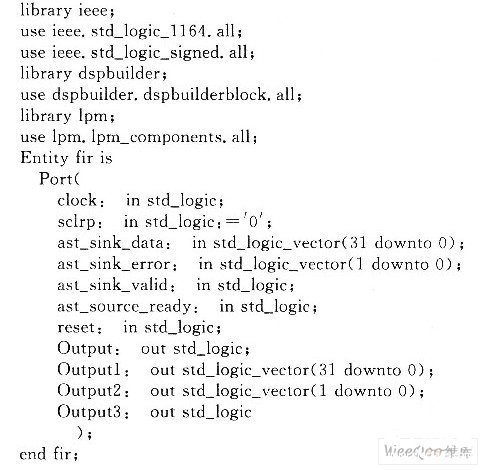

在QuartusⅡ中打开编译后生成的fir.qpf工程文件,可以得到滤波器的VHDL语言,其部分代码如下:

编译成功后,可以将其转换成元件。

2.4 系统功能仿真

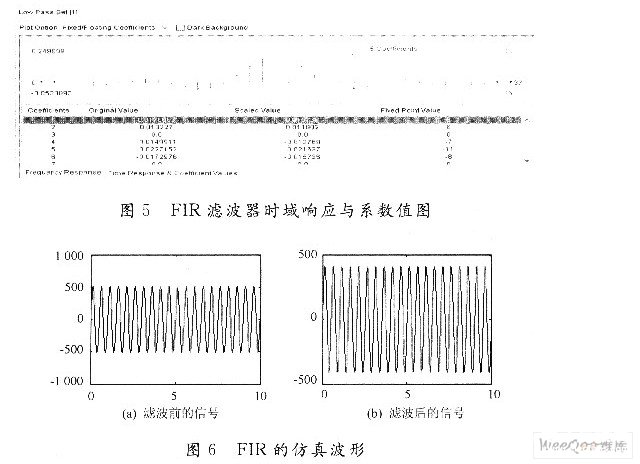

在Matlab中,建立M文件,运用前面设置好参数所生成的FIR滤波器,打开FIR滤波器时域响应与系数值(time response & coefficeient vahles)。得到该滤波器的时域响应和系数值如图5所示,由该系数表确定滤波器,并进行算法级仿真,得到如图6所示的波形。

图6(a)为滤波前信号,图6(b)为滤波后信号。从仿真波形可以看出,经过FIR滤波器之后,高次谐波信号被很好地滤除了,达到了预定的设计目标。

3 基本FPGA片上系统的功能测试

设计目标器件选用美国Altera公司Cyclone系列FPGA器件中的EP3C25E144C8N芯片,通过开发工具QuartusⅡ对各个模块的VHDL源程序及顶层电路进行编译、逻辑综合、电路的纠错、验证、自动布局布线及仿真等各种测试,最终将设计编译的数据下载到芯片中,同时与单片机AT89C51结合,进一步进行数据的快速处理和控制,实现键盘可设置参数及LCD显示。经实际电路测试验证,达到了设计的要求。

4 结语

这种基于SoPC数字滤波器的设计与实现,不仅利用Matlab中的Simulink与Alterl DSP Builder工具确定FIR滤波器系数,不用编程,只需简单的设置,而且通过VHDL层次化设计方法,同时使FPGA与单片机相结合,采用C51及VHDL语言模块化设计思想进行优化编程,进一步完善了数据的快速处理和有效控制,提高了设计的灵活性、可靠性,也增强了系统功能的可扩展性。

责任编辑:gt

-

FPGA

+关注

关注

1629文章

21744浏览量

603609 -

芯片

+关注

关注

455文章

50851浏览量

423916 -

滤波器

+关注

关注

161文章

7826浏览量

178191

发布评论请先 登录

相关推荐

基于matlab FPGA verilog的FIR滤波器设计

EP3C25E144C8N JTTA口无法正常工作

请问哪位大神有EP3C5E144A7N或者EP3C5E144C7N的FPGA开发板原理图?????跪求!!!

如何设计低通FIR滤波器

基于FPGA的FIR滤波器的性能研究

如何使用FPGA实现分布式算法的高阶FIR滤波器

基于单片机和EP3C25E144C8N芯片实现FIR滤波器的设计方案

基于单片机和EP3C25E144C8N芯片实现FIR滤波器的设计方案

评论