赛灵思一直致力于支持开源计划的不断飞跃,为帮助开发人员和研发社区充分发挥自适应计算的优势,我们再次做出了令人振奋的举措: 在 GitHub 上开放提供 Vitis HLS(高层次综合)前端(GitHub 是全球规模最大的开发平台以及构建和共享软件代码的开放社区)

Vitis HLS 工具能够将 C++ 和 OpenCL 功能部署到器件的逻辑结构和 RAM/DSP 块上。在 GitHub 上提供 Vitis HLS 前端为研究人员、开发人员和编译器爱好者开启了无限可能的新世界,使他们可以利用 Vitis HLS 技术并根据其应用的特定需求进行修改。

10 多年来,赛灵思不断改进 HLS 技术,帮助硬件开发人员提高设计生产力,并且让没有硬件设计经验的软件和应用开发人员更容易接受和利用赛灵思自适应平台。随着 Vitis HLS 前端现已在 GitHub 上全面开源,软硬件开发人员可以灵活运用标准的 Clang/LLVM 基础架构并为以下功能定制设计流程:

为 C/C++ 和 OpenCL 之外新的高级语言提供支持

添加新的特定领域优化编译指令或编译器指导

定制 LLVM IR 转换(即新的 LLVM pass)

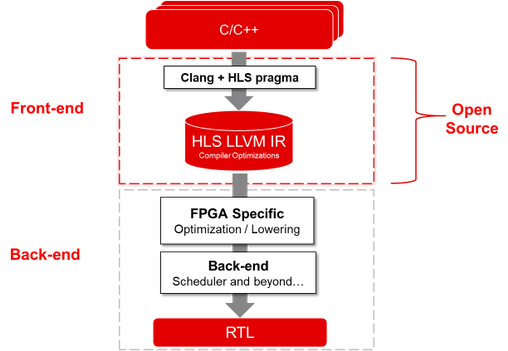

Vitis HLS 中的 C/C++ 到 RTL 综合流程包括两个主要组成部分:

[1] 前端:该部分主要解析用 C/C++ 或 OpenCL 表示的代码,使用 Clang/LLVM 工具链进行前端和中端转换。

[2] 后端:该阶段采用 LLVM IR 输入,并执行 FPGA 特定的底层映射和调度,直到最后一步,生成 RTL 。

除了支持Clang/LLVM 流程外,该项目还提供:

用于编译指示支持和硬件可综合性检查的框架

一种将固有顺序 C 代码映射到空间硬件架构的方法

通往 Vitis 统一软件平台的网关,以访问相关流程和库

我们的生态系统合作伙伴 Silexica 以及美国伊利诺伊大学厄巴纳 - 香槟分校 (UIUC)、帝国理工学院、香港科技大学的研究社区是如何利用 Vitis HLS 前端扩展功能,并助力其研究项目的呢?

“Vitis HLS 的前端开源有助于 FPGA 研究和生态系统合作伙伴社区进行扩展、定制乃至进一步优化 HLS 编译过程。赛灵思新的开源计划还为 Vitis HLS 提供了全新的‘注入使用模型’,能够注入定制的第三方代码转换,甚至使用完全定制的 Clang 编译器前端。”

通过与赛灵思密切合作,Silexica 开发了一款 SLX 插件,它可以利用新的注入使用模型扩展Vitis HLS 2020.2 代码转换。SLX 插件是一种 HLS 编译器插件,通过提供新的 Loop Interchange 指导,有助于改善 Vitis HLS 的延迟问题和吞吐量结果。这是 Silexica 计划的许多 HLS 优化指导中的第一个。该插件可作为 Vitis HLS 的纯独立插件使用,也可与 Silexica 的SLX FPGA 工具结合使用,以同时使用其深层代码分析、自动设计探索以及最佳指导识别和调优功能。

“通过 UIUC 的赛灵思自适应计算集群 (XACC) 项目合作,我们提前获得了开源软件包。利用软件包提供的接口,我们可以方便地定制并集成新的 Clang 编译指示和 LLVM pass 到 Vitis HLS 中,以实施和评估我们的研究思路。在Vitis HLS流程中利用LLVM的能力在许多方面都带来了新的可能性。此外,开源 Vitis HLS 前端还将大幅促进 HLS 开源社区的增长。我们很高兴自己能成为其中的一员。

“对我这样的 HLS 工具设计师来说,在将 LLVM IR 转换回 C 代码(包括 pragmas)时,将代码输入到 Vitis HLS中是非常困难的。新的 Vitis HLS 前端能够极大地帮助我们的工具动态和静态调度 (DASS) 集成到 HLS 流程中。例如,开源前端使我们能直接进行程序分析和转换,并将编译指示插入到 LLVM 中。”

“从我们的角度看,开发全面的 HLS 工具需要大量工程设计工作,这也是学术界与工业之间存在的差距之一。赛灵思慷慨地开放了商业 HLS 前端,它能与 Vitis HLS 结合使用,从而提供了灵活的 API 以及从解析到 IR 优化的可读源代码。它使得我们不必再处理详细的实施方案,使我们能够在实用应用场景中解决问题,并帮助我们高效地评估自己的想法。对于 HLS 社区,我们相信这个开源项目将大幅促进创新,因为它能帮助用户根据具体需求轻松定制工具。”

香港科技大学的两个开发项目利用了 Vitis HLS 前端:

项目 1:高效自动优化 Pass 阶段排序:

在该项目中,根据输入源代码的特性,开源前端中提供优化 pass 的最佳顺序将通过机器学习和启发式算法进行搜索,用于改进性能和资源消耗。

项目 2:多 FPGA HLS:

在该项目中,开源前端生成的 IR 代码将通过性能和资源模型进行分析,并自动划分为子模块,这些子模块针对与网络或 DDR 存储器互联的多个 FPGA 应用进行了优化。

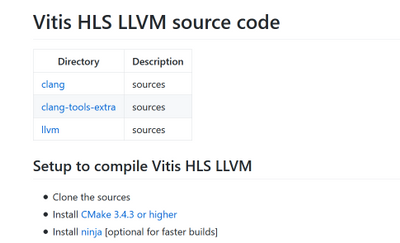

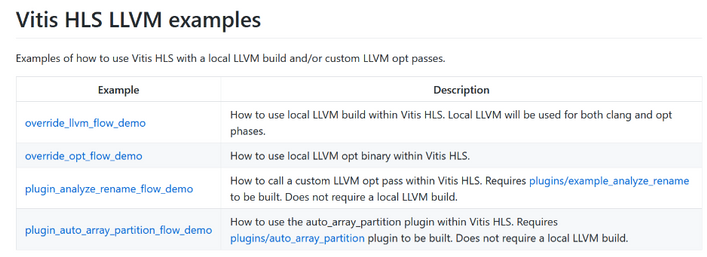

Vitis HLS 前端的源代码可在赛灵思 GitHub 库中获取。该库共享的3个示例演示了如何使用和定制流程,包括构建定制 LLVM pass 的流程。

编辑:lyn

-

赛灵思

+关注

关注

32文章

1794浏览量

131334 -

编译器

+关注

关注

1文章

1636浏览量

49172 -

硬件开发

+关注

关注

3文章

158浏览量

24213 -

HLS

+关注

关注

1文章

130浏览量

24144

原文标题:开启无限可能的世界: Vitis HLS 前端现已全面开源

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

gitee 与 GitHub 的比较

助力AIoT应用:在米尔FPGA开发板上实现Tiny YOLO V4

NVIDIA TensorRT-LLM Roadmap现已在GitHub上公开发布

Arm推出GitHub平台AI工具,简化开发者AI应用开发部署流程

优化 FPGA HLS 设计

Mistral Large 2现已在Amazon Bedrock中正式可用

在Windows 10上创建并运行AMD Vitis™视觉库示例

Mistral Large模型现已在Amazon Bedrock上正式可用

FPGA版通用图形处理架构创新解决方案

Vitis HLS前端现已在GitHub上全面开源,开启了无限可能的新世界

Vitis HLS前端现已在GitHub上全面开源,开启了无限可能的新世界

评论