探索异构平台的设计方法和概念

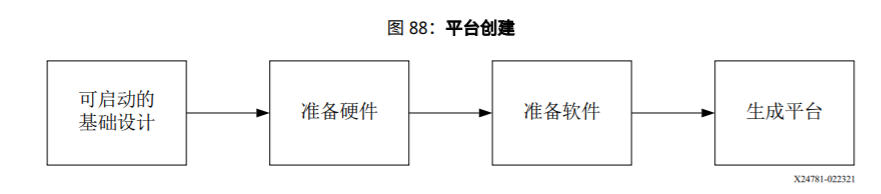

赛灵思 Versal ACAP 硬件、IP 和平台开发方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。Versal ACAP从设计之初即采用正确方法并尽早关注设计目标(包括 IP 选择和配置、块连接、RTL、时钟、I/O 接口和 PCB 管脚分配)至关重要。在每个设计阶段中正确定义和验证设计有助于减少后续实现阶段的时序收敛、性能收敛和功耗问题。

鉴于设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。本指南基于最佳时间对操作步骤进行了规范,帮助开发者以尽可能最快且最高效的方式实现期望的设计目标。

Versal ACAP支持包括Vivado IP intergrator、Vitis HLS、RTL等方式创建设计。

Vivado IP integrator 支持使用 SmartConnect IP 和 NoC 将多个 IP 连接在一起以创建块设计 (.bd) 或 IP 子系统。通过使用 IP integrator,即可将 IP 拖放到设计画布上,以单一线路连接 AXI 接口,设置端口和接口端口布局以将 IP 子 系统连接到顶层设计。这些 IP 块设计还可作为源设计加以封装 并在其它设计中复用。

本指南中详细介绍了开发者通过以上方式创建设计的基本流程和注意事项。

如何完美适配 Vitis 环境?

平台是设计的起点,Vitis 统一软件平台凭借“打破软硬件语言壁垒,提升开发效率”的优势,广受开发者青睐。本指南对如何适配 Vitis 环境提供了详细的指导。

获取基础平台源代码

同时,如果开发者希望从头开始创建自定义 Vitis 嵌入式平台,本指南亦提供了详细的指导。

编辑:lyn

-

pcb

+关注

关注

4335文章

23243浏览量

402256 -

IP

+关注

关注

5文章

1740浏览量

150427 -

RTL

+关注

关注

1文章

386浏览量

60183

原文标题:用户指南 | 探索 Versal ACAP 设计方法论

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

异构计算的概念、核心、优势、挑战及考虑因素

人工智能应用中的异构集成技术

【一文看懂】什么是异构计算?

异构集成封装类型详解

新华三发布多元异构算力平台H3C UniServer G7

汽车异构硬件平台开发如何进行静态代码分析

浅谈国产异构双核RISC-V+FPGA处理器AG32VF407的优势和应用场景

AvaotaA1全志T527开发板AMP异构计算简介

无问芯穹发布千卡规模异构芯片混训平台

迁移学习的基本概念和实现方法

鲲泰新闻|神州鲲泰创新智算之旅北京站开幕,发布全新智算架构和液冷整机柜产品应对 “多云、异构、绿色

探索异构平台的设计方法和概念

探索异构平台的设计方法和概念

评论