大侠好,阿Q来也,今天是第二次和各位见面,请各位大侠多多关照。今天给各位大侠带来一篇项目开发经验分享“基于JESD204B的LMK04821芯片项目开发”第二篇,这是本人实打实的项目开发经验,希望可以给有需要的大侠提供一些参考学习作用。

以后机会多多,慢慢分享一些项目开发以及学习方面的内容,欢迎各位大侠一起切磋交流。

204B实战应用-LMK04821代码详解(二)

一、 SPI协议

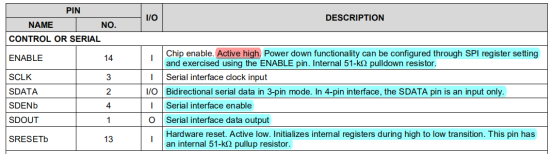

通过阅读LMK04821数据手册,我们可以从中知道,可以通过SPI协议对LMK04821进行寄存器的配置工作,进而实现我们设计所需要的功能。

SPI协议部分,咱们可以用3线,或者4线,在本次设计中,使用3线。关于SPI的时序部分,这儿就不再赘述,手册里面都有详细的描述。

图1

二、 SPI寄存器配置模块设计

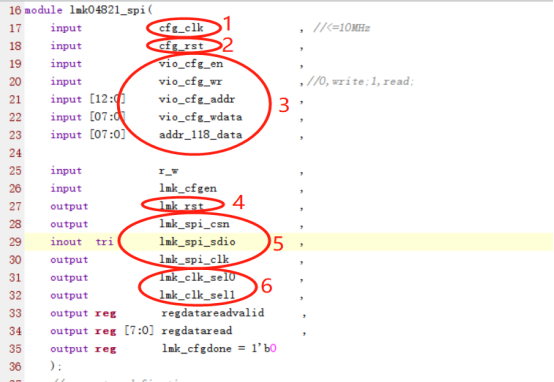

图2

如图2所示,就是配置LMK04821存器的单元,信号定义如下:

1、cfg_clk:系统时钟;

2、cfg_rst:系统复位;

3、通过VIO控制的信号,这组信号存在的目的在于方便检测自己配置寄存器的正确性。

vio_cfg_en:配置寄存器使能信号;

vio_cfg_wr:配置寄存器读写使能,0写1读;

vio_cfg_addr:配置的寄存器地址;

vio_cfg_wdata:寄存器中配置的值;

addr_118_data:预留信号,模块中没有用;

我们在配置LMK04821寄存器时,要验证配置寄存器操作是否正确,就要有写有读,在对应的寄存器内写入对应的数值,然后进行读操作,观察正确性。本次设计是在vivado环境下进行设计,通过添加VIO的IP核,来控制读写操作。同时,添加ILA配合VIO来进行读写数据操作的观测。别的开发环境下思路一样。

该组信号仅在回读寄存器时使用,目的是为了验证寄存器读写正确性。

图3

4、lmk_rst:LMK04821复位信号,用于复位LMK04821,直接和LMK04821芯片相连;

5、3线制SPI信号:

lmk_spi_csn:片选;

lmk_spi_sdio:数据;

lmk_spi_clk:时钟;

6、可编程管教:主要和LMK04821内部的PLL相关,本次设计中默认为0;

lmk_clk_sel0 :sel0;

lmk_clk_sel1 :sel1;

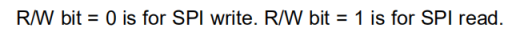

三、 SPI数据buffer定义

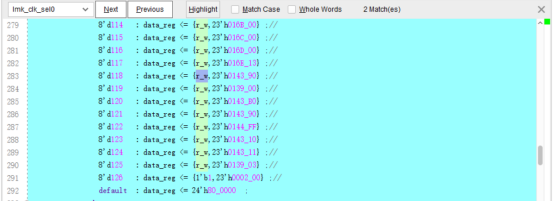

在本次设计中,SPI配置数据buffer,data_reg为24bit,r_w占1bit,箭头1所指包含W1、W2以及地址位占13bit,具体见SPI时序图;箭头2所指数据位8bit。

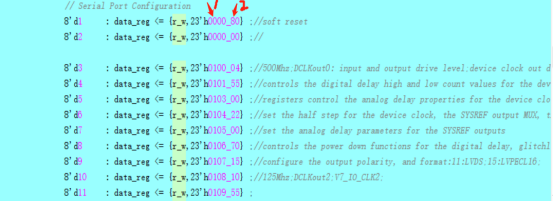

图4

根据图5我们可以知道,要配置LMK04821我们需要配置126个寄存器,这126个寄存器来源参见第一章实战记录。

其中,126个寄存器包含必须要配的寄存器、一些无关紧要的寄存器、以及功能实现所需要的寄存器等,有些寄存器需要配置多次。

图5

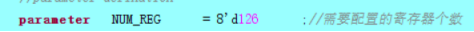

四、 SPI时序实现

设计中,我们需要按照顺序配置126个寄存器,也就是说SPI要执行126次。因此,在代码实现过程中,注意寄存器配置的顺序,并且保证每个寄存器都准确无误的配置完成,才能进行下一个寄存器的配置。如果在设计中,要求LMK004821实现不同的功能,当配置的寄存器个数不一致时,在v文件中更改图6所示的参数即可。

图6

下一篇,将详细介绍jesd_204B IP核应用的相关知识,各位大侠,尽请关注。

原文标题:FPGA项目开发:204B实战应用-LMK04821代码详解(二)

文章出处:【微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1629文章

21736浏览量

603297 -

芯片

+关注

关注

455文章

50812浏览量

423546

发布评论请先 登录

相关推荐

JESD204B使用说明

调试ADS52J90板卡JESD204B接口遇到的问题求解

在FPGA里面例化了8个jesd204B的ip核同步接收8块AFE芯片的信号,怎么连接设备时钟和sysref到AFE和FPGA?

如何配置LMK04828时钟芯片生成JESD204b需要的时钟?

LMK04821遇到的问题求解

LMK04821 SPI通信不了是怎么回事?如何解决?

LMK04821测量SPI波形异常,无法写入及读取怎么解决?

从JESD204B升级到JESD204C时的系统设计注意事项

采用JESD204B的LMK5C33216超低抖动时钟同步器数据表

带双环路PLL且符合JESD204B标准的LMK04832超低噪声时钟抖动清除器数据表

LMK0482x超低噪声JESD204B兼容时钟抖动消除器数据表

具有双环路PLL的LMK04228超低噪声且符合JESD204B标准的时钟抖动清除器数据表

LMK04714-Q1符合JESD204B/C标准的汽车级、超低噪声、双环路时钟抖动清除器数据表

基于JESD204B的LMK04821芯片项目详解

基于JESD204B的LMK04821芯片项目详解

评论