一、从结构说起:

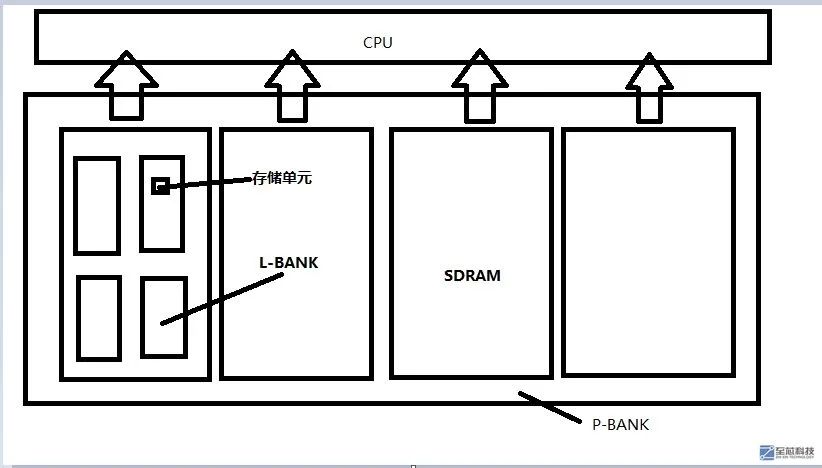

1、P-bank

SDRAM,也即我们的内存,我们的电脑,手机等设备都离不开我们的内存。一个设备运行速度的快慢,内存起到关键性的作用,就像我们的电脑,开机之后一般都是把一些应用程序加载到内存里运行,因为RAM的读写速度要远远大于ROM,而我们的SDRAM,即同步动态随机存储器,就是通过不断地刷新,充电,防止电容电量的丢失,从而保留住数据。与CPU交换数据,根据CPU位宽的不同,要相应选择不同的SDRAM芯片,SDRAM芯片的位宽不等,我们用的这片SDRAM是16位位宽,假设我们的CPU是64位的,那么我们要想与之匹配,就必须用到4片这样的SDRAM,才能构成64位的位宽,那么由这4片SDRAM 构成的芯片集合,我们称之为物理bank,即P-bank,CPU通过控制SDRAM的片选信号,控制相应的芯片

2、L-bank

再往芯片里面看,每一片SDRAM里面,有几个存储阵列,我们开发板上的都是4个存储阵列,这样的存储阵列,我们称它为逻辑bank,即L-bank。每个存储阵列里面有2^12行,2^8列,我们可以通过控制SDRAM的地址线,来选中相应的行与列,进而确定一个存储单元,每个存储单元里面就是我们的数据了,我们的芯片是16位的,所以我们的存储单元也就是16位的。

这样一来,CPU通过片选信号选中一片SDRAM,然后访问某一个L-bank,通过行列地址确定某一个存储单元,将存储单元里的数据读出来送到CPU。这样看来,芯片的位宽就是我们的存储单元的位宽,若是一同选中所有SDRAM芯片,那么输出的也就是16X4=64位的CPU位宽了。

3、芯片容量 与 内存容量

我们来算一下SDRAM的芯片容量,一片SDRAM芯片假设有4个L-bank,2^12行,2^8列,那么它就含有4 x 2^12 x 2^8个存储单元,又因为每个存储单元里面有16位数据,因此,我们的芯片容量为 4 x 2^12 x 2^8 x 16 = 64Mbit = 16MB,如果是一个P-bank里面是4片SDRAM的话,那么我们的内存容量就是4 x 16 = 64MB

我们再算一下,假如我们的SDRAM的芯片位宽是8位的但是芯片容量不变,即芯片位宽是8位,芯片容量是16MB,那么,要想与64位的CPU匹配,我们需要8片SDRAM,那么我们的内存容量就是8 x 16 = 128MB,由此可见,在芯片容量相同的情况下,位宽越小,内存容量越大。这就说明了,为什么我们的台式电脑要用位宽小的芯片,因为台式电脑空间大,位宽越小,用的芯片越多,内存也就越大,相反,我们的手机就必须用大位宽的芯片,从而节约空间,但是付出了内存容量小的代价,这也说明了为什么我们的手机或者笔记本电脑不如台式机运行速度快的原因,在内存方面差了一大截

下面是我用画图做的一个框架,帮助大家理解

二、工作原理其实不难

这部分我们就按照代码的顺序开始讲起

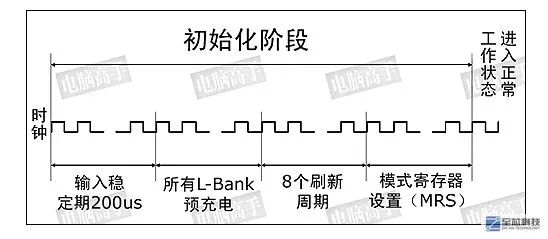

1、初始化

初始化开始,SDRAM需要经过一个200us的稳定延时,这部分在代码部分直接做一个计数器就好了,下面来讲一下预充电

预充电

官方解释是 L-Bank关闭现有工作行,准备打开新行的操作就是预充电。也就是说,我们发送了一个行地址,有发送了一个列地址,找到了相应的存储单元之后,如果我们想访问另一个地址,而这个地址不在这一行内,那么我们就需要先将这一工作行关闭,这个过程就是预充电,然而刚开始我们还没有发送行列地址,只是先做一下初始化,以后等我们要发送行列地址的时候,为了手动设置预充电麻烦,我们可以告诉SDRAM在每次寻址完之后自动进行预充电即可

自刷新

我们之所以叫DRAM,就是因为它是动态的,就是每隔一段时间进行一次刷新,确保那些没有被读写过的数据不会以为时间长导致电容漏电,从而导致数据丢失,因此,每隔一段时间要对存储单元进行一次自刷新,由于存储体中电容的数据有效保存期上限是64ms,因此,我们需要每64ms对所有的存储体进行一次刷新,又因为我们有2^12= 4096行,那么我们来算一下,每刷新一行所要的时间是64ms/4096 = 15us 也就是说,我们每15us需要发送一个自刷新命令

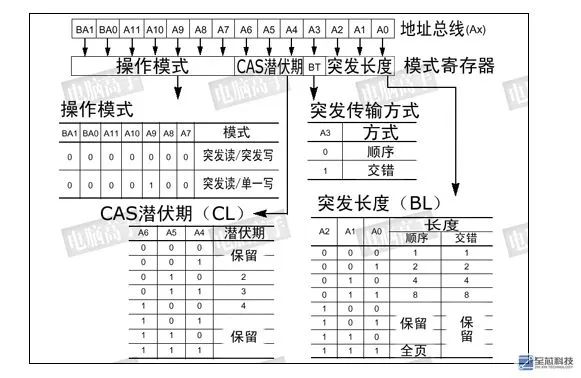

模式寄存器配置

模式寄存器的配置主要还是用于后面的读写操作的,我们先看上面,是地址总线,首先大家不要被他迷惑,我们的地址总线是12位的,行列共用,他前面的两位bank地址不属于地址总线范围,只是在配置的时候需要用到那两位,所以会将其加进来,下面来一一解释。

关于操作模式 : 操作模式可以分为突发读,突发写,单一写等,突发读就是我们在发送了行列地址后,找到了我们要的存储单元地址,对它进行读,如果设置了突发读的话,那么我们在读取第一个数据之后,如果想读取这个存储单元后面的一个存储单元的数据的话,就不必再次发送行列地址了,他会自动的读取接下来的数据,至于读几个存储单元,就涉及到突发长度,一般是2,4,8,全页的方式,全页就是将这一行上的数据一连串的全部读出或写入,同时还涉及到突发传输方式,分为顺序和交错传输,顺序传输就是依次读后面的几个存储单元,交错传输就是隔一个读一个。

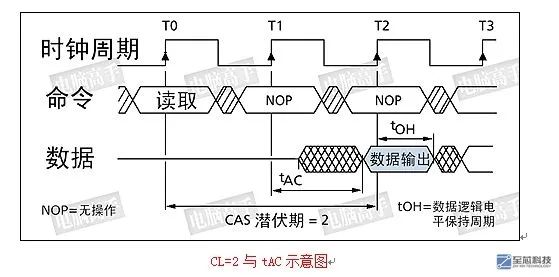

关于潜伏期 : 潜伏期就是我们发送了行列地址后,数据并不是马上到达数据总线,而是要经过一段潜伏期,一般为2到3个时钟周期,注意潜伏期不是延迟,潜伏期是发送列地址后数据已经有效,只是还没有达到一定的高度,或者说是信号不够强,要经过一定的放大才能输出,所以说潜伏期不是延迟

2、工作状态

初始化结束以后,SDRAM就可以正常工作了,这个时候,如果收到读写信号,并且收到地址,那么SDRAM就会进行相应的寻址,并将数据作相应处理。

读状态

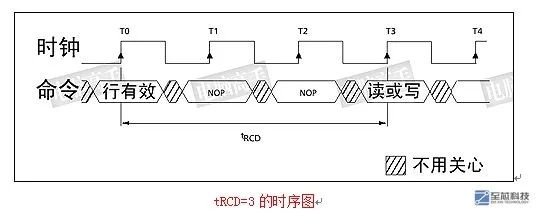

上面说了,SDRAM的地址是行列共用,也就是说行地址和列地址共用那条12位的地址线,假设某个时间我们要读一个数据,那么就先要发送12位地址线,就是行地址,当然也要接着发送的是P-bank的地址,但是这个时候还没有发送读信号,读信号要和列地址一起发送,我们称这个状态为行有效(RAS)

发送完行地址之后,就要发送列地址,但是不能马上发送,要经过一定的延时,这个延时我们叫做行有效到列有效的延时,即Trcd

经过Trcd之后,我们需要发送列地址,即列有效(CAS),这样我们就确定了我们逻辑单元所在的位置了,在发送列地址的同时,给SDRAM发送读命令。有人会问,既然地址线是行列共用,那么12位的地址线,列地址才占8位,其他的怎么用?没错,列地址是只占了8位,还有第8到11位地址线没用,这个时候我们就将其补零就好了,凑够12位地址发送给SDRAM,但是我们有一位地址很重要就是A10位,A10位置1的话,那么我们每次进行完一次读写,SDRAM就会自动预充电,因此,我们一般把地址总线的第8到11位赋值0100,然后与列地址合并,再发给SDRAM。

发送完列地址后,也就是读命令后,就要进入潜伏期Tcl,刚刚说了,数据在潜伏期里,要经过一定的放大驱动,达到一定的高度之后才会被输出,这个放大的过程是在一个叫做S-AMP的通道里完成的,每一个存储体都对应一个S-AMP通道 ,因此从数据I/O总线上有数据输出之前的一个时钟上升沿开始,数据即已传向S-AMP,也就是说此时数据已经被触发,经过一定的驱动时间最终传向数据总线进行输出,这段时间称之为tAC。

在后面的时序分析中,我们会用到这个参数,即数据在SDRAM芯片中的传输时间Tco,数据输出到SDRAM数据总线上以后会有一个保持时间Toh,也是我们以后做时序分析要用到的参数,这两个参数告诉我们,数据从有效前的一个时钟周期开始算起,最大要经过Tac时间才会输出到数据总线,最慢需要Toh时间因此,在后面的时序分析中我们要计算,数据在SDRAM芯片的传输时间 Toh 《 Tco 《 Tac

写状态

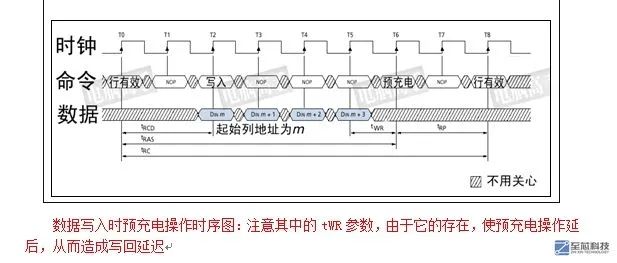

写状态跟读状态有一点不同,就是写状态没有潜伏期,即行有效之后,等待Trcd后发送写命令和列地址,数据直接会写到数据总线上,也就是说,写数据是零延时的,但是,即使写数据是零延时的,但是数据要进入SDRAM的存储体还是需要时间的,这个时间叫做写回延时Twr,试想,如果SDRAM工作在写回延时状态,突然来了一个预充电,那么数据是不是就不能正确的被写入了,因此,写回延时不能和预充电同时进行。

三、参数总结

好了,说了这么多,是不是感觉SDRAM的操作并不难,那么我们就来总结一下之前出现的一些参数吧,这些参数的消化,能够帮我们更好的理解SDRAM的工作原理

1、RAS : 行有效

2、Trcd : 行地址到列地址的延时时间,单位是周期数,一般为2到3个时钟周期

3、CAS : 列有效,同时发送读写命令

4、 Tcl : 潜伏期,发生在读状态,数据有效到出现在数据总线上的延时,单位为周期数

5、 Tac : 数据从存储单元里出来之后,已经进入S-AMP通道进行驱动与放大,到出现在数据总线上的时间

6、 Toh : 数据出现在数据总线上,并保持一段时间

7、 Trp : 在发出预充电命令之后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行

8 、Twr :写状态时的写回延时,写入的数据进入SDRAM存储单元的时间

编辑:jq

-

FPGA

+关注

关注

1664文章

22519浏览量

639738 -

SDRAM

+关注

关注

7文章

459浏览量

57875

发布评论请先 登录

零基础手写大模型资料2026

零基础玩转Linux+Ubuntu实战视频课程

2小时搞定鸿蒙应用!零基础做出你的鸿蒙“处女作”

如何评估SDRAM的有效带宽

【教程】零基础!手把手教你使用STM32F4进行E22-400T22S编程通信

零基础学习LuatOS编程:快速上手开发实战教程!

跟老齐学Python:从入门到精通

STC8H 单片机 + RA8889/RA6809:重新定义嵌入式触控交互_高流畅、低延迟、零基础的人机界面(一)

零基础学FPGA - SDRAM(理论篇)

零基础学FPGA - SDRAM(理论篇)

评论