Astro-Rail工具为芯片设计提供了在设计和签核阶段进行功耗、电压降和电迁移分析的功能。用Astro-Rail工具对一个5百万门的设计进行功耗、电压降和电迁移分析,所需时间不到一个小时。分析完成后,Astro-Rail将可能出问题的区域用不同的颜色在版图上清晰地显示出来,以帮助设计者分析并查找问题。其提供的签核分析结果和Star-RCXT反标后再分析的结果相差不到5%。Astro-Rail是Synopsys Galaxy平台的一个重要部件,利用独有的动态宏模块技术取得了突破性的速度,是一般rail分析工具速度的2倍“3倍。

文中的FFT芯片是16位的128点FFT/IFFT定点处理器,该处理器主要应用于基于OFDM的UWB系统,采用了N=4×4×4×2的算法实现定点的FFT运算。它采用了两级流水线的结构,包括三级的基-4运算和一级的基-2运算。该设计的时钟频率为62MHz,采用SMIC 0.18mm 1P5M CMOS工艺,用Astro工具完成3.7mm×3.7mm版图面积平面规划、电源环和电源条预布线,用PC工具进行基于时序和阻塞的布局,再用Astro工具完成时钟树综合和布线。在满足静态时序分析和设计规则检查的情况下,利用Astro-Rail工具对FFT芯片进行功耗分析来判断电源和地的Pad对数目是否符合要求,通过电压降和电迁移分析来判断电源环和电源条的布线是否符合电压降和电迁移要求。

Astro-Rail分析门级功耗的方法

用Astro-Rail工具分析门级功耗包含四个部分:开关功率、短路功率、内部功率和泄漏功率。

开关功率

单元门器件的输出端与地之间会形成一个电容,器件导通或关断时对该电容进行充电或放电所消耗的功率即为开关功率。Astro-Rail计算开关功率的公式为:P=C×V2×f/2。其中f为信号跳变率,即单位时间内信号在高低电平之间跳变的次数;C为门器件输出端的线负载电容,其数值可以通过线负载模型提取,也可以在物理设计完成后从版图中提取,后者具有较高的精度;V为电源电压。

短路功率

当一个单元的状态从0变为1或从1变为0时,对应的N型和P型管在短时间内同时导通,从而在单元门器件中产生从电源到地的通路,此过程中消耗的功率称为短路功率。

内部功率

对一个单元门器件来说,不是每一次输入信号状态的变化都会导致输出信号的状态改变。这种输入信号状态发生变化而输出信号状态不变的情况下所消耗的功率被称为内部功率。以二输入或门为例,当A、B输入均为1,则输出X为1,这时若输入B从1变为0,输出X状态不变,但输入B控制的管子状态发生变化,从而消耗内部功率。

泄漏功率

泄漏功率是指晶体管没有进行开关动作时所消耗的功率。尽管在晶体管漏极和衬底之间的一些反向偏置二极管中存在着漏电流,但大部分泄漏功率来自晶体管关断时的亚阈值电流。当一个设计已经确定后,其泄漏功率是恒定的,与芯片的工作状态无关。

FFT芯片的功耗分析

Astro-Rail分析FFT芯片功耗的流程主要包括5个步骤。

查看工艺库文件

在smic18_apollo_m5.tf工艺库文件中查看所定义的电压、功耗、电流等单位,通过搜索关键字maxCurrDensity寻找各金属层和各过孔的最大电流密度值。

在Milkyway环境创建LM目录

Milkyway 环境是 Synopsys 针对超深亚微米(纳米级)设计所建立的一种数据库,它大大方便了整个物理设计实现的流程。LM目录为Astro-Rail工具分析门级功耗、电压降、电迁移提供了所必需的时序信息和功耗信息。由于SMIC 0.18mm CMOS工艺在Milkyway环境中无LM目录,因此需要在Astro环境下使用gePrepLIbs命令创建LM目录。具体的方法是:在STD(标准单元库)目录下,进入Astro环境,输入gePrepLIbs命令,执行后会打开对话框,在对话框中进行相应设置即可生成STD的LM目录。用同样的方法创建标准IO的LM目录。

导入VDD网络的电压值

Astro-Rail工具用VDD的电压值来计算芯片的功耗,默认值为0V。指定VDD网络电压值的命令为:

tdfSetPowerSupply“VDD”1.621.81.98

将该命令保存在Powersupply.tdf文件,然后执行poLoadPowerSupply命令,弹出对话框输入该文件进行导入。

导入芯片的信号跳变信息

为正确分析各种单元门器件的功耗,关键是要精确计算每个单元门器件的信号跳变率。对于本文使用的0.18mm工艺而言,芯片的功耗主要取决于动态功耗,而动态功耗依赖于不同的输入向量,通常需要针对芯片各个部分设计大量的输入向量进行仿真,以记录信号跳变信息。信号跳变信息由Value Change Dump(VCD)文件记录。导入芯片的信号跳变信息时,先执行菜单命令Power>Load NetSwitching Activity,在弹出对话框的输入格式中选择VCD模式,然后输入VCD文件名后按OK按钮即可导入。

功耗计算

执行菜单命令Power>PowerAnalysis,在弹出的对话框中进行适当选择后,按OK按钮对FFT芯片进行功耗计算。结果如下 :开关功率为293.88mW,短路功率为293.991mW,内部功率为160.541mW,泄漏功率为0.1159mW,总功耗为748.527mW,总电流为Itotal=415.848mA。根据工艺库文档可知:电源和地 PAD允许通过的最大电流都为Imax=51mA,则可确定电源和地 PAD的最小对数n:

n= Itotal/Imax=415.848/51=8.15

在本文的FFT芯片中布置有12对电源和地PAD数,故符合要求。在设计中,应该多放置几对电源和地PAD,不但可以减少电压降,冗余的电源、地PAD以及键合线(Bonding Wire)都可以减少寄生电容,从而降低顺势电流变化而导致的电压波动。

FFT芯片的电压降和电迁移分析

芯片电源完整性分析包含电压降分析和电迁移效应分析。电压降分析包含计算对电源网络VDD的电压降和对地网络GND的电压反弹值。对电源网络VDD的电压降是由芯片中电源网络的金属连线电阻所造成的,导致电源和地之间电势差降低;对地网络GND的电压反弹主要是由于开关电流流经连线或衬底的电感引起,也可能由于连接电源和地的封装引线电感引起。电压降和地电压反弹都会减小逻辑门的噪声容限,增加时延。电迁移是由于金属连线中存在高密度的电流,从而在金属的正偏压端和负偏压端之间形成金属导电原子流动。这股强烈的原子流有可能导致金属的断裂(金属连线开路)或是挤出(金属连线短路)。因此,完成功耗分析后对FFT芯片进行电压降分析和电迁移分析是十分必要的。

抽取电源和地网络参数

要正确分析电压降,需要抽取电源和地网络的电阻和电容值。执行poPGExtraction命令,打开对话框,在PG net name中选择VDD按Apply按钮,再选择GND按OK按钮,即可完成电源和地网络参数抽取。

定义理想电源输入点

在分析电压降和电迁移的过程中,用poGenUserDefineTap命令自动生成用户定义的理想源输入点。具体做法是:先执行poGenUserDefineTap命令,弹出对话框,接着在FFT版图窗口左边的快捷按钮点击 Layer panel选项,在弹出的对话框中选择仅显示M1层(层号为61)。用鼠标左键点击每个VDD的PAD与VDD网络线连接处,则该点位置会自动加入vddtaps文件中,并在命令窗口显示:Writing tap (VDD 61 336.750 3514.180)into file ”vddtaps“。用同样的方法定义分析地电压反弹时所需的理想电压输入点文件gndtaps。

计算最大电压降

输入poRailAnalysis命令,弹出对话框,在P/G pad info中选择用户定义的Tap,在用户定义的Tap文件中输入文件名vddtaps,选中Extract Option选项分析电压降。从分析结果中可知,最大的电压降为70.726mV,小于0.1VDD即180mV,证明FFT芯片电源环和电源条的布置符合电压降的要求。

计算最大地电压反弹,只需在用户定义的Tap文件中输入文件名gndtaps,选中Extract Option选项即可分析地网络。从分析结果中可知,最大地电压反弹为46.419mV,小于0.1VDD即180mV,证明FFT芯片电源环和电源条的布置符合地反弹电压要求。

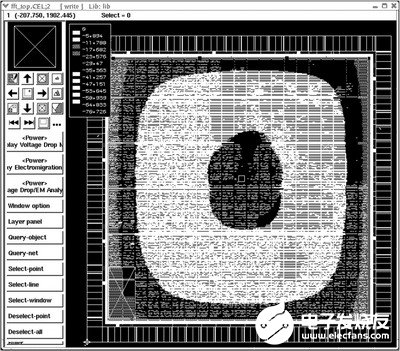

显示电压降图

当轨道分析完成后,可用不同颜色来显示芯片FFT不同部位的电压降情况。具体做法为:执行菜单命令Power>Display Voltage Drop Map…,弹出对话框,在PG Net中选择分析VDD,按Apply按钮后自动指定最大的电压降值-70.726mV。对最大的电压降值-70.726mV进行12等分,并选择将每一等分范围及对应的颜色配置显示在FFT芯片版图上,按OK按钮后得电压降图,如图1所示。从图中可知,中间呈蛋形的区域对应的电压降大,该区域中的高亮小矩形表示此处的VDD网络电压降最大。地电平反弹图可用同样的方法分析。

图1 FFT芯片电压降图

显示电迁移图

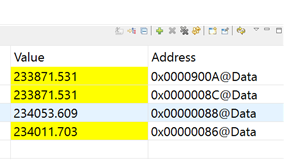

电迁移图可用不同颜色来显示芯片各层及过孔在芯片FFT不同部位的电流密度情况。显示电迁移图的具体方法是:执行Power> Display Electromigration Map…菜单命令,弹出对话框,在PG Net中选择分析VDD,然后点击Color,Metal,Via Bounds按钮,打开如图2所示的对话框。对话框中各金属层和过孔所允许的最大电流密度按smic18_apollo_m5.tf工艺库文件中的指定自动填入。可根据实际情况修改各金属层和过孔所允许的最大电流密度。

选择图2中的M1金属层,并按OK按钮进行分析,得到M1层电迁移图,如图3所示,可在FFT芯片版图上用12种不同颜色来显示不同部位的电流密度情况。从图中可知,M1层中电迁移率较大区域的参数值范围为6.667”7.5,小于M1层所允许的最大电流密度10。用同样方法可分析其它金属层和过孔的电迁移图,从图中可判断出,各金属层和过孔的电迁移率都小于所允许的最大电流密度,从而证明FFT芯片电源环和电源条的布置符合电迁移要求。

图2 金属层和过孔允许最大电流密度

图3 FFT芯片M1层电迁移率图

结语

随着集成电路制造技术的不断提高,集成度越来越高,对应的功耗、电压降和电迁移问题也越来越突出。减小芯片功耗的方法与设计有关;解决电压降的主要方法是增加电源线和地线的宽度及数量,合理布置电源网络;解决电迁移问题的主要方法是增加电源和地PAD对的数量,增加电源线和地线的宽度及数量,对关键路径设置较宽的连线。通过利用Astro-Rail工具对电源和地网络进行参数提取,再进行功耗、电压降和地反弹电压计算,并显示电压降和电迁移分析的结果,能够确保芯片中与功耗相关的电源和地PAD对数,与电源环和电源条布局布线相关的电压降、地电压反弹和电迁移效应等问题得到解决。

责任编辑:gt

-

电源

+关注

关注

185文章

17892浏览量

252369 -

处理器

+关注

关注

68文章

19485浏览量

231518 -

晶体管

+关注

关注

77文章

9811浏览量

139164

发布评论请先 登录

相关推荐

浮点处理器相对于定点处理器有何不同

基于FPGA的FFT和IFFT IP核应用实例

玩转Zynq连载48——[ex67] Vivado FFT和IFFT IP核应用实例

FFT和IFFT的Matlab实现

FFT和IFFT的Matlab实现

基于FPGA的FFT处理器的研究与设计

高速定点FFT处理器的设计与实现

基于128点FFT/IFFT定点处理器解决电压降和电迁移问题

基于128点FFT/IFFT定点处理器解决电压降和电迁移问题

评论