1 引 言

频移键控(FSK)是利用数字基带信号控制载波的频率来传送信息的一种方式。“1”码用频率f1传输,“0”码用频率f2传输。FSK信号又可分为2种,一种叫离散相位FSK信号,记作DPFSK,这种信号的波形在基带信号“0”,“1”交替时,载波相位不连续;另一种叫相位连续FSK信号,记作CPFSK,他在码元“0”,“1”交替时相位连续。CPFSK信号由于其相位的连续性,不仅具有实现容易、适用频带宽、抗干扰能力强、解调无需相干载波等优点,而且避免了DPFSK信号由于在频率转换点上的相位不连续,而使功率谱产生很大的旁瓣分量,带限后会引起包络起伏的缺点,因此在数字通信领域有着广泛应用。

在实际应用中CPFSK信号的实现有许多种途径,例如采用频率切换技术、动态改变谐振电路LC组件参数或者直接采用调制芯片如DDS等。如何在满足系统功能的前提下,以较少的硬件成本完成CPFSK信号调制,具有广泛的应用价值。本文介绍在我国磁悬浮列车车地通信系统中应用的一种CPFSK中频调制器,其核心是基于锁相环路的CPFSK信号调制技术。系统要求中频频率为280 MHz,在信道带宽25 MHz以内,对前级编译码板提供的码率为10.24 Mb∕s的数据和周期为1 ms,脉宽10~12μs的报头脉冲信号实现调制后送至后级的38 GHz毫米波前端。

2 设计思路及系统仿真

CPFSK的基本数学原理就是用数字基带信号去控制频率的切换,完成对载频信号的调制,并保持相位的连续性,从而实现数字信息的传输。在一个码元时间Ts内,CPFSK信号可表示为:

当θ(t)为时间的连续函数时,已调波在所有时间上是连续的。若传0码时载频为ω1,传1码时载频为ω2,他们相对于未调载频ω0的频偏为△ω,上式又可写为:

式中的θ(0)为初相角,取决于过去码元的调制的结果,他的选择要防止相位的任何不连续性。对于CPFSK信号有,βf称为调制指数。

传统CPFSK信号的实现途径包括以下3种方式:

频率转换 采用数字基带信号控制两个独立的振荡器,通过加法器叠加实现CPFSK调制。该方式采用了部分数字电路,精度较高,但由于两个边频采用独立的高频振荡器生成,在频域引入了大量的谐波成分,无法满足相位连续的调制。

直接调频 采用数字基带信号直接控制LC振荡回路的参数改变,实现CPFSK调制。该方式实现容易,相位连续,但采用了大量的仿真电路组件,频率精度和稳定性无法保证。

调制解调芯片 采用成熟的调制解调芯片实现。该方式采用了当前通信电子技术发展的最新成果,直接利用现成硬件加以实现CPFSK调制、精度高、频率稳定性好,但由于调制解调芯片普遍遵循了相应的CCITT通信协议标准,只能实现特定载频、特定调制频率上的CPFSK调制,并且硬件成本较高,无法满足专用领域的应用。

综上所述,该CPFSK调制器采用基于锁相环路(PLL)方式的CPFSK调制,其原理与仿真调制相同,一方面可以保证相位的连续性,另一方面利用PLL的稳频特性可以保证较高的频率的稳定度,并且实现方法简便。

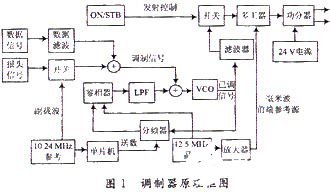

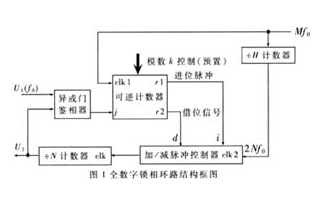

调制器原理框图如图1所示。

其中数据信号为10.24 MHz曼彻斯特编码信号,为了限制中频带宽并减小数据信号的码间串扰,在数据滤波部分采用升余弦滤波器,其频率特性为:

升余弦特性所形成的基带波形h(t),除了在本码元抽样时刻上不为零外,在其它码元的抽样点上均为零值,满足无码间干扰的时域条件。不仅如此,他在两个抽样点之间还有一个零点,并且他的“尾巴”收敛快,因此这样的波形对于减小码间干扰及定时提取都十分有利。

用报头信号作为开关的控制信号,实现对10.24 MHz的副载波(来自于前级的数据基带板的参考输出,以便与数据有同步关系)进行幅度键控(ASK),将键控输出与数据信号合成后送到VCO调谐端。选用10.24 MHz这个频率做副载波,从频谱上看10.24 MHz恰好为数据信号频谱的一个零点,这样可以有效避免报头和数据信号的互相干扰,利于解调。此外10.24 MHz还作为单片机的外接参考。

合成的调制信号加到VCO的调谐端,对于锁在一个点频上的锁相环而言,调制信号可认为是一种干扰,因此PLL的环路滤波器必须抑制掉调制信号对载频的干扰。从锁相环误差传递函数的角度来分析,由于锁相环的误差传递函数He(jω)具有高通特性,因此必须设计合适的环路滤波器,让调制信号的最低频率ωm处于锁相环误差传递函数的通带以内,从而实现频率调制。这种方案在调制频率ωm很低,进人He(jω)的阻带之后,调制频偏是很小的,这是这类方案的一个显著的缺点。但由于送入该调制器的数据信号为10.24 Mb∕s的曼彻斯特编码信号,调制频率下限不可能很低,从而避免了上述缺点的影响。

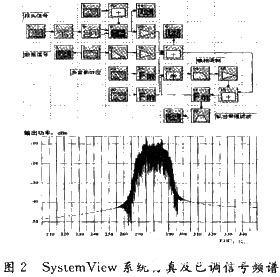

图2是用SystemView对整个调制器进行系统仿真的框图和得到的已调信号的频谱。

3 实际电路

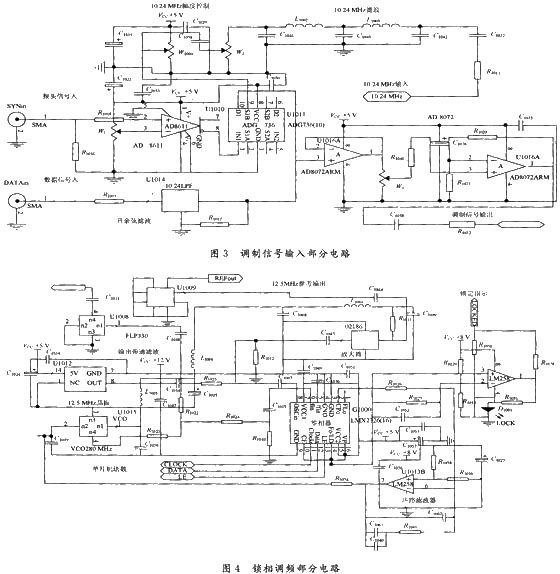

调制信号输入部分如图3所示,报头信号输入经比较器AD8611整形后作为开关ADG736的控制信号,电位器W1用于调节比较器的参考电压,以适应不同幅度的报头输入。编译码送来的10.24 MHz数据信号经过低通滤波并由电位器W2控制幅度后送入ADG736。ASK输出和经升余弦滤波后的数据信号一起送到放大器AD8072放大后送至VCO的调谐端,电位器W3用于控制合成信号的幅度,从而控制调制器的调制度,使已调信号带宽控制在系统要求的25 MHz以内。

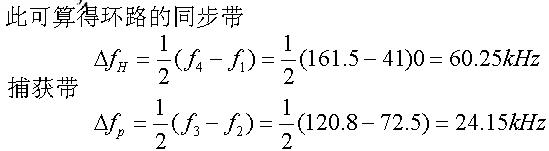

锁相环部分如图4所示,经过前面的分析,锁相环的环路滤波器带宽应低于调制信号的最低频率。

由于磁悬浮列车行进过程中的振动可能会引起输出频率的抖动,因此环路带宽又必须足够宽使锁定时间足够快。综合上述考虑,环路带宽设计成50 kHz左右,鉴相频率由单片机过程控制可选500 kHz,625 kHz,1 250 kHz,2 500 kHz四种,以便通过调试过程得出一个最优值。鉴相器芯片选取带Charge Pump的LMX2316,其为32∕33双模预分频,外接晶振5~100 MHz,最大鉴相频率10 MHz,射频输入工作频率0.1~2.8 GHz。由于ChargePump电流较小因此环路滤波器采用有源滤波器标准反馈结构(standard feedback approach)以获取较低的杂散。使用NSC的“WEBBECH”工具,可以方便快捷地完成锁相环的设计和仿真。此外12.5 MHz的晶振输出经放大器SNA586放大后送至多任务器,为后级的毫米波前端提供参考信号。系统提供的发射控制信号用于实现各发射站间的信号切换,以避免越站干扰。

最终完成的实际电路如图5所示。调制器中频为280 MHz,已调信号带宽25 MHz(可调),最大数据速率可达15 Mb∕s(死循环误码率10-9)。目前该中频调制器已在磁浮试验线车地通信系统的地面基站和车载移动站中投入使用,性能良好。

责任编辑:gt

-

锁相环

+关注

关注

36文章

637浏览量

91316 -

调制器

+关注

关注

3文章

978浏览量

48782

发布评论请先 登录

高频锁相环路LMX2430电子资料

锁相环路是什么?有何特点

用锁相环路实现任意频率变换技术

基于FPGA的全数字锁相环路的设计

锁相环路跟踪特性的测量方法

锁相环在调制和解调中的应用及概念解析

采用Spartan2系列FPGA器件实现全数字锁相环路的设计和仿真验证

锁相环路的工作原理

基于锁相环路实现CPFSK中频调制器的设计方案

基于锁相环路实现CPFSK中频调制器的设计方案

评论