将先进的计算技术、半导体技术和电子技术与各个行业的具体应用以及与Intemet技术相结合己经成为未来嵌入式系统的发展趋势。这里以A19lRM9200微处理器为CPU,ATmegal28系列单片机,8 MB的Flash和32 MB的SDRAM存储器,扩展了以太网接口、串行接口等外围通信设备以及输入输出接口,根据处理器和其他接口芯片的要求设计了外围硬件电路及软件。实现了用电机控制系统实时监控多路电机的状态,并且可以控制任一路电机的转速与相位,解决了单片机与ARM系列处理器之间的通信。

1 系统硬件设计

1.1 主机硬件系统结构

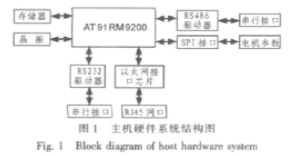

主机硬件系统结构如图1所示。

1)电源电路 AT9lRM9200需要1.8 V和3.3 V电源,另外,大部分外围器件需要3.3 V电源,小部分外围器件还需要5 V电源。此处选用了Sipex公司生产的SPXlll7M3-3.3型低压差(LDO)稳压器和SPXlll7M3-1.8型低压差(LDO)稳压器进行DC-DC变换后为各个器件提供工作电压。

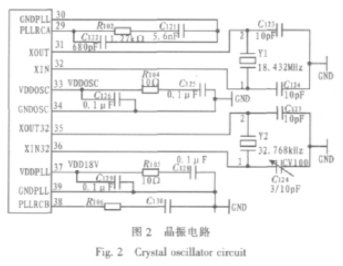

2)晶振电路 如图2所示,晶体振荡电路用于向AT91RM9200和其他需要时钟的外设电路提供工作时钟。本系统使用无源晶体振荡器X1(18. 432 MHz)和X2(32.768 kHz)作为系统的主振荡器和慢时钟振荡器,其中32.768 kHz晶振为系统提供慢时钟,18 MHz晶振通过倍频为系统提供180 MHz的主机时钟。

3)AT91RM9200处理器 ATglRM9200是Atmel公司基于ARM920T核的高性能、低功耗16/32位RISC微处理器,其最高主频为180 MHz,其双向、32位外部数据总线支持8、16、32位数据宽度,26位地址总线可以对最大64 MB空间寻址。是系统的工作和控制中心。

4)存储器 存储器模块包括Flash存储器和SRAM存储器2部分。Flash存储器用于存放引导程序、嵌入式操作系统、用户应用程序及重要的数据等,即使掉电程序和数据都不会丢失。设计中采用Intel公司生产的28F640J3A,其存储容量为64 Mb(8 MB),工作电压为2.7~3.6 V,采用48引脚TSOP封装,16位数据宽度。

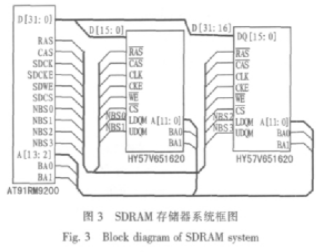

SDRAM存储器是系统代码的运行场所,存放系统运行时的程序和数据,但掉电后该部分程序和数据会丢失。设计中使用2片数据宽度为16位的SDRAM并行运行作为1个32位数据宽度的SDRAM模块,如图3所示。

使用的SDRAM电路为Hynix公司的HY57V651620BTC,其工作电压为3.3 V,单片存储容量为4组x16 Mb,54引脚TSOP封装,兼容LVTTL电平接口,支持自动刷新和自刷新。

5)网络端口 采用DAVICOM公司的DM9161作为以太网的物理层接口。通过这个接口可以控制和配置很多物理层设备,得到状态和错误信息,并且确定PHY设备的工作方式和功能。将DM9161的REF_CLK端接至50 MHz晶振的输出端;DM9161的TXD1,TXD2,TXEN,RXD1,BXD2端接至AT9lRM9200的ETXO,ETXI,ETXEN,ERXO,ERXI;DM9161的EXESEN,COL,PWRDWN端分别通过10 kΩ电阻接高电平,BGRESG,BGRES之间接6.8 kΩ电阻;将DM9161的RXEXDV,RXER,RESET,MDC,MDIO端接至AT9lRM9200的ECRS,ERXER,NRST,EMDIO均连接发光二极管,DM9161的TX+,TX-,RX+,EMDC,FDX,SPEED,LINKRX连接网络隔离变压器。

6)串行接口 用于AT9lRM9200系统短距离双向串行通信。使用的电平转换电路为Sipex公司双产的SP3232E。本系统包含1个UART接口,它是两线调试串口,用来连接到超级终端观察AT91RM9200的启动,完成与PC的通信调试。其原理图如图4所示。

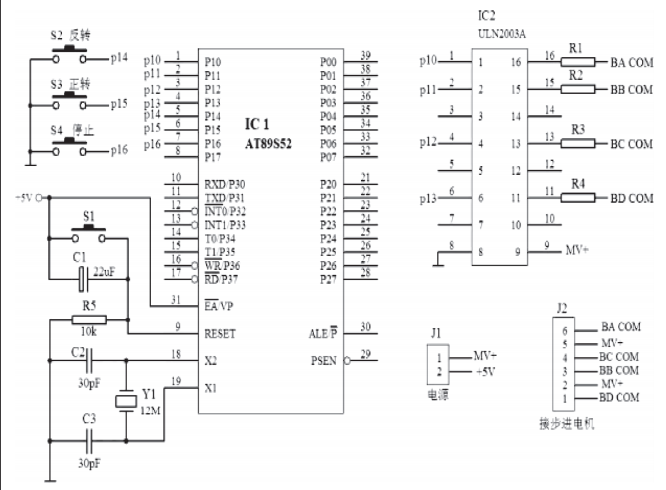

1.2 从机硬件设计

1)ATmega128单片机 ATMEL公司的AVR单片机是增强型RISC内载Flash的单片机,128 K字节的系统内可编程Flash(在写入过程中还具有读取能力,即RWW)、4 K字节的EEPROM、4 K字节的SRAM、53个通用I/O口线、32个通用工作寄存器、实时时钟RTC、4个灵活的具有比较模式和PWM功能的定时器/计数器(T/C)、2个USART、面向字节的两线接口TWI、8通道10位ADC(具有可选的可编程增益)、具有片内振荡器的可编程看门狗定时器、SPI串行端口、与IEEEll49.1规范兼容的JTAG测试接口,以及6种可以通过软件选择的省电模式。

2)系统控制和复位 复位时所有的I/O寄存器都被设置为初始值,程序从复位向量处开始执行。复位向量处的指令必须是绝对跳转JMP指令,以使程序跳转到复位处理例程。如果程序永远不会使能中断,则中断向量可以由一般的程序代码所覆盖。

图5为复位逻辑的电路图。复位源生效时I/O端口立即复位为初始值,不需要任何时钟的辅助。当所有的复位信号消失之后,延迟计数器被激活,从而延长了内部复位,并使得在MCU正常工作之前电源达到稳定的电平。延迟计数器的溢出时间通过熔丝位CKSEL由用户设定。

3)I/O端口 作为通用数字I/O使用时,所有AVRI/O端口都具有真正的读-修改-写功能。输出缓冲器具有对称的驱动能力,可以输出或吸收大电流,直接驱动LED。

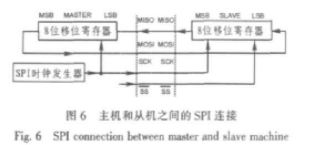

4)SPI串行外设接口 串行外设接口SPI允许ATmegal28和外设之间进行高速的同步数据传输。主机和从机之间的SPI连接如图6所示。

5)16位定时器/计时器 16位的T/C可以实现精确的程序定时、波形产生和信号测量。T/Cl、T/C3的普通模式、CTC模式、快速PWM模式、相位修正PWM模式与T/C0、T/C2相同。

2 系统软件设计

嵌入式电机控制系统在软件设计上分为主机软件设计与从机软件设计。主机软件设计主要分为主机的SPI驱动程序和主机通信程序。

从程序结构角度而言,设备驱动程序是一组由内核中的相关子例程和数据组成的I/O设备软件接口,它的任务就是向系统提供接口函数。因此每种文件系统或设备都有自己的接口函数,这个函数就是一个fileoperations数据结构,结构中的成份几乎全是函数指针。当内核需要对某个设备进行特殊的操作时,它就调用相应的接口函数即驱动例程。这就使得控制从用户进程转移到了驱动例程,当驱动例程完成控制又返回至用户进程。用户态的程序使用内核提供的标准系统调用来与内核通讯,当每个系统调用被使用时,内核就转到相应的设备驱动例程来操纵。

调用基本接口函数都需要驱动程序的fileoperations结构成员指向open(),read(),write(),release()等函数,实现了xxx_fops结构体内的各个入口点函数后,编写设备驱动程序初始化函数,并在内核启动时注册此函数,完成硬件设备的初始化设置。初始化程序片断如下:

voidinitexxxdevice(viod){

/检查硬件设备是否存在,如果存在进行硬件设备内部寄存器初始化

if(result=registerchrdev(254,“xxxdevice”,&xxxefops))

printk(“Error:%dinitxxx_device()can‘tgetMajorln”,result);

}

设备初始化函数中调用函数registerchrdev()来完成注册字符,函数形式如下:

intregisterchrdev(unsignedintmajor,constchar*name,structfileoperations*fop);

fops是指向实现的fileoperations结构体的操作指针。根据这些参数,采用如下命令,在/dev下创建该设备文件名。

mknod/dev/xxxdevicec2540。

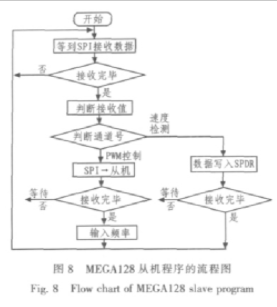

主机通信程序流程如图7所示。MEGAl28从机程序的流程图如图8所示。

3 结束语

该系统设计是对嵌入式技术与理论的拓展和应用,是对NETCON网络化控制系统的升级与改进,实现了对电机控制系统实时监控多路电机的状态,并且可以控制任一路电机的转速与相位。实现了单片机与ARM系列处理器之间的通信,解决了利用ARM处理器实现电机控制CPU工作效率低的问题。该方案经过测试应用效果良好,大大提高了CPU的工作效率。但电机的测速精度还有待进一步提高,PWM调速范围有待进一步加大,还需进一步优化程序,提高整个系统的实时性。

责任编辑:gt

-

处理器

+关注

关注

68文章

19083浏览量

228729 -

单片机

+关注

关注

6030文章

44482浏览量

631751 -

微处理器

+关注

关注

11文章

2242浏览量

82248

发布评论请先 登录

相关推荐

微处理器、单片机的概述和对比

微处理器与单片机的概述和对比

单片机、微控制器和微处理器有何区别?

基于微处理器的嵌入式直流伺服电机控制系统

如何使用51单片机进行步进电机控制系统的设计与实现

微处理器MPU和单片机MCU的区别

选微处理器MPU,还是单片机MCU?两者区别详解

选微处理器MPU,还是单片机MCU?

基于单片机的步进电机控制系统设计与实现

基于A19lRM9200微处理器和单片机实现电机控制系统的设计

基于A19lRM9200微处理器和单片机实现电机控制系统的设计

评论